Потехин / ЛР1

.docМИНИСТЕРСТВО ОБРАЗОВАНИЯ РФ

Томский государственный университет систем управления и радиоэлектроники (ТУСУР)

ЛАБОРАТОРНАЯ РАБОТА №1

по курсу ЦИФРОВЫЕ УСТРОЙСТВА И МИКРОПРОЦЕССОРЫ

В.А.Потехин

Выполнил:

Попов

Сергей

Сергеевич

код – bgø22PSS

пароль – 13172849

Сергиев Посад 2004

СЧЁТЧИК И ДЕШИФРАТОР

ЦЕЛЬ: ознакомление с принципом работы счётчика и дешифратора и правилами построения делителей частоты.

ПЛАН РАБОТЫ:

-

Собрать схему суммирующего счётчика. Зарисовать осциллограмму напряжений на управляющих выводах счётчика, на всех его выходах и на любых трёх соседних выводах дешифратора от 0 до 9.

-

Повторить предыдущий пункт для вычитающего счётчика.

-

Собрать схему программируемого делителя на базе суммирующего счётчика с использованием дешифратора и дополнительных ЛЭ. Коэффициент деления на выходах D1, D2, D3, D4 задавать равным последней цифре индивидуального номера. Зарисовать осциллограмму напряжений на выводах устройства.

-

Собрать схему программируемого делителя на базе вычитающего счётчика. Загрузку счётчика осуществлять выходным сигналом счётчика «меньше или равно 0». Коэффициент деления выбирается равным 9 минус последняя цифра индивидуального номера.

-

Составить отчёт.

1.Собираем схему суммирующего счётчика . Схема приведена в прикреплённом файле СХЕМА СУММИРУЮЩЕГО СЧЁТЧИКА Файл “СА4”.Файл открывается с помощью программы EWB_4.1

Рисунок 1-Функциональная схема суммирующего счётчика

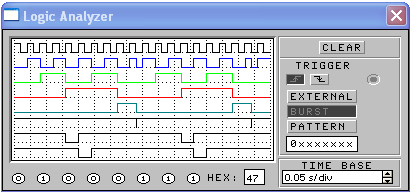

Рисунок 1- ОСЦИЛЛОГРАММЫ НАПРЯЖЕНИЙ СУММИРУЮЩЕГО СЧЁТЧИКА

В начальный период времени на выходах счётчика QA,QB, QC,QD находятся низкие уровни напряжения на переносе <9(CO)высокий уровень т.к.0 меньше 9. На нулевом выводе дешифратора низкий уровень т.к. на всех входах дешифратора логические 0. На входах 1и2 других высокий уровень .При переходе генератора с низкого уровня на высокий на выходе QAна младшем разряде появляется лог 1 на остальных QB,QC,QD логические 0.Эта комбинация соответствует 1 и на дешифраторе на 1м выходе появляется логическая 1 а на остальных лог.0 и.т.д. Когда счёт доходит до 9 при этом на выходе QA,QD-высокие уровни а на QB,QC-низкие уровни .При этом выполняется условие 9 меньше или равно 9 то возникает прерывание на выходе <9(CO) длительностью ½ периода тактового генератора по окончании которого на выходах QA,QB,QC,QD-возникают логические нули а на нулевом выходе дешифратора появляются лог.0 и процесс повторяется.

2.Собираем схему вычитающего счётчика . Схема приведена в прикреплённом файле СХЕМА ВЫЧИТАЮЩЕГО СЧЁТЧИКА Файл “СА4”.Файл открывается с помощью программы EWB_4.1

Рисунок 2-Функциональная схема вычитающего счётчика

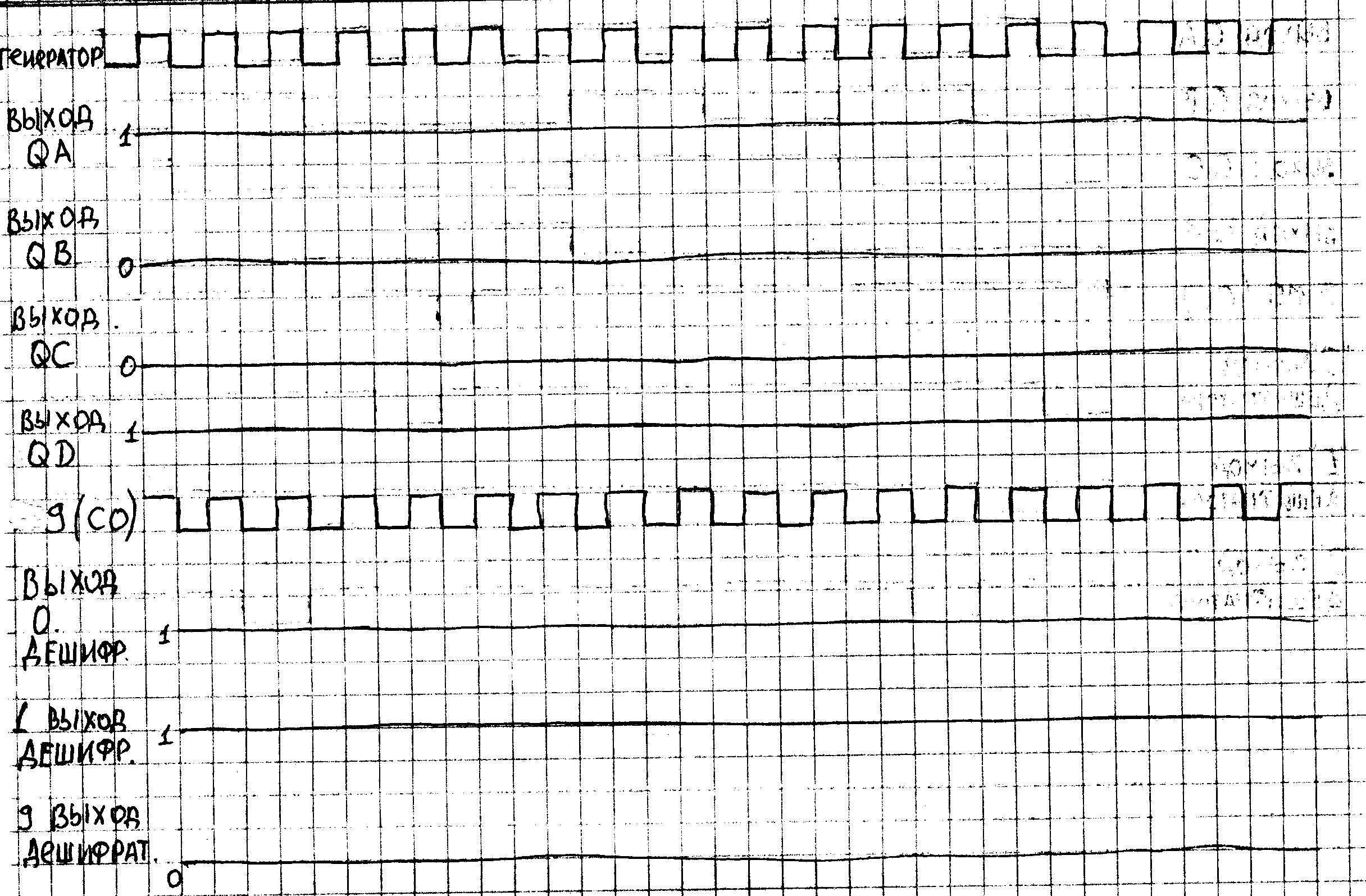

Рисунок 2- ОСЦИЛЛОГРАММЫ НАПРЯЖЕНИЙ ВЫЧИТАЮЩЕГО СЧЁТЧИКА

Работа устройства аналогична предыдущему отличие заключается только в том что счёт ведётся не от нуля до 9 а с 9 до 0. При переходе от 0 к 9 возникает прерывание на выводе <0 (ВO)

Сигнал от тактового генератора подаётся на вход DOWN а сигнал переноса снимается с вывода ВО

3.Собираем схему программируемого делителя на базе суммирующего счётчика . Схема приведена в прикреплённом файле СХЕМА СУММИРУЮЩЕГО СЧЁТЧИКА КОЭФФ. ДЕЛЕННИЯ 9.СА4 .Файл “СА4”.Файл открывается с помощью программы EWB_4.1 Коэффициент деления на входах D1,D2,D3,D4 задаём равным 9 (1001) .При этом значение на всех выходах QA,QB,QC,QD будут 1001 соответственно ,а на выходе >9(LOAD) будут прямоугольные импульсы той же частоты амплитуды и фазы что и на задающем генераторе .Девятый выход дешифратора будет постоянно под низким потенциалом .

Рисунок 3- Функциональная схема счётчика с коэффициентом деления 9

Рисунок 3- осциллограммы программируемого делителя на базе суммирующего счётчика

4. Собираем схему программируемого делителя на базе вычитающего счётчика .Коэффициент деления равен 9-9=0 поэтому выбираем произвольно 9-3=6.Вводим в счётчик D1,D2,D3,D4 число 6 (0110) чтобы получить коэффициент деления 6

Рисунок 4-Функциональная схема программируемого делителя на базе вычитающего счётчика

Рисунок 4- осциллограммы программируемого делителя на базе вычитающего счётчика

ВЫВОД : в данной работе собраны делители частоты на базе счётчиков . Если на их входа D1,D2,D3,D4 суммирующего счётчика подать двоичное число N<9 то до появления прерывания на выходе >9 следует подать 9-N импульсов . Коэффициент деления будет равен 9-N. Для вычитающего счётчика для получения прерывания на выходе <0 и при подаче на входы D1,D2,D3,D4 двоичного числа N необходимо задающему генератору сгенерировать N прямоугольных импульсов, коэффициент деления в данном случае тогда будет равен N.