Потехин / АЛУ. Отчет

.docxМинистерство образования и науки Российской Федерации

Федеральное государственное бюджетное образовательное учреждение высшего профессионального образования

ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕТРОНИКИ (ТУСУР)

Кафедра телевидения и управления (ТУ)

Отчет по лабораторной работе

по дисциплине «Вычислительная техника»

АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО (АЛУ)

|

|

Проверил ________Потехин В.А.

Выполнили ст. гр. 152 _______Долгирев В.О. _______Ни М.С. |

2014 г.

Введение

Целью цикла лабораторных работ является ознакомление с типовыми узлами ЭВМ и микропроцессоров, получение навыков проверки субблоков, изготавливаемых с использованием микросхем средней и малой степени интеграции. Все используемые микросхемы относятся к классу транзисторно-транзисторной логики (ТТЛ).

В данной лабораторной работе исследуется микросхема АЛУ (К155ИП3)

Арифметико-логические устройства (АЛУ)

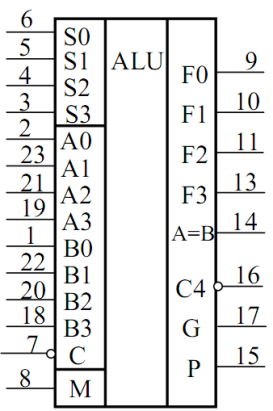

Арифметико-логические устройства (АЛУ) – это специализированные микросхемы, выполняющие в соответствии с программой на входах арифметические или логические преобразования двоичной информации (рисунок 1). В микропроцессорной технике АЛУ являются базовыми элементами – они используются в сочетании с регистрами памяти и сдвига, оперативными запоминающими устройствами и другими цифровыми узлами. АЛУ, принадлежащие к разным типам логик (ТТЛ, ТТЛШ, КМОП, ЭСТЛ), функционально во многом совпадают, в том числе и по разводке выводов.

Рисунок 1 – Условное обозначение К155ИП3

Микросхема К555ИП3 предназначена для действий с двумя четырехразрядными двоичными слоями: А = А3А2А1А0 и В = В3В2В1В0. Конкретный вид операции, выполняемой микросхемой, задается 5-разрядным кодом на выходах МS3S2S1S0. Всего это АЛУ способно выполнить 25 = 32 операции: 16 логических и 16 арифметических и арифметико-логических. Операции сложения и вычитания проводятся с ускоренным переносом из разряда в разряд. Кроме того, имеется вход приема сигнала переноса С.

На выходах F0F1F2F3 формируются результаты логических преобразований и арифметических действий. На выходе переноса С4 образуется сигнал старшего (пятого) разряда при выполнении арифметических операций. Дополнительные выходы – образования ускоренного переноса G и распространения ускоренного переноса Р – используются только при организации многоразрядных АЛУ в случае их сочетания с блоком ускоренного переноса К555ИП4.

Слова А и В, подлежащие обработке, могут быть представлены в положительной либо отрицательной логике. Таблицы истинности для каждого варианта логики различны. Для положительной логики действительна таблица 1. Старший разряд кода выбора операции (вход М) определяет характер действий, выполняемых АЛУ. Когда на этом входе сигнал высокого уровня, АЛУ производит логические операции поразрядно над каждой парой бит слов А и В, а переносы между разрядами запрещаются.

При М = 0 АЛУ выполняет арифметико-логические операции. При этом логические операции выполняются поразрядно, а арифметические - с переносом. Результаты арифметических операций выражены в дополнительном коде. Как отмечалось, числа в дополнительном и в обратном коде связаны простым соотношением Nдоп = Nобр+ 1 или Nобр = Nдоп – 1. Поэтому в тех строках таблицы, где указана операция «минус 1», результат арифметических действий представлен в обратном коде.

Таблица 1 - Функциональная зависимость выходов микросхемы К555ИП3 от состояния входов

Выходной результат формируется с учетом состояния входа переноса. Оба сигнала переноса – входной С и выходной С4 – инверсные относительно сигналов на входах А и В, т.е. когда слова А и В – в положительной логике, сигналу переноса отвечает низкий уровень напряжения на соответствующем выходе, а в отрицательной логике – наоборот.

Если АЛУ выполняет логико-арифметическую операцию, логическая функция реализуется поразрядно, а арифметическая – с переносом. Например, входному коду МS3S2S1S0 = 01000 отвечает операция АB плюс А, где АB - логическое умножение двух слов. Если А = 0101 и В 1011, то первая операция дает АB = 0101, сумма 0101 плюс 0100 = 1001.

При использовании АЛУ в качестве компаратора сигнал снимают с выхода А = В (вывод 14). Этот выход с открытым коллектором, к источнику питания его следует подключать через внешний резистор 1 кОм. Режим компаратора обеспечивается при М = 0 и S3S2S1S0 = 0110. Когда числа А и В равны, на выходе А = В формируется сигнал высокого уровня.

Принципиальная схема устройств

Рисунок 2 – Принципиальная схема устройства

Принципиальная схема приведена на рисунке 2. Она включает в себя АЛУ D1.

АЛУ D1 (микросхема К155 ИП3) – это сложная комбинационная схема, предназначенная для выполнения арифметических и логических операций над четырехразрядными кодами чисел, причем, операции производятся над одноименными зарядами. Для увеличения разрядности чисел, например до восьми необходимо использоваться два таких устройства. При этом сигнал на выходе Cn+N младших четырех разрядов должен поступить на вход Cn старших четырех разрядов. Такое соединение позволит увеличить разрядность обрабатываемых чисел до 4N, где N – целое положительное число.

На входы А0…А3 АЛУ подается четырехразрядный код числа А, на входы В0…В3 – код числа В.

Двоичным кодом, поданным на входы S0…S3 АЛУ, задается код одной из 16 операций обработки операндов А и В. Если на управляющем входе М при этом установлен уровень логической единицы, то в АЛУ выполняется логическая операция, а если М=0, то арифметическая.

При выполнении логических операций (М=1) внутри АЛУ разрываются связи межразрядных связей.

При выполнении арифметических операций (М=0) эти цепи включаются и, кроме того, учитывается значение сигнала на входе переноса. Если Cn = 0, то считается, что перенос есть, а если Cn = 1, то переноса нет. Результат операции над операндами появляется на выходах F0…F3.

АЛУ имеет выход, который обозначен А=В. Высокий логический сигнал образуется, если F0=F1=F2=F3=1. Этот выход выполнен на схеме с открытым коллектором. Выходы P и G используются при построении АЛУ, обрабатывающих числа с разрядностью больше четырех.

Таблица соединений

|

Обозначение на схеме устройства |

Номер контакта устройства |

Номер контакта установки |

|

+5 В |

27 |

I47 |

|

0 B |

2 |

J47 |

|

Управляющие входы |

||

|

Сn |

15 |

J16 (F1) |

|

M |

20 |

J14 (F2) |

|

Входные двоичные коды чисел |

||

|

А0 |

25 |

J7 (E5) |

|

А1 |

31 |

J5 (E6) |

|

А2 |

33 |

J3 (E7) |

|

А3 |

35 |

J1 (E8) |

|

В0 |

23 |

J15 (E1) |

|

В1 |

26 |

J13 (E2) |

|

В2 |

34 |

J11 (E3) |

|

В3 |

36 |

J9 (E4) |

|

Код операции обработки |

||

|

S0 |

22 |

J8 (F5) |

|

S1 |

17 |

J6 (F6) |

|

S2 |

19 |

J4 (F7) |

|

S3 |

21 |

J2 (F8) |

|

Контроль результата операции |

||

|

F0 |

11 |

I32 (A0) |

|

F1 |

18 |

I30 (A1) |

|

F2 |

16 |

I28 (A2) |

|

F3 |

43 |

I26 (A3) |

|

Контроль дополнительных выходов |

||

|

G |

37 |

J33 (B0) |

|

P |

39 |

J31 (B1) |

|

Cn+N |

38 |

J29 (B2) |

|

A=B |

40 |

J27 (B3) |

Выводы

Проделав данную лабораторную работу, мы ознакомились с работой сумматора и регистра на практике. Получили навыки работы с субблоками. Путем спайки контактов мы получили рабочую схему, управляемую с помощью тумблеров на панели. Полученная схема своим поведением показывает работу АЛУ.