Потехин / накапливающий сумматор

.doc

Федеральное агентство по образованию

ТОМСКИЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ

И РАДИОЭЛЕКТРОНИКИ

Кафедра телевидения и управления

Лабораторная работа по курсу «Вычислительная техника и информационные технологии»

НАКАПЛИВАЮЩИЙ СУММАТОР

Проверил: Выполнили:

Доцент кафедры ТУ студенты группы 157

Потехин В.А._________ Семкин А.О. ________

Биктимирова Н.С._________

Томск 2009

Введение

Целью цикла лабораторных работ является ознакомление с типовыми узлами ЭВМ и микропроцессоров, получение навыков проверки субблоков, изготавливаемых с использованием микросхем средней и малой степени интеграции. Все используемые микросхемы относятся к классу транзисторно-транзисторной логики (ТТЛ).

Целью данной лабораторной работы является ознакомление с принципом работы комбинационного сумматора К155 ИМЗ (на принципиальной схеме имеет обозначение D1, D2), получение навыков работы с накапливающим сумматором, навыков сложения чисел в двоичном и двоично-десятичном кодах.

-

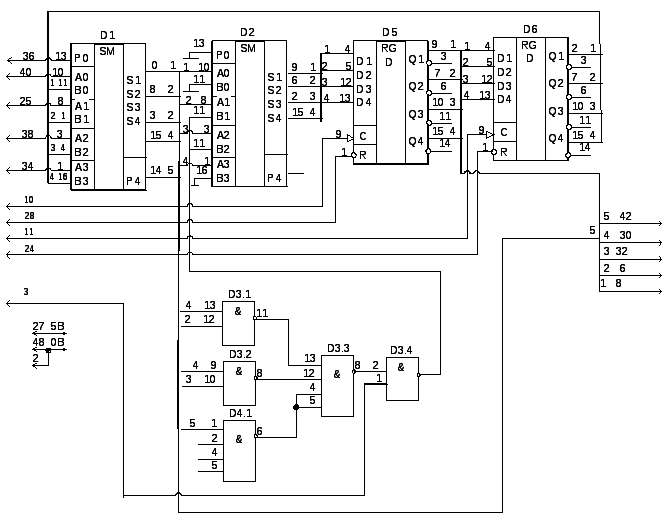

Принципиальная схема устройства

Принципиальная схема устройства представлена на рисунке 1.1.

Рисунок 1.1 Схема устройства

Комбинационные сумматоры D1, D2 (К155 ИМЗ):

-

Выполняют операцию суммирования двух четырехразрядных двоичных чисел A B с учетом переноса из предыдущего разряда P0 и формирования переноса в последующий разряд P. Закон функционирования i-го разряда сумматора:

|

Pi-1 |

Ai |

Bi |

A+B |

Pi |

|

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

0 |

|

0 |

1 |

0 |

1 |

0 |

|

0 |

1 |

1 |

0 |

1 |

|

1 |

0 |

0 |

1 |

0 |

|

1 |

0 |

1 |

0 |

1 |

|

1 |

1 |

0 |

0 |

1 |

|

1 |

1 |

1 |

1 |

1 |

Таким образом, булевы функции, описывающие работу сумматора имеют вид:

f(Ai + Bi) = Pi-1(AiBi + Ai’Bi’) + Pi-1’(AiBi’ + AiBi);

f(Pi) = AiBi + Pi-1(Ai + Bi);

Регистры D5, D6 (К155 ТМЗ):

-

D5 служит регистром хранения результата сложения.

-

D6 служит буферным регистром.

-

Оба регистра имеют входы сброса на ноль R0, причем сброс осуществляется асинхронно низким уровнем сигнала на входе. При этом выполняются микрооперации:

Y1: PrD5(4) := 0;

Y2: PrD6(4) := 0;

-

Синхровходы C служат для записи информации, установленной на входах D1,D2,D3,D4, в регистры, т.е. выполняются следующие микрооперации:

Y3: PrD5(4) := S2;

Y4: PrD6(4) := PrD5(4);

-

Таким образом, комбинационные сумматоры выполняют следующие функции сложения:

D1: S1 = PrD5(4) + A(4);

D2: S2 = S1 + const;

где А(4) – четырехразрядное двоичное число, поступающее на субблок с разъема;

Si – сумма, образованная на выходе i-го сумматора (i=1, 2);

const – константа, формируемая в схеме коррекции;

-

Схема коррекции D3, D4 предназначена для выработки констант. Она формирует две константы. Если на сумматоре складываются числа в двоичном коде, то в блок коррекции поступает признак K = 0 и блок вырабатывает константу, равную нулю, т.е. на D2 формируется сумма:

S2 = S1 + 0;

Если же на сумматоре складываются числа в двоично-десятичном коде (K = 1), то в определенных условиях схема коррекции вырабатывают константу G = 0110, т.е. на D2 формируется сумма:

S2 = S1 + 0110(2)

-

Ход работы

Для того, чтобы ознакомиться с принципом работы сумматора, соберем схему, изображенную на рисунке 2.1.

Рисунок 2.1 Схема лабораторной установки, накапливающий сумматор, соединенный с элементами управления

Таким образом, мы соединили входы первого сумматора (D1), синхровходы и входы сброса на ноль регистров и вход K схемы коррекции с тумблерами стенда (блок тумблеров E0 – E8, F0 – F8), а выходы регистра хранения суммы и выход P сумматора D1 со светодиодами стенда (блок светодиодов A). Т.е. получена возможность задавать суммируемые числа с помощью тумблеров и наблюдать полученную сумму на стенде в виде загорающихся светодиодов. Схема управляющих элементов приведена на рисунке 2.2 и рисунке 2.3.

Рисунок 2.2 Подключенные в соответствии со схемой светодиоды стенда

Рисунок 2.3 Подключенные в соответствии со схемой тумблеры стенда

Рассмотрим принцип работы устройства, выполнив задания данной лабораторной работы:

-

Произведем сложение трех чисел в двоичном коде. Для этого, подадим низкий уровень сигнала на вход К схемы коррекции (сложение в двоичном коде) тумблером F2 и «обнулим» значения, записанные в регистры, щелкнув тумблерами F0, F1. Затем подадим на входы Ai первого сумматора число, например 0100, подав высокий уровень тумблером E2. Переведем регистр D5 в режим записи, щелкнув тумблером E6. Если схема собрана верно, на стенде загорится светодиод A5, что будет соответствовать поданному числу 0100. Отключим режим записи регистра D5. Запишем в регистр D6 данное число, щелкнув тумблером E6. После этого, на вход сумматора D1 подается заданное число, соответственно, можно производить дальнейшее суммирование. Выключим режим записи регистра D6. Зададим на входе сумматора тумблерами E0-E3 следующее число, например, 1011, включим режим записи регистра D5. На стенде должны загореться все светодиоды A7-A4, что соответствует сумме чисел 1011 и 0100. Выключим режим записи регистра D5, включим режим записи регистра D6. После этого, на вход сумматора подается число 1111. Выключим режим записи регистра D6. Прибавим к полученной сумме число 0001, подав его на вход сумматора соответствующими тумблерами. Включим режим записи регистра D5. Если схема собрана верно, на стенде загорится светодиод A3, что соответствует числу 1 0000 (произошел перенос в старший разряд).

-

Проведем суммирование трех чисел в двоично-десятичном коде. Двоично-десятичный код – это такое представление десятичного числа, при котором каждый десятичный разряд представляется в виде его (разряда) четырехбитного двоичного аналога. В технике реализация двоично-десятичного кода производится путем добавления к двоичному числу «избытка 6». Т.е. для того, чтобы перевести двоичный код числа в двоично-десятичный, необходимо к двоичному коду прибавить число 01102. В данной лабораторной работе данное действие производится формированием константы «0110» схемой коррекции. Чтобы перейти к изображению чисел на стенде в виде двоично-десятичного необходимо подать высокий уровень сигнала на вход K тумблером F2. В этом случае, к каждому двоичному числу на выходе сумматора D1 будет прибавляться «избыток» 0110. Остальные действия по сложению чисел будут производиться аналогично предыдущему этапу. Стоит отметить, что для того, чтобы проверить правильность производимых действий (перейти от двоично-десятичного к двоичному коду) необходимо к числу, изображаемому на стенде прибавить «двоичную десятку», число 1010.

Выводы.

В ходе работы ознакомились с принципом работы сумматора, были получены практические навыки сложения чисел с использованием микросхем, освоены два вида представления чисел: двоичный и двоично-десятичный коды, получены навыки чтения и построения схем. Произведено сложение трех чисел, представленных двумя видами кодов.