Потехин / Сч с дш_вет_9с

.doc

Федеральное агентство по образованию

ТОМСКИЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ

(ТУСУР)

Кафедра промышленной электроники (Прэ)

ОТЧЕТ

Лабораторная работа по дисциплине «Вычислительная техника и информационные технологии».

СЧЕТЧИК С ДЕШИФРАТОРОМ

Преподаватель: Студент гр.363-18:

________Потехин В.А. ________Ширкунов П.Л.

__________2005г. ________Рахманов

__________2005г.

Новый Уренгой

2005

ВВЕДЕНИЕ

Целью данной лабораторной работы является ознакомление с работой типовых схем ТТЛ логики отечественного производства и их импортными аналогами. Работа выполняется в программе Electronic Workbench версии 5.0 и выше, так как данный программный продукт позволяет проектировать цифровые схемы, а также осуществлять контроль и испытание полученных цифровых устройств.

1 ОПИСАНИЕ СХЕМЫ УСТРОЙСТВА

Принципиальная схема исследуемого устройства включает в себя счетчик D1 и дешифратор D2. Счетчик D1 (К555ИЕ6 или 74192) – синхронный реверсивный четырехразрядный двоично-десятичный счетчик. Счетчик работает в коде 1-2-4-8, условное графическое изображение МСХ приведено на рисунке 1.1.

Рисунок 1.1 – Условное графическое обозначение ИС ИЕ6 (а); 74192 (б)

К исходному нулевому состоянию счетчик приводится при подаче на асинхронный вход R уровня лог. 1, при этом одновременно запрещается счет импульсов: Y1: Сч (4):= 0.

Входы «+1», «–1» – счетные входы для выполнения операций суммирования или вычитания соответственно:

+ 1: Y2: Сч (4): = Сч (4) + 1,

– 1: Y2: Сч (4): = Сч (4) – 1.

Причем при отсутствии какого-либо из

управляющих сигналов на вход должен

быть подан высокий уровень напряжения.

При подаче на вход «+1» тактовых импульсов

на выходах счетчика Q1, Q2, Q3, Q4 образуется

двоичный код 1-2-4-8. За 10 тактовых импульсов

счетчик приходит в состояние от 0 – 0000

до 9 – 1001. Когда все триггеры находятся

в единичном состоянии, то очередной

десятый тактовый импульс (низкий уровень

сигнала) проходит на выход переноса (![]() ≥ 9 вывод).

≥ 9 вывод).

Если счетчик работает на вычитание

(вход «–1»), то при переходе из состояния

0000 в состояние 1001 возникает заем из

старшего разряда. Это отображается

появлением сигнала низкого уровня на

выходе (![]() ≤ 0).

≤ 0).

Входы D1, D2, D4, D8 предназначены для записи в счетчик параллельного четырехразрядного управляющего кода, запись кода ведется при поступлении на вход синхронизации C сигнала низкого уровня. В счетчике реализуется микрооперация присвоения:

Y4: Сч(4): = Di,

где Di – четырехразрядный двоичный код.

При выполнении микрооперации установки, на входах «+1», «–1» должны быть установлены высокие уровни сигналов.

Дешифратор D2 (К555ИД3 или 74154) – это комбинационная схема для преобразования четырехразрядного двоичного кода (подается на входы 1-2-4-8) в шестнадцатеричный унитарный двоичный код (снимается с входов 0 – 15). Условное графическое обозначение дешифраторов приведено на рисунке 1.2.

Рисунок 1.2 – Условное обозначение: К155 ИД3 (а); 74154 (б).

Для включения дешифратора в работу необходимо, чтобы на управляющих входах W0,W1 были установлены сигналы низкого уровня. Каждой кодовой комбинации на входах 1-2-4-8 соответствует свой активный выход Yi, причем возбужденный выход принимает низкое значение уровня сигнала.

2 ОПИСАНИЕ ЭКСПЕРИМЕНТАЛЬНОЙ УСТАНОВКИ И МЕТОДИКИ ИЗМЕРЕНИЙ

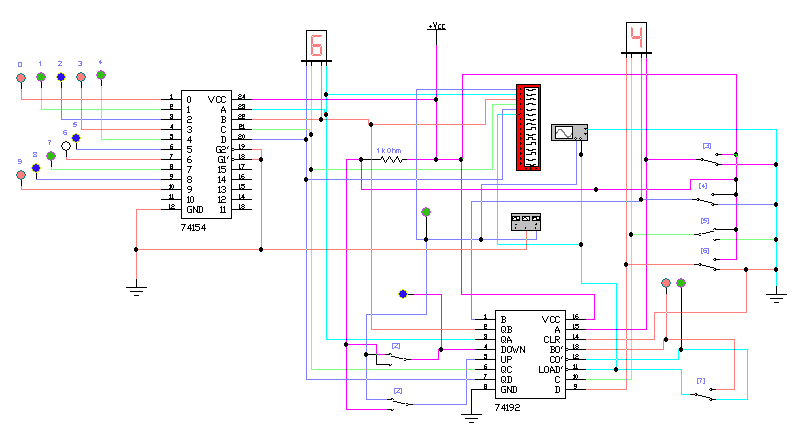

Полученная

принципиальная схема суммирующего

счетчика с дешифратором представлена

на рисунке 2.1, а на рисунке 2.2 представлены

эпюры напряжений на управляющих входах

счетчика и на всех его выходах:

Рисунок 2.1 – Принципиальная схема суммирующего счетчика.

Рисунок 2.2 – Эпюры напряжений на управляющих входах счетчика и на всех его выходах.

По полученным эпюрам напряжений первому тактовому импульсу соответствует код Q4=0, Q3=0, Q2=0, Q1=0, т.е. десятичной цифре 0, на первом выводе дешифратора низкий уровень напряжения. Второму импульсу соответствует Q4=0, Q3=0, Q2=0, Q1=1 код 0001 (цифра 1), на выводе 2 дешифратора (втором индикаторе) 0, и т.д. Индикаторы, подключенные к выводам дешифратора, будут поочередно гаснуть 0 1 2 3…..9. Таким образом, мы наблюдаем прямой счет.

Соберем схему вычитающего счетчика, для этого на вход «-1» подаем тактовые импульсы от генератора, на «+1» подаем сигнал высокого уровня. При переходе из состояния 0000 в состояние 1001 возникает заем из старшего разряда, что отображается появлением сигнала низкого уровня на выходе «≤0».

Полученная схема вычитающего счетчика с дешифратором представлена на рисунке 2.3, а эпюры напряжений на управляющих входах счетчика и на его выходах изображены на рисунке 2.4:

Рисунок 2.3 – Принципиальная схема вычитающего счетчика.

Рисунок 2.4 – Эпюры напряжений на управляющих входах счетчика и на всех его выходах.

По полученным эпюрам напряжений первому тактовому импульсу соответствует код Q4=1, Q3=0, Q2=0, Q1=1, т.е. десятичной цифре 9, на десятом выводе дешифратора низкий уровень напряжения. Второму импульсу соответствует Q4=1, Q3=0, Q2=0, Q1=0 код 1000 (цифра 8), на выводе 9 дешифратора 0, и так далее. Индикаторы, подключенные к выводам дешифратора, будут поочередно гаснуть 9 8 7 6….0. Таким образом, наблюдаем обратный счет.

Счетчик D1, помимо счета, выполняет еще

одну функцию – делителя входной частоты,

когда в качестве выходного используется

сигнал переноса (заем) или выходной

сигнал четвертого триггера. По отношению

к входной частоте Fвх (на входах

«+1» или «–1») частота на выходе Q1 имеет

значение

![]() ,

на выходе Q2 – Fвх /4 и т.д. Счетчик

может быть использован для построения

делителей частоты с коэффициентами

деления, отличными от вышеперечисленных.

,

на выходе Q2 – Fвх /4 и т.д. Счетчик

может быть использован для построения

делителей частоты с коэффициентами

деления, отличными от вышеперечисленных.

Строить делители частоты можно различными способами.

1. Если выходным сигналом «≥9» записать

в счетчик какое-либо двоичное число N <

9 (по входам D1, D2, D3, D4) и подать тактовые

импульсы с генератора на вход «+1», то

до переполнения счетчика необходимо

подать «![]() »

импульсов. Если при выработке каждого

импульса переполнения (выход «≥9») в

счетчик вновь записывать это число, то

счетчик всегда будет вести счет от N до

9. Таким образом, коэффициент деления

счетчика окажется равным «9-N».

»

импульсов. Если при выработке каждого

импульса переполнения (выход «≥9») в

счетчик вновь записывать это число, то

счетчик всегда будет вести счет от N до

9. Таким образом, коэффициент деления

счетчика окажется равным «9-N».

Если счетчик загружать по параллельным входам сигналом заем «≤0» (при работе счетчика в режиме вычитания), то коэффициент деления будет равен N.

2. Требуемый коэффициент деления счетчика можно получить, если при достижении счетчиком заданного числа N его сбрасывать в нулевое состояние. Коэффициент деления окажется равным N. Выделение двоичной комбинации N производится с помощью вспомогательной схемы «И-НЕ».

3. Третий способ изменения коэффициента деления основан на использовании дешифратора, выходной сигнал которого необходимо подать на вход R счетчика через дополнительный инвертор.

В нашей работе реализуем первый способ

делителя частоты. Для начала соберем

схему счетчика в режиме суммирования,

зададим N равным 4 и

определим количество импульсов, которые

необходимо подать до обнуления счетчика

(из вышеописанного следует, в данном

случае коэффициент деления должен быть

равным

![]() ).

Принципиальная схема делителя частоты

на суммирующем счетчике, представлена

на рисунке 2.5, эпюры напряжений на

управляющих входах счетчика и на его

выходах изображены на рисунке 2.6, а

осциллограмма, демонстрирующая число

импульсов, проходящих до обнуления

счетчика, приведена на рисунке 2.7:

).

Принципиальная схема делителя частоты

на суммирующем счетчике, представлена

на рисунке 2.5, эпюры напряжений на

управляющих входах счетчика и на его

выходах изображены на рисунке 2.6, а

осциллограмма, демонстрирующая число

импульсов, проходящих до обнуления

счетчика, приведена на рисунке 2.7:

Рисунок 2.5 – Принципиальная схема делителя частоты на суммирующем счетчике.

Рисунок 2.6 – Эпюры напряжений на управляющих входах счетчика и на всех его выходах.

Рисунок 2.7 – Осциллограмма, демонстрирующая число импульсов, проходящих до обнуления счетчика.

Построим такую же схему в режиме вычитания и убедимся, что коэффициент деления в этом случае будет равен 4 (при N = 4). Принципиальная схема делителя частоты на таком счетчике, представлена на рисунке 2.8, эпюры напряжений на управляющих входах счетчика и на его выходах изображены на рисунке 2.9, а осциллограмма, демонстрирующая число импульсов, проходящих до обнуления счетчика, приведена на рисунке 2.10:

Рисунок 2.8 – Принципиальная схема делителя частоты на вычитающем счетчике.

Рисунок 2.9 – Эпюры напряжений на управляющих входах счетчика и на всех его выходах.

Рисунок 2.10 – Осциллограмма, демонстрирующая число импульсов, проходящих до обнуления счетчика.

Выводы:

Выполнив данную лабораторную работу, мы ознакомились с базовыми элементами ТТЛ логики, изучили работу дешифраторов и счетчиков, а также научились использовать счетчики в качестве делителей частоты.