В состав линий управления шиной входных данных входят:

1) строб записи данных (FI_WR*).

Строб записи данных является синхронным сигналом. Активный уровень - низкий;

2) флаг готовности модуля к приему данных FI_INR*.

Сигнал флага готовности модуля к приему данных является синхронным. Активный уровень - низкий.

Высокий уровень сигнала FI_INR* свидетельствует о готовности входного буфера модуля к приему данных. Низкий уровень FI_INR* говорит о том, что буфер близок к заполнению и запись в него следует приостановить;

3) сигнал сброса входного буфера модуля FI_RST*.

Сигнал сброса входного буфера является асинхронным сигналом.

Активный уровень - низкий. Не влияет на конфигурацию БИС. Не является обязательными для использования.

В состав линий управления шиной выходных данных входят:

1) строб чтения данных (FO_RD*).

Строб чтения данных является синхронным сигналом. Активный уровень - низкий;

2) флаг готовности модуля к передаче данных FO_OR*.

Сигнал флага готовности модуля к передаче данных является синхронным. Активный уровень - низкий.

Активный уровень сигнала FO_OR* свидетельствует о наличии данных в выходном буфере модуля;

3) сигнал сброса выходного буфера модуля FO_RST*.

Сигнал сброса выходного буфера является асинхронным сигналом. Активный уровень - низкий. Не влияет на конфигурацию БИС. Не является обязательными для использования.

В состав линий управления модулем входят:

1) сигнал сброса RST*.

Сигнал сброса является асинхронным. Используется для инициализации модуля. Имеет активный низкий уровень. По данному сигналу происходит сброс входных и выходных буферов модуля и реконфигурация БИС. Длительность сигнала должна быть не менее 200 нс;

2) синхроимпульс CLK_IN.

Синхроимпульс является двунаправленным сигналом, тактирующим работу интерфейса. Чтение-запись данных в буферах модуля происходит по переднему фронту (переход из лог. "0" в лог. "1") данного сигнала. Может иметь частоту до 40 МГц. По умолчанию считается, что данный сигнал является входным для модуля. Имеется возможность формировать синхросигнал непосредственно на модуле и выдавать его внешнему устройству для формирования сигналов управления. В этом случае частота выдаваемого сигнала составит 33 МГц;

3) сигнал готовности модуля RDY*.

Сигнал готовности модуля является асинхронным. Свидетельствует об исправности и готовности модуля. Имеет активный низкий уровень. Устанавливается после завершения конфигурации БИС. Не является обязательным для использования.

В состав шины входных данных входит набор линий данных DI(0)...DI(35) - 36 линий.

Шина входных данных является однонаправленной и предназначена для приема данных в модуль. Активный уровень на линиях данных высокий, то есть:

- "логический ноль" по линии передается низким уровнем;

- "логическая единица" - высоким уровнем.

Информация, принимаемая по 36-разрядным линиям, состоит из двух частей: собственно данных, под которые задействуются разряды с "0" по "31", и 4-разрядного идентификатора. Коды идентификаторов приведены в приложении А.

В состав шины выходных данных входит набор линий данных DO(0)...DO(35) - 36 линий.

Шина выходных данных является однонаправленной и предназначена для передачи данных из модуля. Активный уровень на линиях данных - высокий, то есть:

- "логический ноль" по линии передается низким уровнем;

- "логическая единица" - высоким уровнем.

Информация, передаваемая по 36-разрядным линиям, состоит из двух частей: собственно данных, под которые задействуются разряды с "0" по "31", и 4-разрядного идентификатора. Коды идентификаторов приведены в приложении А.

Входные и выходные буферы модуля реализованы на микросхемах FIFO с разрядностью 36 бит. Соответственно, все временные соотношения данного интерфейса определяются спецификацией на применяемые микросхемы. Временные диаграммы входной и выходной шин приведены на рисунках 3 и 4.

Длительность сигнала RST* должна быть не менее 200 нс.

Длительность сигналов FI_RST* и FO_RST* должна быть не менее 40 нс.

Длительности сигналов измеряются на половине уровня их амплитуды.

Уровень логической "1" на входах модуля не должен быть ниже 2,0 В, а логического "0" - не выше 0,5 В. Уровень логической "1" на входах модуля не должен превышать значения 5,0 В.

Значение уровня логической единицы для выходных сигналов модуля не превышает 3,3 В.

Управление модулем осуществляется ПК аппаратуры потребителя посредством обращения к программно-доступным регистрам.

Перечень и адреса программно-доступных регистров, а также назначение отдельных разрядов этих регистров, приведены в описании контроллера модуля ВСК, приведенном в приложении А.

Описание контроллера модуля воск

Назначение

Контроллер модуля ВОСК выполняет следующие функции:

- интерфейс двунаправленных каналов связи 1Гбит;

- интерфейс 36–разрядного двунаправленного порта FIFO;

- коммутация потоков данных по схеме 3 источника – 3 приемника.

Состав и архитектура

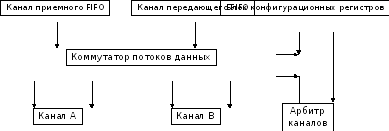

Структурная схема контроллера модуля ВСК показана на рисунке 1.

Архитектура контроллера модуля ВСК включает в себя следующие узлы:

- канал приемного FIFO – интерфейc канала приемного FIFO данных;

- канал передающего FIFO – интерфейc канала передающего FIFO данных;

- канал А – интерфейс внешнего приемо-передатчика канала А;

- канал В – интерфейс внешнего приемо-передатчика канала В. Идентичен каналу А;

- блок конфигурационных регистров. Содержит в себе регистры конфигурации, доступные как со стороны обоих оптических каналов, так и со стороны параллельного порта. Блок конфигурации управляет коммутацией

Рис. 1. Структурная схема контроллера модуля ВОСК.

потоков данных от источников к приемникам, а также арбитражем каналов в случае коммутации нескольких источников на один приемник;

- арбитр каналов – осуществляет арбитраж каналов – источников, коммутированных на один канал приемник, исходя из конфигурационного регистра блока конфигурации;

- коммутатор потоков данных – в зависимости от конфигурационных регистров производит коммутацию данных в следующих возможных направлениях:

- канал А –канал В;

- канал В –канал А;

- канал А – канал передающего FIFO;

- канал В – канал передающего FIFO;

- канал приемного FIFO – канал передающего FIFO;

- канал приемного FIFO –канал А;

- канал приемного FIFO –канал B.

Коммутатор потоков данных осуществляет дешифрацию команд, поступающих с каждого из входных каналов, а также, запись конфигурационных регистров контроллера.

Описание функционирования

Контроллер модуля ВОСК представляет собой регистровое устройство коммутации потоков данных с трех источников – два канала А и В и канал приемного FIFO, на 3 приемника – два канала А и В и канал передающего FIFO. Распределение данных между пользователями происходит исходя из конфигурационных внутренних регистров контроллера. Данные регистры доступны как со стороны оптических каналов, так и со стороны канала приемного FIFO.

Каналы А и В могут работать как на прием, так и на передачу данных, канал приемного FIFO работает только на прием данных, поступающих из внешнего приемного FIFO модуля, а канал передающего FIFO работает только на передачу данных, поступающих с коммутатора потоков данных во внешнее передающее FIFO.

Формат передачи данных в каналах А и В совместим со стандартом IEEE 802.3z Gigabit Ethernet. Кодирование данных в каналах происходит в стандарте 8В/10В. Пропускная способность каналов А и В 1,25 Гбит, пропускная способность канала - приемное FIFO – канал А или В - 37 МГц 36-разрядных слов.

Существует два режима работы контроллера: режим ON_LINE и режим OFF_LINE, данные режимы работы устанавливаются битом OP_MODE управляющего регистра контроллера REG_CFG_CTRL. В режиме OFF_LINE (ждущий режим) контроллер читает данные со всех источников, причем прочитанные данные не попадают ни в один из приемников. В режиме ON_LINE (активный режим работы) контроллер читает данные со всех источников и направляет прочитанные данные в соответствующие приемники.

В случае коммутации нескольких источников на один приемник начинает работать схема арбитража каналов, распределяющая поток данных, направленных в приемник между источниками, исходя из конфигурационных регистров контроллера.