Цикл обработки команды

Мы уже описывали в общих чертах, как протекает основной цикл обработки машинной команды. Рис. 11.4 повторяет один из рисунков, использованных в этом описании). Напомню, что цикл включает три основных фазы (или подцикла).

• Фаза извлечения. Считывание очередной команды из памяти в процессор.

• Фаза выполнения. Расшифровка кода операции и выполнение соответствующих действий.

Познакомившись

с особенностями организации процессора,

мы можем сейчас внести в эту упрощенную

схему цикла некоторые уточнения —

новые фазы.

Фаза косвенной адресации

В главе 10 было сказано, что в процессе выполнения команды процессору могут понадобиться операнды (один или два), находящиеся в памяти. Извлечение каждого операнда требует обращения к памяти. Если в спецификации операнда указан режим косвенной адресации, то помимо обращения к памяти за значением операнда, потребуется еще одно обращение к памяти за адресом операнда.

Можно считать, что извлечение косвенно заданного адреса — это еще одна фаза цикла обработки команды. Схема цикла с учетом варианта косвенной адресации показана на рис. 11.5. При обработке большинства команд в цикле фактически реализуются только две фазы — извлечения и выполнения. После того как команда извлечена, проверяется, не задан ли в ней в том или ином виде косвенный режим адресации. Если дело обстоит именно так, в цикл включается фаза извлечения косвенного адреса. После фазы выполнения перед началом следующего цикла может включаться фаза прерывания, если поступил запрос прерывания.

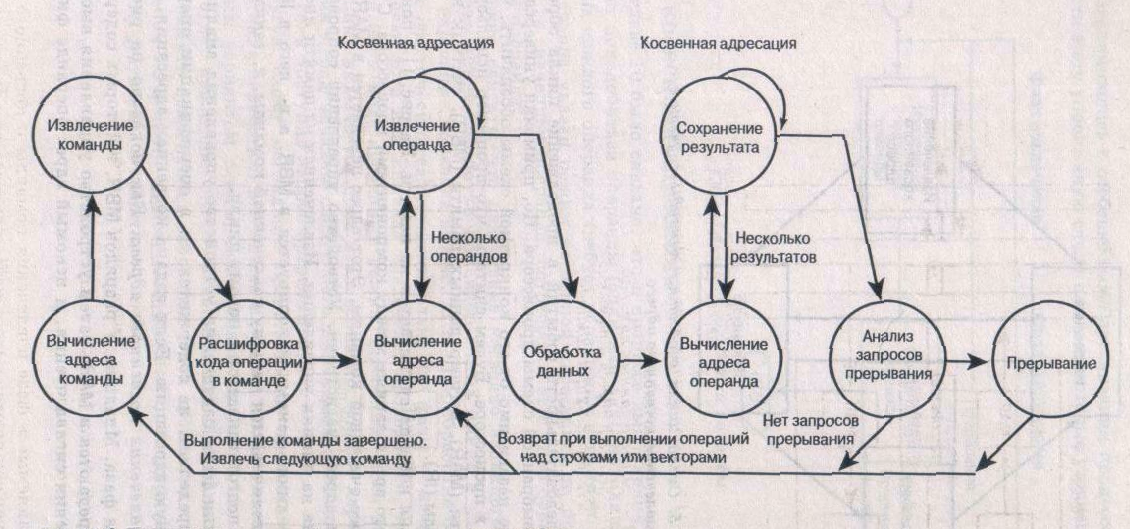

Другую схему наглядного представления процессов, происходящих во время цикла обработки, вы видите на рис. 11.6. Эта схема является переработанным вариантом схемы, помещенной на рис. 3.12. После того как команда будет извлечена, нужно расшифровать спецификации операндов. Затем из памяти извлекаются операнды, и эта процедура может включать фазу извлечения косвенного адреса. Аналогичная процедура выполняется при сохранении результата в памяти.

Поток данных

Конкретная последовательность событий в продолжение цикла обработки команды зависит от выбранной схемы процессора. Но, применяя универсальную терминологию, можно независимо от его конкретной схемы обозначить, что же должно происходить в процессоре. Будем считать, что процессор использует регистр адреса в памяти (MAR), регистр данных памяти (MBR), счетчик команд (PC) и регистр команды (IR).

В фазе извлечения команда считывается из памяти. На рис. 11.7 показано, как циркулируют в это время данные между компонентами процессора. Счетчик команд содержит адрес очередной команды. Этот адрес передается в MAR и выставляется на линии адреса магистрали. Устройство управления сопровождает адрес сигналом чтения на линиях управления. Извлеченная из памяти информация выставляется на линии данных и копируется в MBR, а из него в IR. Тем временем код в PC увеличивается на дину извлеченной команды, и, таким образом, счетчик команд подготавливается к новому циклу.

После завершения фазы извлечения устройство управления анализирует содержимое IR и определяет, не содержится ли в спецификации операндов указания на косвенную адресацию. Если задана косвенная адресация, наступает черед фазы извлечения косвенного адреса. Как показано на рис. 11.8, это довольно простая фаза. Младшие N разрядов MBR, в которых содержится ссылка на адрес, передаются в MAR. Затем устройство управления выставляет на линии управления сигнал чтения, и искомый адрес операнда фиксируется в MBR.

Рис. 11.6. Диаграмма состояний цикла обработки команды

Рис. 11.7. Поток данных в фазе извлечения

Условные обозначения: MBR — регистр данных памяти,; MAR — регистр адреса в памяти; IR — регистр текущей команды; PC — счетчик команд

Рис. 11.8. Поток данных в фазе извлечения косвенного адреса

Операции, выполняемые в фазе извлечения команды и косвенного адреса, просты и легко прогнозируются. Этого нельзя сказать об операциях фазы выполнения команды, поскольку они зависят как от содержимого кода команды в регистре IR, так и от результатов выполнения предыдущей команды (а иногда и нескольких предыдущих команд). В этой фазе может выполняться передача данных между регистрами, чтение или запись в память или в модуль ввода-вывода и/или выполнение арифметических или логических операций с участием АЛУ.

Последняя фаза цикла — фаза прерывания — также достаточно проста и предсказуема (рис. 11.9). Если имеется запрос прерывания и обработка прерываний разрешена, сохраняется текущее содержимое счетчика команд, что позволяет в дальнейшем возобновить выполнение прерванной программы с той же точки. Для этого содержимое PC передается в регистр MBR, чтобы его можно было записать в память. Адрес ячейки, выделенной с этой целью в памяти, "знает" устройство управления и передает его в регистр MAR. Чаще всего для хранения содержимого счетчика команд используется системный стек и, таким образом, этот адрес содержится в регистре указателя стека. В PC вместо текущего адреса прерванной программы загружается начальный адрес подпрограммы обработки прерывания. В результате следующий цикл начнется с извлечения первой команды подпрограммы обработки прерывания.