- •5 Логические (цифровые) устройства 106

- •5.1 Комбинационные логические элементы 106

- •5.2 Последовательностные устройства 130

- •5 Логические (цифровые) устройства

- •5.1 Комбинационные логические элементы

- •5.1.1 Основные определения алгебры логики

- •5.1.2 Представление логических функций

- •5.1.3 Законы (правила преобразования) алгебры логики

- •5.1.4 Способы минимизации логических функций

- •5.1.5 Основные параметры и характеристики цис

- •5.1.6 Основные серии цифровых интегральных схем

- •5.1.7 Схемотехника логических элементов на диодах

- •5.1.8 Схемотехника ттл логики

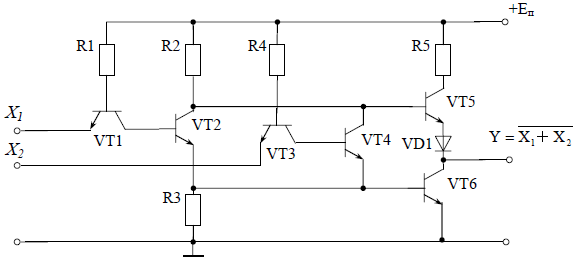

- •5.10 Ттл логический элемент или-не

- •5.1.9 Схемотехника кмоп логических элементов

- •5.1.10 Сумматоры

- •5.1.11 Дешифраторы

- •5.1.12 Мультиплексоры

- •5.2 Последовательностные устройства

- •5.2.1 Rs-триггер

- •Синтез rs-триггера на элементах или-не

- •5.2.2 Счетный т-триггер

- •5.2.4 Универсальный jk-триггер

- •5.2.5 Счетчики сигналов

- •5.2.6 Регистры

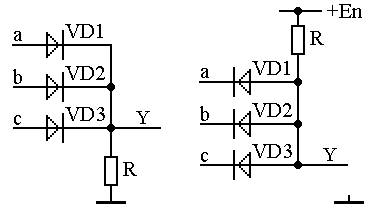

5.1.7 Схемотехника логических элементов на диодах

Диодная логика (ДЛ) не обладает усилением и не позволяет построить сложные логические схемы, однако она используется в виде одиночных элементов с релейными или аналоговыми устройствами.

Логический элемент ИЛИ.

а) б)

Рис. 5.7 Диодная логика: а) – элемент ИЛИ; б) – элемент И

Схема логического элемента ИЛИ приведена на рис. 5.7, а, ее еще называют схемой выделения максимума. Выходной сигнал формируется из входного сигнала, который имеет наибольшее напряжения. Если все входные сигналы нулевые – выход нулевой, если хотя бы один входной сигнал единичный - выход единичный. Уровень единичного сигнала меньше входного сигнала на величину падения на диоде, то есть сигнал ослабляется при прохождении через элемент. Реализуемое логическое уравнение

Y = a + b + c. (5.7)

Схема логического элемента И приведена на рис. 5.7, б, ее еще называют схемой выделения минимума. Выходной сигнал единичного уровня формируется резистором R. Если хотя бы на одном из входов нулевой уровень, то открывается диод и на выходе формируется нулевой уровень. Потенциал нулевого уровня на выходе на падения напряжения на диоде больше минимального входного сигнала. Реализуемое логическое уравнение

Y = a . b . c. (5.8)

Диодно-транзисторный элемент И-НЕ.

Рис. 5.8 Схема диодно-транзисторного элемента И-НЕ

Элемент состоит из диодного логического элемента И, выполненного на диодах VD1, VD2, VD3 и инвертора на транзисторе VT1. Элемент обладает усилением и пригоден для построения сложных логических схем. Диоды VD4, VD5 служат для надежного запирания транзистора. Падение на этих диодах компенсирует остаточное напряжение нулевого сигнала. Реализуемое логическое уравнение

![]() . (5.9)

. (5.9)

5.1.8 Схемотехника ттл логики

Схема ЛЭ обычно содержит три основных узла:

Входной для реализации требуемой логической функции.

Промежуточный, для усиления с целью повышения помехоустойчивости и обеспечения крутизны передаточной характеристики.

Выходной – для обеспечения требуемой нагрузочной способности и крутизны фронтов выходного сигнала. На рис. 5.9 приведена схема логического элемента И-НЕ.

Рис. 5.9 ТТЛ логический элемент И-НЕ

Входной узел выполнен на транзисторе VT1, который можно представить в виде диодной логики. Эмиттерные переходы ведут себя как диоды VD1-VD3 схемы рис. 5.8. Коллекторный переход выполняет функции диодов VD4, VD5 схемы рис. 5.8.

На транзисторе VT2 выполнен усилитель-формирователь для управления сложным выходным инвертором на транзисторах VT3 и VT4. Усилитель-формирователь и сложный инвертор образуют формирователь-инвертор ФИ. Все транзисторы в режиме насыщения имеют Uкэ.нас ≈ 0,2 В.

При подаче хотя бы на один вход низкого уровня сигнала UВХ =(0…0,4) В. Транзистор VT1 закроется. Ток базы транзистора VT2, равный обратному току коллектора VT1, не достаточен для отпирания транзистора VT2, и он находится в запертом состоянии. При этом величина напряжения на его коллекторе UК2 достаточна для отпирания транзистора VT3. Напряжение на эмиттере VT2, равное падению напряжения на резисторе R3 от тока запертого эмиттерного перехода VT2, не достаточно для отпирания транзистора VT4. Таким образом, при подаче низкого уровня входного сигнала транзистор VT3 открыт, а VT4 заперт. При этом на выходе схемы будет высокий уровень напряжения UВЫХ ≈ 3,3 В.

При отключенных входах или подаче на все входы высокого уровня входного сигнала UВХ =(1,9…4,5) В эмиттерные переходы транзистора VT1 смещается в обратном направлении, а коллекторный переход открыт. Ток базы транзистора VT2, равный коллекторному току транзистора VT1, достаточен для отпирания транзистора VT2. Отпирание этого транзистора снижает напряжение на базе транзистора VT3 и увеличивает на базе VT4.

В результате этого транзистор VT3 запирается, а VT4 открывается и на выходе формируется низкий уровень выходного напряжения UВЫХ < 0,4 В.

Диод VD1 служит для надежного запирания транзистора VT3 путем увеличения порогового отпирающего напряжения на величину падения напряжения на этом диоде. Резистор R4 служит для ограничения тока выходных транзисторов в переходных режимах, когда оба транзистора работают в активной области.