Глава 14

.pdf14.Периферийные модули микроконтроллера PIC 16F877

иособенности их программирования

При практическом программировании микроконтроллеров PIC 16F877 в дополнение к приемам и методам, описанным при программировании микроконтроллера 16С52, необходимо дополнительно учитывать следующие факторы:

-наличие аппаратно подключенных к контактам портов микроконтроллера внешних устройств, например, в составе промышленного контроллера TTF 5.0, и соответственно невозможность изменения конфигурации и мультиплицирования этих контактов в процессе работы;

-наличие страничной организации памяти данных и команд, отличной от соответствующей организации 16С52 и механизмов косвенной адресации регистров в этом случае;

-наличие модульной структуры микроконтроллера, при которой кроме АЛУ, специальных регистров, РОН-ов и т.д., приведенных на рис. 8, в состав

16F877 входят дополнительные встроенные устройства, расширяющие его функциональность и называемое модулями. Их особенностью является то, что ими можно управлять (включать, выключать, конфигурировать и т.д.) с помощью определенных бит групп специальных регистров.

-возможность использования в asm-файле имен регистров и их отдель-

ных бит, зарезервированных и хранимых в специальном файле, «подключаемом»

кasm-файлу. Другими словами, при написании команд в теле ПО возможно использование имен регистров и их отдельных бит в соответствие с их описанием в структурных схемах модулей микроконтроллера.

Примечание: Компилятор среды MPLAB автоматически сгенерирует их адреса вместо имен. Например, вместо команды btfsc PIR1, RCIF будет сгенерирована стандартная команда btfsc 0х0С, 0х05. Однако, к этой «автоматической» замене следует относиться осторожно, т.к. ошибочная запись btfsc RCIF, PIR1 в этом случае не обнаруживается MPLABом (хотя и выводится предупреждающее сообщение о выходе значения за пределы разрешенного диапазона), интерпретируется как правильное и приводится к виду btfsc 0х05, 0х04. При этом вместо контроля состояния бита RCIF в регистре PIR1будет происходить контроль бита RA4 в регистре PORTA. Это происходит из-за «автоматической» замены в директивах RCIF equ 0x05, PIR1 equ 0x0C, но учитывая отсутствие бита с номером 0х0С в в8-ми разрядном регистре порта А, компилятор «добавляет» еще одну ошибку: он приводит число 0х0С по модулю 8 и «получает» бит с адресом 0х04.

Ниже будут рассмотрены особенности практического программирования PIC контроллера 16F877, при его работе в составе промышленного контроллера

TTF 5.0.

14.1 Страничный способ организации памяти данных микроконтроллера PIC 16F877

Страничный способ организации памяти данных предусматривает логическое распределение адресов регистров в виде 4-х последовательно расположен-

ных групп, называемых банками (или страницами) памяти. В случае PIC 16F877 вся физически реализованная статическая регистровая память общим

объемом 512 байт делится на 4 банка по 128 байт (рис. 127). Проводя аналогию с

0 (0х00) |

|

128 |

(0х80) |

32 |

32 |

|

|

SFR |

SFR |

|

|

31 (0х1F) |

|

159 |

(0х9F) |

32 (0х20) |

|

160 |

(0хА0) |

96 |

80 |

|

|

РОН |

РОН |

|

|

|

|

239 |

(0хЕF) |

|

16 |

240 |

(0хF0) |

|

ячеек |

|

|

127 (0х7F) |

|

255 |

(0хFF) |

Банк 0 |

Банк 1 |

|

|

|

0 (0х00) |

16 |

|

SFR |

15 (0х0F) |

|

16 (0х10) |

96 |

|

РОН |

|

|

111 (0х6F) |

16 |

112 (0х70) |

ячеек |

|

|

127 (0х7F) |

Банк 2 |

|

|

128 |

(0х80) |

16 |

|

|

SFR |

143 (0х8F) |

|

|

144 |

(0х90) |

96 |

|

|

РОН |

|

|

|

239 |

(0хEF) |

16 |

240 |

(0хF0) |

ячеек |

|

|

|

255 |

(0хFF) |

Банк 3 |

|

|

|

|

01 |

|

10 |

|

|

|

|

|

11 |

|

00 |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

7 |

6 |

5 |

4 |

3 |

|

2 |

|

1 |

0 |

|

|

|

|

|

STATUS |

|

|

|

||||

512 = 4 x 128 = (32+32+16+16) + (96+80+96+96) + (16+16+16) |

|||||||||||

|

|

96 SFR |

|

|

368 РОН |

|

|

48 виртуальных ячеек |

|||

Рис. 127 Упрощенная карта страниц памяти данных контроллера PIC 16F877 и принципы ее адресации

микроконтроллером 16С52, можно сказать, что у него ОЗУ состоит из одной страницы размером 32 байта. Приведенная карта распределения памяти отражает распределение регистров между специальными регистрами SFR и регистрами общего назначения РОН. Как видно из этого рисунка, банк 0 содержит в своем составе 32 специальных регистра и 96 РОН-ов, банк 2 – соответственно 32 и 80 и т.д. Кроме этого, в составе 1-3 банков есть по 16 «виртуальных ячеек» логически недоступных пользовательскому ПО. Таким образом, из 512 байт ОЗУ – 96 отдано под специальные регистры, 48 недоступно пользователю, т.е. реально доступный объем ОЗУ составляет 368 байт (РОН-ов).

При таком способе организации памяти доступ и адресация конкретного регистра в общем адресном пространстве памяти несколько усложняется и со-

держит 2 строго последовательных шага:

-выбор номера банка (0,1,2,3) посредство установки 5-го (RP0) и 6-го (RP1) битов регистра STATUS в соответствии с рис. 127;

-выбор адреса требуемого регистра в установленном банке в диапазоне

0х00 – 0хFF (т.е. от 0 до 255) так, как будто адресуются 256 регистров, расположенные в первых двух банках, независимо от того в каком банке реально располагается требуемый регистр.

INDNF |

00h |

INDNF |

80h |

INDNF |

100h |

INDNF |

180h |

|

TMR0 |

01h |

OPTION_REG |

81h |

TMR0 |

101h |

OPTION_REG |

181h |

|

PCL |

02h |

PCL |

82h |

PCL |

102h |

PCL |

182h |

|

STATUS |

03h |

STATUS |

83h |

STATUS |

103h |

STATUS |

183h |

|

FSR |

04h |

FSR |

84h |

FSR |

104h |

FSR |

184h |

|

POTRA |

05h |

TRISA |

85h |

************ |

105h |

************ |

185h |

|

PORTB |

06h |

TRISB |

86h |

PORTB |

106h |

TRISB |

186h |

|

PORTC |

07h |

TRISC |

87h |

************ |

107h |

************ |

187h |

|

PORTD |

08h |

TRISD |

88h |

************ |

108h |

************ |

188h |

|

PORTE |

09h |

TRISE |

89h |

************ |

109h |

************ |

189h |

|

PCLATH |

0Ah |

PCLATH |

8Ah |

PCLATH |

10Ah |

PCLATH |

18Ah |

|

INTCON |

0Bh |

INTCON |

8Bh |

INTCON |

10Bh |

INTCON |

18Bh |

|

PIR1 |

0Ch |

PIE1 |

8Ch |

EEDATA |

10Ch |

EECON1 |

18Ch |

|

PIR2 |

0Dh |

PIE2 |

8Dh |

EEADR |

10Dh |

EECON2 |

18Dh |

|

TMR1L |

0Eh |

PCON |

8Eh |

EEDATH |

10Eh |

************ |

18Eh |

|

TMR1H |

0Fh |

************ |

8Fh |

EEADRH |

10Fh |

************ |

18Fh |

|

T1CON |

10h |

************ |

90h |

|

110h |

|

190h |

|

TMR2 |

11h |

SSPCON2 |

91h |

|

111h |

|

191h |

|

T2CON |

12h |

PR2 |

92h |

|

112h |

|

192h |

|

SSPBUF |

13h |

SSPADD |

93h |

|

113h |

|

193h |

|

SSPCON |

14h |

SSPSTAT |

94h |

|

114h |

|

194h |

|

CCPR1L |

15h |

************ |

95h |

|

115h |

|

195h |

|

CCPR1H |

16h |

************ |

96h |

РОН |

116h |

РОН |

196h |

|

CCP1CON |

17h |

************ |

97h |

|

117h |

|

197h |

|

RCSTA |

18h |

TXSTA |

98h |

|

118h |

|

198h |

|

TXREG |

19h |

SPBRG |

99h |

|

119h |

|

199h |

|

RCREG |

1Ah |

************ |

9Ah |

|

11Ah |

|

19Ah |

|

CCPR2L |

1Bh |

************ |

9Bh |

|

11Bh |

|

19Bh |

|

CCPR2H |

1Ch |

************ |

9Ch |

|

11Ch |

|

19Ch |

|

CCP2CON |

1Dh |

************ |

9Dh |

|

11Dh |

|

19Dh |

|

ADRESH |

1Eh |

ADRESL |

9Eh |

|

11Eh |

|

19Eh |

|

ADCON0 |

1Fh |

ADCON1 |

9Fh |

|

11Fh |

|

19Fh |

|

|

20h |

|

A0h |

|

120h |

|

1A0h |

|

РОН |

|

РОН |

|

РОН |

|

|

РОН |

|

|

|

|

EFh |

|

16Fh |

|

1EFh |

|

|

|

|

F0h |

|

170h |

|

1F0h |

|

|

|

70h – 7Fh |

|

70h – 7Fh |

|

|

70h – 7Fh |

|

|

7Fh |

|

FFh |

|

17Fh |

|

1FFh |

|

Банк 0 |

|

Банк 1 |

|

Банк 2 |

|

|

Банк 3 |

|

Рис. 128 Полная карта памяти данных микроконтроллера PIC 16F877

Другими словами, ПЕРЕД ЛЮБОЙ ОПЕРАЦИЕЙ С ЛЮБЫМ (кроме,

W) РЕГИСТРОМ, ПРЕДВАРИТЕЛЬНО НАДО УСТАНОВИТЬ НОМЕР БАНКА В КОТРОМ ОН НАХОДИТСЯ.

Примечание: при адресации некоторых специальных регистров (INDNF, PCL, STATUS, FSR, PCLATH, INTCON) не требуется предварительный выбор страницы памяти. Это связано с тем, что они расположены (дублированы) во ВСЕХ банках памяти с одинаковым относительным адресом (смещением по вертикали относительно начала страницы). Это сделано в тех случаях, когда биты этих регистров в той или иной мере управляют логическим распределением самих страниц. В случае же регистра W, адресация банка не нужна, т.к. он не входит в состав памяти данных.

На рис.128 приведена полная карта памяти данных контроллера PIC 16F877.

При ее использовании и адресации необходимо также учитывать следую-

щие особенности:

-помеченные значками «***********» регистры 1-го – 3-го банков следует исключить из обращения, т.к. хотя логически запись в них разрешена, но последующее их чтение дает результат 0х00, и, следовательно, использовать их в качестве РОН-ов для хранения данных невозможно;

-наличие в составе 1-3 банков «виртуальных» регистров (заштрихованных на рис. 127) в диапазоне адресов 0xF0-0xFF (для 1-го банка), 0x170-0x17F (для 2- го) и 0x1F0-0x1FF (для 3-го) содержимое которых «горизонтально отображается» на 16 реальных «нижних по карте» регистров общего назначения 0-го банка с адресами 0x70-0x7F. Их особенность состоит в том, что попытка записи в любой из них приводит к записи во все 4 регистра всех банков расположенных на карте по «одной горизонтали».

Пример:

bcf status, 0x06 bsf status, 0x05 movwf 0x172

указанный код запишет содержимое регистра W не только в 0х172-ой регистр банка 2, но и соответственно в 0х72-ой регистр 0-го банка, и в 0хF2-ой регистр 1- го банка, и в 0х1F2-ой регистр 3-го банка.

Имеет место и обратное «отображение», когда содержимое реальных регистров банка 0 (с адресами 0x70-0x7F) будет автоматически помещено во все «горизонтальные» регистры банков 1,2,3. Поэтому использование «виртуальных регистров» в качестве РОН-ов – ЗАПРЕЩЕНО.

- косвенная адресация РОН-ов отличается от случая одностраничной организации памяти (п. 6.3.3) и осуществляется в соответствие с рис. 128.1.

В этом случае 8-ми разрядный регистр FSR (как всегда, через регистр INDF) адресует 28 = 256 регистров, расположенных в одной из ПАР БАНКОВ, а НОМЕР ПАРЫ выбирает бит IRP регистра STATUS, таким образом, что при IRP=0 адресуются 256 регистров 0-го и 1-го банков, а при IRP=1 - соответственно 256 регистров 2-го и 3-го банков. Строго говоря, выбор страницы при

Непосредственная адресация |

|

|

|

|

|

|

|

Косвенная адресация |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

STATUS |

|

7-разрядный АДРЕС в команде |

|

|

STATUS |

|

|

|

|

FSR |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RP1 |

RP0 |

|

|

|

|

|

|

|

|

|

|

|

|

IRP |

|

|

7 |

6 |

|

…… |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Выбор банка |

|

Выбор регистра 0 - 127 |

|

|

|

|

|

|

|

|

Выбор банка |

|

|

Выбор регистра |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 - 127 |

|

||

|

|

00 |

|

|

01 |

10 |

11 |

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

0x00 |

0x80 |

0x100 |

0x180 |

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

Банк0 |

Банк1 |

Банк2 |

Банк3 |

|

|

|

INDF |

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

О |

З У |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x7F |

0xFF |

0x17F |

0x1FF |

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 128.1 Механизмы непосредственной и косвенной адресации при страничной организации памяти (на примере контроллера PIC 16F877)

косвенной адресации осуществляется двумя битами: старшим - IRP и младшим - 8-м битом регистра FSR (как и битами RP1,0 при непосредственной адресации). Но при практическом программировании достаточно (битом IRP) выбрать пару страниц, где находится требуемый регистр, т.к. выбор требуемой страницы из выбранной пары произойдет автоматически при записи 8-ми разрядного адреса в FSR. Это происходит в силу того, что пока 8-ой бит регистра FSR=0, происходит обращение к 128 регистрам ОЗУ «младшей» страницы пары (за счет 7-ми младших битов регистра FSR), выбранной битом IRP. Если же 8-ой бит регистра FSR=1, то аналогично адресуются 27=128 РОН-ов из «старшей» страницы этой же пары.

Ниже приведен исходный код ПО примера «обнуления ВСЕЙ памяти данных» с использованием косвенной адресации (пример носит исключительно УЧЕБНЫЙ характер). Реальный пример см. в «Методических указаниях к лаб. Работам по курсу ПЦУ».

|

bcf STATUS, IRP |

; установка первой ПАРЫ страниц (0-ая и 1-ая) |

|

movlw 0x01 |

; установка адреса первого обнуляемого регистра на этой паре |

|

movwf FSR |

|

Zero |

clrf INDF |

; начало обнуления |

|

incf FSR, f |

; переход к следующему адресу обнуляемого регистра |

|

btfss STATUS, Z |

; обнулены все 256 регистров на ПЕРВОЙ ПАРЕ страниц ? |

|

goto Zero |

; нет, продолжаем обнулять ПЕРВУЮ ПАРУ страниц |

|

bsf STATUS, IRP |

; да, переходим на ВТОРУЮ ПАРУ страниц (2-ая и 3-я), при этом FSR = 0 |

|

goto Zero |

; начинаем обнулять вторую страницу, начиная с нулевого регистра |

14.2 Модуль аналого-цифрового преобразования (АЦП) 14.2.1 Циклограмма работы АЦП, временные диаграммы

Циклограмма работы модуля АЦП (рис. 129) представляет собой последовательность процессов, происходящих в микроконтроллере (м/к), начиная с мо-

|

|

1 ый отсчет вх. сигнала |

|

|

2 ой отсчет вх. сигнала |

|||||

заряд С HOLD |

преобразование A/D |

пауза |

|

|||||||

|

|

|||||||||

≥ 20 мкс |

|

|

≥ 12 T AD |

|

≥ 2 T AD |

|

||||

|

|

|

|

|

||||||

Выбор, конфигурирование аналогового входа и |

к |

источнику входного сигнала (ADCON0,1) |

запуск начала преобразования и отключение |

источника вход- |

ного сигнала путем установки бита |

|

|

|

|

|

HOLD |

|

завершение A/D преобразования: |

Рис. 129 Циклограм- |

|||||||

|

10—ти разрядный результат по- |

|||||||||

|

ма работы АЦП мик- |

|||||||||

|

мещен |

в регистры ADRES и |

||||||||

|

СHOLD вновь подключен к источ- |

|

||||||||

подключениеС |

от |

GODONE=1 |

роконтроллера PIC |

|||||||

нику входного сигнала выбран- |

||||||||||

HOLD |

|

|||||||||

ного канала, бит GO_DONE = 0 |

16F877 |

|||||||||

|

|

|

||||||||

С |

|

|

|

|||||||

мента начала преобразования («оцифровки») и заканчивая записью 10-ти разрядного результата в пару 8-и разрядных регистров, доступную по шине данных м/к.

Программно работа модуля АЦП содержит 3 основных этапа для одного отсчета мгновенного значения входного напряжения и преобразования его в параллельный 10-ти разрядный код. Далее эти этапы периодически должны повторяться:

- выбор одного из 8 возможных каналов АЦП, его настройка в качестве аналогового входа и подача питания на модуль (предварительно НЕ НА ЭТОМ ЭТАПЕ выбранный контакт контроллера должен быть регистром TRIS сконфигурирован как входной). При этом внутренний накопительный конденсатор C HOLD подключается к выбранному контакту и начинает заряжаться от Uвх. Напряжение на этом конденсаторе (равное Uвх) будет использовано в дальнейшем при

«оцифровке», поэтому необходимо обеспечить чтобы время заряда было не меньше 20 мкс (это определено в технической документации на PIC 16F877 и реализуется путем введения задержки в тело ПО), иначе C HOLD не успеет полностью зарядиться и «оцифровано» будет не истинное мгновенное значение входного сигнала, а напряжение до которого C HOLD успел зарядиться, и соответственно возникнет погрешность преобразования;

-преобразование напряжения на конденсаторе C HOLD (после заряда он аппаратно отключается от входного контакта контроллера) в 10-ти разрядный код. Этап начинается с установки в программе бита GO_DONE (регистра ADCON0,

см. рис. 132) в «1» и длится минимум 12 TAD (о выборе времени TAD см. ниже). В течение этого времени последовательно бит за битом (начиная со старшего 9-го)

врегистровую пару ADRESH, ADRESL записывается 10-ти разрядный код результата. Завершается этап сбросом бита GO_DONE в «0» самим контроллером;

-пауза, которая должна быть выдержана в ПО перед началом 2-го (и каж-

дого последующего) отсчета. Это время должно быть не менее 2 TAD и связано инерционностью ключа, вновь подключающего конденсатор C HOLD к входному контакту контроллера.

После выполнения этих трех этапов цикл работы АЦП может быть повто-

рен для «оцифровки» следующего мгновенного значения Uвх. Обратите внимание, что бит GO_DONE используется двояко: как пользовательской программой, так и самим контроллером автономно. Во-первых, как управляющий входной бит ПО для запуска преобразования, а во-вторых, как выходной индикатор успешного окончания этого процесса. Поэтому изменять программно состояние бита GO_DONE в течение времени преобразования – запрещено, это вызовет сброс АЦП.

При практическом программировании приведенного алгоритма необходимо программно задавать длительность каждого этапа. В качестве «единицы измерения» времени (см. рис. 129) используется величина TAD – время преобразования одного бита, задаваемое программно, но имеющее нижнюю аппаратную границу TAD ≥ 1,6 мкс (т.е. быстрее микроконтроллер не может «оцифровать» один бит). Физически это время (точнее длительность полного цикла АЦП, равное 20 + (12 + 2)TAD ≈ 43 мкс) определяет максимальную частоту преобразования fц = (1/43) МГц ≈ 23 кГц. В соответствие с теоремой Котельникова можно определить и максимально возможную частоту входного сигнала, который можно «оцифровать» с помощью данного контроллера Fc = ½ fц ≈ 12 кГц. Если входной сигнал изменяется «быстрее», то АЦП не будет «видеть» эти изменения и появятся «пропуски» мгновенных значений входного сигнала.

Примечание: при последовательном опросе всех 8 каналов АЦП, это время пропорционально делится между всеми входами и составляет всего около 1,5 кГц в расчете на один вход.

Отсчет этих (хотя строго говоря, и всех других) интервалов времени производится аппаратно самим модулем АЦП путем подсчета определенного числа тактовых импульсов ТOSC. С помощью битов ADCS1, ADCS0 регистра ADCON0 (см. Таблицу №10) можно задавать требуемое число этих импульсов: либо 8, ли-

бо 32. Выбор именно таких |

|

|

|

|

|

|

|

|

|

значений связан с тем, что в |

|

|

Табл. № 10 |

|

контроллере TTF 5.0 ТOSC = |

|

|

|

|

|

ADCS1 : ADCS0 |

TAD (при ТOSC = 0,25 мкс) |

|

|

0,25 мкс, а следовательно |

|

|

||

только в этих случаях вре- |

|

|

8 ТOSC = 2 мкс |

|

|

0 : 1 |

|

||

мя преобразования полу- |

|

|

||

|

|

|

|

|

чится ≥ 1, 6 мкс как того |

|

1 : 0 |

32 ТOSC = 8 мкс |

|

требует документация на |

|

|

|

|

|

|

|

|

|

микроконтроллер. |

|

|

|

|

|

|

|

|

|

Внимание: установка других значений битов ADCS1, ADCS0 – ЗАПРЕЩЕНА, поскольку приводит к некорректной работе АЦП м/к PIC 16F877 (за счет очень высокой частоты кварца, АЦП будет «не успевать» обрабатывать аналоговый сигнал, например, за время 2 ТOSC).

14.2.2 Назначение и состав управляющих регистров АЦП

За настройку, конфигурирование и управление работой модуля АЦП контроллера отвечает группа из 5 специальных регистров, перечень которых приведен на рис. 130. Их функциональное назначение также указано на этом рисунке,

|

|

|

|

модуль АЦП |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

ADRESH |

|

ADRESL |

|

|

ADCON0 |

|

ADCON1 |

|

TRISA, E |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

хранениемладшей части разрядноготи-10 результата преобразованияU |

устанавливает- T |

выбираетномер входа запускаетначало преобразования выкл/вкл-модуль АЦП |

выбираетформат размерезультатащения в регистADRES0,1рах конфигурируетрежимы контактовработы портов A/D |

|

управляетнаправлением контактоввых/вх порта |

||

хранениестаршей части разрядноготи-10 результата преобразованияU |

|

|

||||||||

|

вх |

|

вх |

|

AD |

|

|

|

|

|

Рис. 130 Состав и назначение специальных регистров, управляющих работой модуля АЦП контроллера PIC 16F877

а назначение отдельных битов будет рассмотрено ниже. Следует обратить внимание на то, что в контроллере TTF 5.0 в силу его аппаратной структуры, дос-

тупными |

являются лишь |

|

|

|

|

|

|

||||

|

|

|

|

|

|

||||||

приводимыеные |

значения |

|

|

|

|

|

|

||||

отдельных битов этих ре- |

|

|

|

|

|

|

|||||

гистров. |

|

|

|

|

|

|

|

|

|

|

|

|

Пара |

регистров |

|

|

|

|

|

|

|

||

ADRESH |

(0х1Е) |

и |

|

|

|

|

|

|

|

||

ADRESL (0х9Е) предна- |

|

|

|

|

|

|

|||||

значены для размещения и |

|

|

|

|

|

|

|||||

хранения «10-bit Result» |

|

|

|

|

|

|

|||||

10-ти разрядного резуль- |

|

|

|

|

|

|

|||||

|

правое выравнивание |

|

левое выравнивание |

|

|

||||||

тата «оцифровки» текуще- |

|

|

|

|

|||||||

го мгновенного |

значения |

|

|

|

|

|

|

||||

|

Рис. 131 Форматы представления выходного |

|

|||||||||

входного |

напряжения. |

В |

|

|

|||||||

|

кода АЦП в регистрах ADRESH и L |

|

|||||||||

зависимости от |

значения |

|

|

||||||||

|

|

|

|

|

|

||||||

бита ADFM регистра AD- |

|

|

|

|

|

|

|||||

|

|

|

|

|

|

||||||

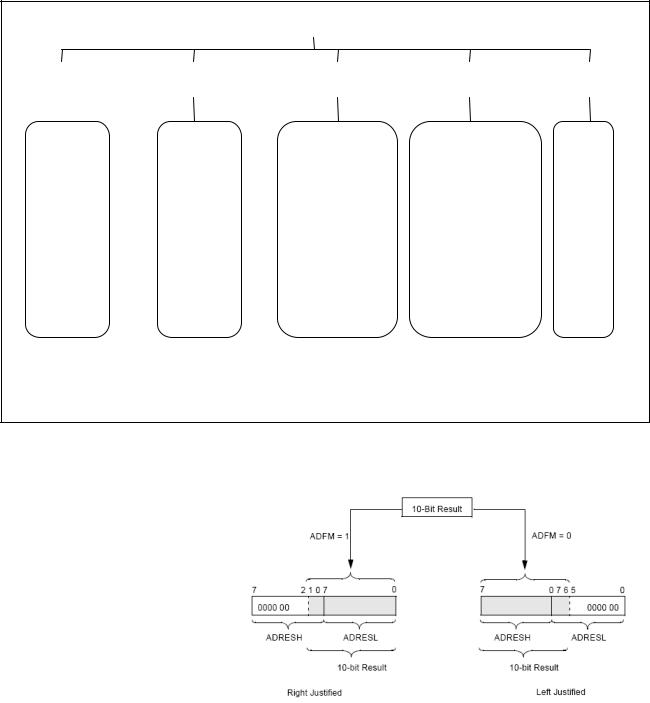

CON1 эти 10 бит могут располагаться в двух 8-и разрядных регистрах ADRESH, |

|||||||||||

ADRESL одним из следующих способов (рис. 131). Этот факт необходимо учи- |

|||||||||||

тывать и «отбрасывать» 6 незначащих нулей в одном из регистров ADRES при |

|||||||||||

переводе двоичного результата в десятичное значение напряжения. Очевидно, что более «привычным» является режим правого выравнивания, когда 6 старших бит регистра ADRESH равны 0.

Регистр ADCON0 (0х1F), назначение бит приведено на рис. 132. Кроме ограничений на выбор времени преобразования одного бита TAD битами ADSC1-

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

|

|

|

|

|

|

ADSC1 |

ADSC0 |

CHS2 |

CHS1 |

CHS0 |

GO/DONE |

x |

ADON |

|

|

|

|

|

|

|

|

|

Биты выбора |

|

|

Биты выбо- |

|

|

|

TAD |

|

|

ра номера |

|

|

|

|

|

канала АЦП |

0 |

1 |

= 8ТOSC |

1 |

0 |

1 = RE0/AN5 |

1 |

0 |

= 32ТOSC |

1 |

1 |

0 = RE1/AN6 |

|

|

|

1 |

1 |

1 = RE2/AN7 |

x – бит не используется

Бит статуса модуля АЦП

при ADON = 1

1 – модуль АЦП выполняет преобразование (установка бита вызывает начало преобразования); 0 – состояние ожидания

(контроллер сбрасывает бит по окончании преобразования)

Бит включения модуля АЦП

1 = Вкл

0 = Выкл

Другие комбинации бит – ЗАПРЕЩЕНЫ !

Рис. 132 Назначение бит регистра ADCON0 (0x1F) с учетом ограничений контроллера TTF 5.0

А Ц П

|

|

Порт |

Назначение |

|||

|

|

|

|

|

|

|

|

|

RA0 |

Цифровой вход №1 |

|||

|

|

|

|

|

|

|

|

|

RA1 |

Цифровой вход №2 |

|||

|

|

|

|

|

|

|

|

|

RA2 |

Цифровой вход №3 |

|||

|

|

|

|

|

|

|

|

|

RA3 |

Цифровой вход №4 |

|||

|

|

|

|

|

|

|

|

|

RA5 |

Цифровой вход №6 |

|||

опорное |

|

|

Аналоговый вход №1 |

|||

RЕ0 |

||||||

напряжение |

||||||

|

|

|

|

|||

|

|

RЕ1 |

Аналоговый вход №2 |

|||

|

|

|

|

Аналоговый вход №3 |

||

|

|

RЕ2 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

TTF 5.0 |

|

|

Рис. 133 Соответствие входов АЦП микроконтроллера 16F877 и реальных сигналов на них в контроллере TTF 5.0

ADSC0 (см. Табл. № 10) при установке бит этого регистра необходимо учиты-

вать ограничения на используемые комбинации бит связанные с тем, что в

|

|

7 |

|

6 |

5 |

|

4 |

|

|

3 |

|

2 |

|

1 |

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PCFG0 |

|

|

|

|

ADFM |

|

x |

x |

|

x |

|

PCFG3 |

|

PCFG2 |

|

PCFG1 |

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

- |

|

|

Бит формата сохранения |

|

|

Биты установки режимов работы контактов |

|||||||||||||||

|

|

10-ти разрядного |

|

|

|

|

|

|

|

модуля АЦП |

|

|

|

|||||

|

|

результата (рис. Ф) |

|

|

|

|

|

|

|

|

|

|

|

|

||||

1 |

- правое выравнивание, |

6 |

|

0 0 |

0 0 |

- при этом контакты RE0, RE1, |

||||||||||||

|

RE2 |

становятся аналоговыми |

входами, а |

|||||||||||||||

старших |

бит |

регистра |

||||||||||||||||

величина источника опорного напряжения |

||||||||||||||||||

ADRESH читаются как «0»; |

|

|

||||||||||||||||

|

|

Еоп = +5 В |

|

|

|

|

|

|

|

|||||||||

0 |

- левое |

выравнивание, |

6 |

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||

младших |

бит |

регистра |

x – бит не используется |

|

|

|

|

|||||||||||

ADRESL читаются как «0»; |

|

|

|

|

|

|

|

|

|

|

|

|

||||||

Другие комбинации бит при работе с АЦП – ЗАПРЕЩЕНЫ !

Рис. 134 Назначение бит регистра ADCON1 (0x9F) с учетом ограничений контроллера TTF 5.0

контроллере TTF 5.0 из 8 аналоговых входов (рис. 133) микросхемы 16F877 доступны лишь три: RE0, 1,

2. На остальные 5 контак- |

|

|

|

|

|

|||||

тов (RA0 – RA5) микро- |

|

|

|

|

|

|||||

схемы, которые хотя и мо- |

|

|

|

|

|

|||||

|

|

|

|

|

||||||

гут быть запрограммиро- |

|

|

|

|

|

|||||

ваны как аналоговые вхо- |

|

|

|

|

|

|||||

ды, жестко аппаратно уже |

|

|

|

|

|

|||||

|

|

|

|

|

||||||

поданы |

цифровые сигна- |

|

|

|

|

|

||||

|

|

|

|

|

||||||

лы. Попытка их перепро- |

|

|

|

|

|

|||||

граммирования |

на прием |

|

|

|

|

|

||||

аналогового сигнала, |

хотя |

|

|

|

|

|

||||

логически и возможна, но |

|

|

|

|

|

|||||

на практике приведет к |

|

|

|

|

|

|||||

тому, что на вход АЦП |

|

|

|

- запрещенные комбинации |

||||||

|

|

|

|

|

||||||

подключится |

воздейст- |

|

|

PCFG3 – PCFG0 = 0000 |

||||||

вующие на эти контакты |

|

|

||||||||

|

|

PCFG3 – PCFG0 = 011х |

||||||||

постоянные входные |

на- |

|

|

|||||||

|

|

|

|

|

||||||

пряжения. |

|

|

|

|

Рис. 135 Разрешенные комбинации бит PCFG3 |

|||||

|

Регистр |

ADCON1 |

|

|

|

– PCFG0 регистра ADCON1 |

||||

(0x9F), |

назначение |

бит |

|

|

|

|

|

|||

|

|

|

|

|

||||||