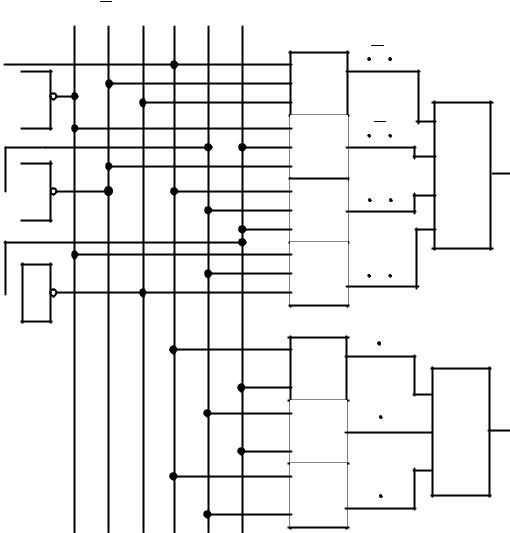

ai bi ci ai bi ci

ai  1 bi

1 bi  1

1

ci  1

1

& |

ai bi ci |

|

|

|

|

& |

ai bi ci |

1 |

|

||

|

|

si |

& |

ai bi ci |

|

& |

ai bi ci |

|

|

|

|

& |

ai ci |

|

|

|

|

|

|

1 |

& |

bi ci |

ci+1 |

|

||

|

|

|

& |

ai bi |

|

|

|

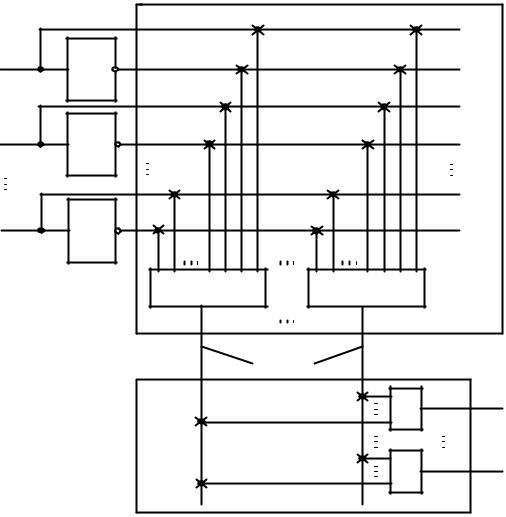

Рисунок 2.22 – Логическая схема ОДС

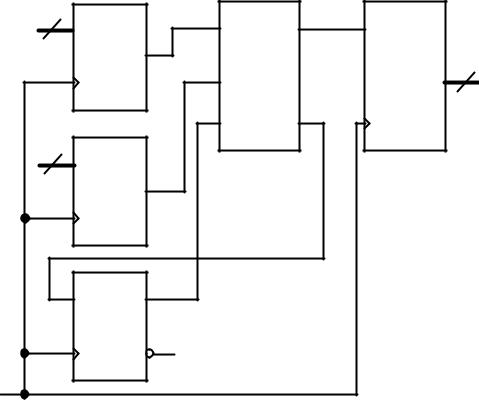

Операция суммирования во всех разрядах слагаемых осуществляется с помощью одного и того же ОДС. С первым тактовым импульсом (ТИ) на входы ОДС поступают из регистров 1 и 2 цифры первого разряда слагаемых a0 и b0, а из D-триггера на вход СI подается нулевой сигнал. Суммируя поданные на входы цифры, ОДС формирует первый разряд суммы s0, выдаваемый на вход регистра 3, и перенос c1, принимаемый в D-триггер. Второй ТИ осуществляет в регистрах сдвиг на один разряд вправо, при этом на входы ОДС подаются цифры второго разряда слагаемых a1, b1 и c1. Получающаяся цифра второго разряда суммы s1 вдвигается в регистр 3, перенос c2 принимается в D-триггер и т. д.

Достоинством МДС последовательного действия является малый объем оборудования, требуемый для его построения, а недостатком – низкое быстродействие, так как время суммирования TSM пропорционально разрядности слагаемых.

111

n |

DSRG |

A SM S si |

DSRG |

|

|

|

ai |

|

n |

|

|

|

|

|

|

C |

B |

|

|

|

1 |

|

CO ci+1 |

|

|

|

CI |

C |

|

n |

SRG |

|

|

3 |

|

|

|

||

|

D |

bi |

|

|

|

|

|

|

|

|

C |

|

|

|

|

2 |

|

|

|

|

D T |

ci |

|

|

|

C |

|

|

|

TИ |

|

|

|

|

Рисунок 2.23 – Логическая схема МДС последовательного действия |

||||

МДС параллельного действия в зависимости от способа передачи переносов от младших разрядов в старшие могут быть двух типов:

–с последовательным переносом;

–с параллельным (ускоренным) переносом.

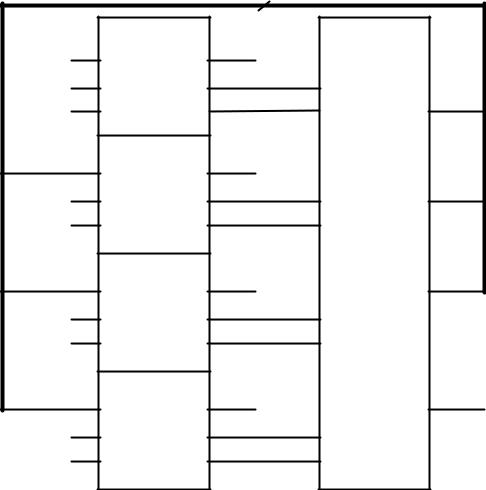

Логическая схема МДС параллельного действия с последовательным переносом (рисунок 2.24) состоит из отдельных разрядов, каждый из которых содержит ОДС.

При подаче слагаемых цифры их разрядов поступают на соответствующие ОДС. Каждый из ОДС формирует на своих выходах цифру соответствующего разряда суммы и перенос в соседний старший разряд. Сигнал переноса в каждом разряде формируется после того, как будет сформирован и передан сигнал переноса из предыдущего разряда.

В худшем случае, возникший в младшем разряде перенос может последовательно вызывать переносы во всех остальных разрядах. При этом время передачи переносов TC = n tC ОДС, где tC ОДС – задержка распространения переноса в одном разряде. Таким образом, последовательный перенос в МДС параллельного действия не обеспечивает высокое быстродействие.

112

an-1 |

|

|

|

|

A |

SM |

S |

|

|

|

|

|

Sn-1 |

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

||||||||

bn-1 |

|

|

|

B |

|

CO |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

CI |

n |

|

|

|

|

|

Cn |

||

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

a1 |

|

|

|

|

A |

SM |

S |

|

|

|

|

|

S1 |

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|||||||

b1 |

|

|

B |

|

|

|

|

|

|

|

C2 |

|

||

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

CI |

|

CO |

|

|

|

|

|

|

|

|

|

|

|

|

2 |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

a0 |

|

|

|

|

A |

SM |

S |

|

|

|

|

|

S0 |

|

|

|

|

|

|

|

|

|

|||||||

b0 |

|

|

B |

|

|

|

|

|

|

|

C1 |

|||

|

|

|

|

|

|

|

|

|

||||||

c 0 |

|

|

|

|

CI |

|

CO |

|

|

|

|

|

||

|

|

1 |

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рисунок 2.24 – Логическая схема МДС параллельного действия с последовательным переносом

Для обеспечения высокого быстродействия в МДС параллельного действия сигналы переносов формируются одновременно для всех разрядов с помощью блока ускоренного переноса. На рисунке 2.25 показана функциональная схема четырехразрядной секции МДС параллельного действия с параллельным переносом.

При этом разрядные сумматоры не содержат цепей формирования переносов, они формируют только сумму si и функции Gi, Pi, для получения которых переносы не требуются. Эти вспомогательные функции генерации переноса Gi = ai ∙ bi и распространения переноса Pi = ai v bi необходимы для формирования переносов в блоке ускоренного переноса GRP (рисунок 2.25).

Исходя из этого, выражение (2.15) можно представить в следующем виде:

Ci+1 = ai ∙ bi ˅ ci ∙ (ai ˅ bi) = Gi ˅ Pi ∙ ci. |

(2.16) |

113

|

|

|

3 |

|

|

|

|

|

SM |

|

|

GRP |

|

|

|

|

|

|

||

c0 |

CI |

S |

|

s0 |

|

|

a0 |

A |

P |

P0 |

P0 |

1 |

|

G0 |

||||||

|

|

|

|

|||

b0 |

B |

G |

G0 |

С1 |

||

|

||||||

1 |

|

SM |

|

|

|

|

CI |

S |

|

s1 |

|

||

|

P1 |

2 |

||||

|

|

|

|

|||

a1 |

A |

P |

P1 |

С2 |

||

G1 |

||||||

b1 |

B |

G |

G1 |

|

||

|

|

|||||

2 |

|

SM |

|

|

3 |

|

|

|

|

|

|||

|

CI |

S |

|

s2 |

С3 |

|

|

P2 |

|

||||

a2 |

A |

P |

P2 |

|

||

G2 |

|

|||||

b2 |

B |

G |

G2 |

|

||

|

|

|||||

3 |

|

SM |

|

|

|

|

CI |

S |

|

s3 |

С4 |

||

|

|

|||||

|

|

|

||||

a3 |

A |

P |

P3 |

P3 |

|

|

G3 |

|

|||||

b3 |

B |

G |

G3 |

|

||

|

|

|||||

Рисунок 2.25 – Функциональная схема четырехразрядной секции сумматора с ускоренным |

||||||

|

|

(параллельным) переносом |

|

|||

Из выражения (2.16) следует, что сигнал переноса на выходе i-го разряда генерируется самим разрядом (Gi = 1) при ai = bi =1 независимо от результата переноса из соседнего младшего разряда. Следовательно, можно передавать сигнал переноса для обработки старших разрядов, не дожидаясь окончания формирования переносов из младших разрядов. Однако, если только один из сигналов ai, bi равен единице, то перенос в следующий разряд будет иметь место только при наличии переноса из предыдущего разряда (Pi = 1, ci = 1). Таким образом, сигналы переноса в каждом разряде формируются одновременно в соответствии с выражением (2.16).

2.1.9Программируемые логические структуры

Впоследнее время все более широкое распространение получают различные программируемые логические структуры, которые можно разделить на про-

граммируемые логические матрицы (ПЛМ), программируемые матрицы логики

114

(ПМЛ) и базовые матричные кристаллы (БМК). Причем ПЛМ и ПМЛ являются наиболее простыми схемами с программируемой структурой. Дальнейшее развитие этого направления привело к разработке БМК, уровень интеграции которых достиг миллионов вентилей на кристалле. Кроме того, в последние годы появился новый тип логических микросхем – перепрограммируемые логические интегральные схемы (ПЛИС). Эти микросхемы обеспечивают разработчику цифровых устройств все преимущества использования стандартного БМК, добавляя при этом гибкость и значительное сокращение времени проектирования. Особенностями ПЛИС являются: значительный объем ресурсов (до 10 млн. вентилей на кристалл); высокая производительность (до 420 МГц); высокая гибкость архитектуры с множеством системных особенностей (внутреннее ОЗУ, логика ускоренного переноса, встроенные блоки умножителей, наличие порядка ста тысяч триггеров и сдвиговых регистров); низкое энергопотребление; возможность использования развитых и недорогих средств проектирования и др.

Программируемая логическая матрица характеризуется простотой получе-

ния необходимых функций. Основой ПЛМ служат последовательно включенные программируемые матрицы элементов И и ИЛИ (рисунок 2.26).

x1 |

|

|

x1 |

|

|

|

|

|

|

|

|

|

||

|

|

M И |

t1 |

MИЛИ |

F1 |

|

F1 или F1 |

|||||||

|

|

|

|

|

|

|||||||||

|

БВх |

|

x1 |

БВых |

||||||||||

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

xm |

(M1) |

|

|

|

|

|

|

|

||

xm |

|

|

t k |

(M2) |

Fn |

|

Fn или Fn |

|||||||

|

xm |

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

OE |

|

|

|

|

|

|

|

|

OE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рисунок 2.26 – Базовая структура ПЛМ

В ПЛМ также входят блоки входных и выходных буферных каскадов (БВх и БВых). Входные буферы преобразуют однофазные входные сигналы в парафазные и формируют сигналы необходимой мощности для матрицы элементов И. Выходные буферы обеспечивают необходимую нагрузочную способность выходов, разрешают или запрещают выход ПЛМ на внешние шины с помощью сигнала OE, а нередко выполняют и более сложные действия. Выпускаются ПЛМ на основе как биполярной, так и МОП-технологии.

Основными параметрами ПЛМ являются число входов m, число термов k

и число выходов n. Под термом понимается конъюнкция, связывающая входные аргументы, представленные в прямой или инверсной формах.

115

Схема ПЛМ на вентильном уровне показана на рисунке 2.27. Крестики в пересечениях горизонтальных и вертикальных линий обозначают программируемые точки связей (ПТС).

|

Матрица элементов И |

|

|

1 |

|

|

|

x1 |

|

|

|

1 |

|

|

|

x2 |

|

|

|

1 |

|

|

|

xm |

|

|

|

& |

& |

|

|

t1 |

|

tk |

|

|

термы |

|

|

|

Матрица |

1 |

F1 |

|

элементов ИЛИ |

||

|

|

|

|

1 |

Fn |

Рисунок 2.27 – Схема ПЛМ на вентильном уровне

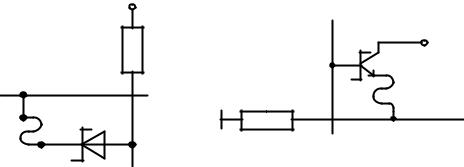

В первой ситуации незапрограммированная ПЛМ имеет соединения во всех пересечениях, а при ее программировании часть соединений удаляется. Как видно из схемы, в этом случае в исходном состоянии все термы и функции независимо от входных переменных имеют нулевые значения, так как на входы схем И подаются одновременно прямые и инверсные значения аргументов, а Xi ∙ X̅i = 0. Элементами связей в матрице И служат диоды, соединяющие горизонтальные и вертикальные шины, как показано на рисунке 2.28, а, изображающем цепи выработки терма ti.

До программирования все перемычки целы и диоды размещены во всех узлах матрицы И. При программировании в схеме оставляют только необходимые элементы связи, а ненужные устраняются пережиганием перемычек. Вы-

116

сокий уровень на выходе конъюнктора (рисунок 2.27) появится при наличии высоких напряжений на всех входах (все диоды заперты). Если же хотя бы на одном входе низкий уровень напряжения, то фиксируется низкий уровень напряжения (диод открыт).

Элементами связи в матрице ИЛИ служат транзисторы (рисунок 2.28,б), включенные по схеме эмиттерного повторителя относительно линий термов и образующие схему ИЛИ относительно горизонтальной линии выхода ПЛМ. В данном случае схема ИЛИ реализована за счет параллельного соединения эмиттерных повторителей.

При изображении запрограммированных матриц наличие элементов связей (целые перемычки) отмечается точкой в соответствующем узле.

U П |

|

|

R |

t i |

U П |

|

R |

Fi |

|

|

|

t i |

|

|

а) |

|

б) |

Рисунок 2.28 – ПЛМ схемотехники ТТЛШ. Элементы связей в матрицах И (а) и ИЛИ (б)

Во второй ситуации все соединения отсутствуют, входные сигналы в схему не поступают. Значения термов и функций определяются внутренними цепями ПЛМ, как правило, они единичны. При программировании формируются необходимые термы, из которых и составляются требуемые функции.

Переменные x1, x2, …, xm подаются через БВх (рисунок 2.26) на входы элементов И. В матрице И формируются термы, число которых равно числу конъюнкторов, т. е. числу выходов матрицы И. Далее термы подаются на входы матрицы ИЛИ, т. е. на входы дизъюнкторов, формирующих выходные функции. Число дизъюнкторов равно числу вырабатываемых функций n.

Таким образом, ПЛМ реализует ДНФ воспроизводимых функций. ПЛМ спо-

собна реализовать систему n логических функций от m аргументов, содержащую не более k термов, т. е. представляет собой усеченное ПЗУ.

Например, однократно программируемая БИС ПЛМ К556РТ1 выполнена по схемотехнике ТТЛШ. Эта микросхема реализует восемь функций от шестна-

117

дцати переменных, общее число конъюнкций (термов) для всех функций не должно превышать 48.

В программируемых матрицах логики по сравнению с ПЛМ программиру-

ются только термы, т. е. конъюнкции переменных для СДНФ. Элементы ИЛИ зафиксированы и имеют, как правило, семь-восемь входов.

Контрольные вопросы и задачи к теме 2.1

Смотри в [1].

118

Тема 2.2 Триггерные устройства

2.2.1 Общие сведения о триггерах

Триггером называется ПЦУ, имеющее два устойчивых состояния и способное под действием управляющих сигналов скачкообразно переходить из одного состояние в другое.

Одно состояние называется единичным, а второе – нулевым. В общем случае триггер имеет два выхода: прямой Q и инверсный Q̅, поскольку логическое состояние одного выхода всегда инверсно логическому состоянию другого. Состояние триггера определяется логическим уровнем на прямом выходе. Если, например, на прямом выходе высокий уровень, соответствующий лог. 1, то триггер находится в единичном состоянии или установлен (при этом на инверсном выходе уровень, соответствующий лог. 0). Если на прямом выходе низкий уровень, соответствующий лог. 0, то триггер находится в нулевом состоянии или сброшен (и при этом уровень на инверсном выходе соответствует лог. 1).

Триггеры классифицируются по функциональному признаку и способу записи информации.

По функциональному признаку, т. е. по виду характеристического уравнения, связывающего логические переменные на входах и выходах триггера в момент срабатывания tn и после срабатывания tn+1, различают RS-, D-, T-, JK-триггеры и др.

По способу записи информации триггеры делятся на асинхронные (не тактируемые) и синхронные (тактируемые). В асинхронных триггерах запись информации происходит под действием изменений входных сигналов с момента подачи их на информационные входы. В синхронных триггерах запись информации происходит только при подаче сигнала синхронизации.

Синхронные триггеры в свою очередь подразделяются на три категории в зависимости от того, какие параметры синхросигнала используются для записи информации:

-со статическим управлением (тактируемые уровнем);

-двухступенчатые, управляемые синхроимпульсом;

-с динамическим управлением (тактируемые фронтом);

119

Синхронный триггер со статическим управлением воспринимает инфор-

мационные сигналы, когда синхросигнал достигает своего активного уровня. Характерной особенностью этого типа триггеров является то, что смена информационного сигнала в течение времени действия импульса синхронизации вызывает новое срабатывание триггеров, т. е. синхронные триггеры со статическим управлением при активном уровне синхросигнала ведут себя подобно асинхронным. При окончании действия синхроимпульса триггер «защелкивает» последнее значение информационного сигнала, т. е. переходит в режим хранения.

Асинхронные триггеры и синхронные триггеры со статическим управлением имеют ограниченное применение. Например, эти триггеры не могут использоваться в счетчиках или регистрах сдвига. В зарубежной литературе такие триггеры относятся к Latch типу (от англ. Latch – защелка). Двухступенчатые триггеры, управляемые импульсом, и триггеры с динамическим управлением являются более универсальными и относятся к FF типу (от англ. Flip-Flop).

Двухступенчатые триггеры, управляемые импульсом, воспринимают информационные сигналы, когда синхросигнал изменяет свое состояние с низкого на высокое, а затем снова на низкое, т. е. управляются импульсом. В двухступенчатых триггерах переход в новое состояние происходит после окончания действия синхроимпульса, т. е. при низком уровне на входе синхронизации С.

Синхронный триггер с динамическим управлением воспринимает инфор-

мационные сигналы только в момент действия положительного перехода (переход 0 1 = ↑) или в момент действия отрицательного перехода (переход от 1 0 = ↓) синхроимпульса. Вход триггера C называется прямым динамическим, если переключение триггера осуществляется положительным перепадом импульса синхронизации. Если же переключение триггера осуществляется отрицательным перепадом импульса синхронизации, то вход триггера С называется инверсным динамическим. Характерной особенностью триггеров с динамическим управлением является то, что в остальное время импульса синхронизации триггер не реагирует на информационные сигналы и остается в предыдущем состоянии независимо от уровня синхросигнала.

В таблице 2.7 показаны УГО различных типов входов синхронизации С в синхронных триггерах, а также временные диаграммы процессов переключения.

120