Розробити АП, що виконує базову операцію алгоритму ШПФ за основою 4 з проріджуванням за часом. Час виконання базової операції Тб о≤ 200 нс., час передачі даних по магістралі τ м =Тб о . Розрядність чисел при роботі з фіксованою крапкою 40 (20 розрядів - дійсна частина числа і 20 розрядів - уявна), з поблочно-плаваючою крапкою 26 (13 розрядів - дійсна частина числа і 13 розрядів - уявна), з гібридною плаваючою крапкою 20 (8 розрядів - дійсна частина, 8 розрядів – уявна, 4 розрядів – порядок числа). Критерій якості - мінімальна кількість використаних блоків і вузлів.

Алгоритм базової операції ШПФ за основою 4 і проріджування за часом можна представити у вигляді

А'1 = А1 + A2W1 + A3W2 + A4W3 = (А1 + A3W2) + (A2W1 + A4W3),

A'2

= A1

![]() jA2W1

– A3W2

±

jA4W3

= (A1

– A3W2

)

jA2W1

– A3W2

±

jA4W3

= (A1

– A3W2

)

![]() j(A2W1

- A4W3

),

j(A2W1

- A4W3

),

A'3 = A1 - A2W1 + A3W2 - A4W3 = (A1 + A3W2) - (A2W1 + A4W3),

A'4

= A1

±

jA2W1

– A3W2

![]() jA4W3

= (A1

- A3W2)

± j(A2W1

- A4W3),

jA4W3

= (A1

- A3W2)

± j(A2W1

- A4W3),

де A'1, A'2, А'з, А'4 - результати базової операції; А1, А2, А3, А4 - вхідні відліки; W1, W2, W3 - комплексні коефіцієнти; j - уявна одиниця, верхній знак перед j відповідає прямому, нижній - оберненому ШПФ.

Re A'1 = [ReА1 + (ReA2 ReW2 - 1mA3 ImW2)] + [(ReA2 ReW1 - ImA2 ImW1) +

+ (ReA4 ReW3 – ImA4ImW3)],

1m A'1 = [1m A1 + (Re A3 Im W2 + ImA3 Re W2}] + [(Re A2 Im W1 + 1m A2 Re W1) +

+ (Re A4 Im W3 + Im A4 Re W3)],

Rе A'2 = [Re A1 - (Re A3 Re W2 - Im A3 Im W2)] ± [(Re A2 Im W1 + Im A2 Re W1) –

- (Re A4 1m W3 + Im A4 Re W3)],

Im

A'2

= [Im A1

- (Re A3

Im

W2

+ Im A3

Re W2)]

![]() [(Re A2

Re W1

- Im A2

Im W1)

-

[(Re A2

Re W1

- Im A2

Im W1)

-

- (Re A4 Re W3 - Im A4 Im W3)],

Re A'3 = [Re A1 + (Re A3 Re W2 - Im A3 Im W2)] - [(Re A2 Re W1 - Im A2 Im W1) +

+ (Re A4 Re W3 - Im A4 Im W3)],

Іm A'3 = [Іm A1 + (Re A3 Im W2 + Im A3 Re W2)] - [(Re A2 Im W1 + Im A2 Re W1) +

+ (ReA4 lmW3+ Im A4 ReW3)],

Re

A'4

=

[ReA1

- (ReA3

ReW2

– ImA3

Im W2)]

![]() [(Re A2

Im W1

+ Ima2

Re W1)

–

[(Re A2

Im W1

+ Ima2

Re W1)

–

- (ReA4ReW3 —ImA4 ReW3)],

Im A'4 = [Im A3 - (Re A3 Im W2 + Im A3 Re W2)] ± [(Re A2 Re W1 - Im A2 Im W1) –

- (ReA4ReW3 –ImA4 ImW3)]

Для виконання базової операції вимагається виконати 12 операцій множення і 22 додавання. Для чисел з фіксованою крапкою до основних операцій алгоритму базової операції ШПФ за основою 4 добавляються 12 операцій округлення дійсних добутків і 8 операцій округлення результатів виконання базової операції. Швидкодія помножувача τy = 250 н.с суматора τс л = 275 нс. Кількість елементарних операцій множення Nэ о у = 12 додавання Nє о с л =42.

Мінімальна необхідна кількість помножувачів ny і суматорів nс л дорівнює:

![]() ,

,

![]() .

.

Для визначення періоду тактової частоти складемо таку систему нерівностей:

![]() ,

,

![]() .

.

Підставляючи значення τу, τм, τся, Nэо сл , nу = 15, ncл = 58, отримуємо наступну систему нерівностей:

1,25bм ≤ by ≤ 1,25 bм, 1,375bм≤ bсл ≤1,38bм.

Мінімальне значення bм, що задовольняє останнім нерівностям, рівно 100, і отже, період тактової частоти Тбо / bм =2 нс. Для збільшення Тт потрібно збільшити кількість АФУ. Перебір різних поєднань числа помножувачів і суматорів у пошуках варіанту, що враховує реальні можливі елементної бази і забезпечує як найкращий показник якості, - дуже трудомістка робота. Можна рекомендувати вибрати кількість помножувачів і суматорів кратним кількості операцій відповідно множення АП. Узявши nсл = 84, ny = 24, отримаємо

1,25bм ≤2bм, 1,375bм ≤ bсл ≤ 2bм.

Мінімальне значення bм рівне1, і період тактової частоти Тт = Тбо; by=bсл=2, отже, Ту = Тсл=2Тбо.

|

Номер базової операції |

Номер ітерації |

||||

|

1 |

2 |

3 |

4 |

5 |

|

|

1

2

. . . . 31

32 |

000000 100000 000001 100001 . . . . 011110 111110 011111 111111 |

000000 010000 000001 010001 . . . . 101110 111110 101111 111111 |

000000 001000 000001 001001 . . . . 110110 111110 110111 111111 |

000000 000010 000001 000011 . . . . 111100 111110 111101 111111 |

000000 000001 000010 000011 . . . . . 111100 111101 111110 111111 |

зливаються в ті ж елементи пам'яті, з яких прочитувалися початкові для даної базової операції операнди.

Відомо багато різновидів алгоритмів БПФ [8]. Аналіз алгоритмів показує, що обчислення БПФ розділяються на ряд ітерацій, число ітерацій logrN. Нз кожній ітерації виконується N/r базових операцій, в яких беруть участь всі N відліків, розбитих на N/r груп по r відліків в кожній. Так, в базових операціях 1-й ітерації беруть участь групи з r відліків, віддалених друг від друга на N/r відліків. На 2-й ітерації в базових операціях беруть участь групи відліків, віддалених друг від друга на N/r2 відліків, і т. д. На останній ітерації беруть участь групи r відліків, що поряд стоять.

Якщо представити номер відліку п числом з підставою r: n=kL-1rL-1+ . . .+k1r1+k0r0, (3.21)

де ki=0, 1, ..., r-l;i=0, 1, ..., L—1; A=IogrN, то коди групи відліків, що беруть участь в базовій операції на j-и ітерації (j = 1, 2 ..., L), виходять зміною коефіцієнта kL-i від 0 до r-1 в коді номера будь-якого відліку, інші розряди кодів співпадають. Значення кодів відліків, що беруть участь в різних базових операціях на j-й ітерації, будуть відрізнятися значеннями інших розрядів коду.

Для прикладу в табл. 3.1, 3.2 наведені групи відліків, що беруть участь в базових операціях при виконанні алгоритму БПФ з N=64 і підставами 2 і 4 відповідно. Номери відліків при г=2 представляються 6 - розрядними війковими кодами

n=k525+k424+k323+k222+k121+k020

де ki = 0, 1; i=0, ..., 5.

Номери відліків при г=4 представляються 3-розрядними четвертними кодами

n = k222 + k121 + k020

де ki=0, 1, 2, 3; i=0, I, 2.

|

Номер базової операції |

Номер ітерації |

||

|

1 |

2 |

3 |

|

|

k2k1k1(k5k3k3k2k1k0) |

k2k1k1(k5k3k3k2k1k0) |

k2k1k1(k5k3k3k2k1k0) |

|

|

1

2

. . .

15

16 |

000 (000000) 100 (010000) 200 (100000) 300 (110000) 001 (000001) 101 (010001) 201 (100001) 301 (110001) . . . 032 (001110) 132 (011110) 232 (101110) 332 (101110) 033 (001111) 133 (011111) 233 (101111) 333 (111111) |

000 (000000) 010 (000100) 020 (001000) 030 (001100) 001 (000001) 000 (000101) 021 (001001) 031 (001101) . . . . 302 (110010) 312 (110110) 322 (111010) 332 (111110) 303 (110011) 313 (110111) 323 (111011) 333 (111111) |

000 (000000) 001 (000001) 002(000010) 003 (000011) 010 (000100) 011 (000101) 012 (000110) 013 (000111) . . . . 320 (111000) 321 (111001) 322 (111010) 323 (111011) 330 (111100) 331 (111101) 332 (111110) 333 (111111) |

В табл. З.2 поряд із четвертинними кодами в дужках наведені їхні двійкові еквіваленти. Порядок виконання базових операцій на кожній ітерації може бути довільним.

Основна задача вузла управління – формування адрес прочитування операндів з ОЗУ і ПЗП коефіцієнтів поворотних множників і адрес запису результатів обчислень в ОЗУ. Алгоритм формування адрес ОЗУ залежить від алгоритму формування групи звітів, що беруть участь в базовій операції послідовності виконання базових операцій і структурної побудови ЦВ. При коефіцієнті розпаралелювання ОЗУ К=1 адреси зберігання операндів співпадають з їхніми номерами n (3.21) і алгоритм формування адрес прочитується з ОЗУ можна представити в наступним вигляді:

Асч (i) = rL-j( i mod r) + (i ÷ r) mod rL-j+ [rL-j+1 (i ÷ rL-j+1 )] mod N, (3.22)

де j=(i ÷ N)+1 - номер ітерації; i=0, 1, ..., (N(L - 1) - номер формованої адреси; r - основа БПФ; N - довжина БПФ; L=logr N — кількість ітерацій;

amod b-a по модулю b.

Алгоритм формування адрес запису Азп(i) результатів виконання базових операцій з Асч(i) з точністю до затримки в АУ: Aзп(i) =Асч(i-i0).

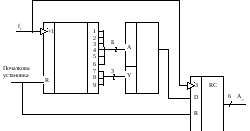

На мал. 3.12 наведена структурна схема вузла, що реалізує алгоритм (3.22) при r=2, N=64.

Для формування адрес прочитування використовуються розряди 1—6 лічильника. Перший розряд лічильника реализует функцію imod2. Множення 26-j(imod2) здійснює привласненням відповідної ваги розряду l лічильника у моормуючому адресі Асч. Так першому лічильнику не першійітерації при множенні 25(imod2) привласнюється вага розряду 6, на другій ітерації – розряду 5 і т. д. До розряду 1 на останній ітерації.

Р озряди

лічильника, починаючи з другого,

реализують функцію i÷2.

Обчислення по

алгоритму (i÷2)mod

26-j

реализується привласненням у формованій

адресі прочитування

відповідних терезів розрядам лічильника,

починаючи з другого. На

першій ітерації розрядам лічильника з

другого по шостий представляються вага

з першого по п'ятий відповідно. При

виконанні другої

ітерації розрядам лічильника з другого

по п'ятий привласнюються вага з першого

по четвертий і т д. На п'ятій ітерації

розряду 2 лічильника привласнюється

вага розряду 1. на шостій ітерації

значення

функції

(i÷2)

mod 1 рівне 0. Розряди 7 – 9 формують

номер ітерації без одиниці (j -1) і

реалізують функцію

(i÷64).

озряди

лічильника, починаючи з другого,

реализують функцію i÷2.

Обчислення по

алгоритму (i÷2)mod

26-j

реализується привласненням у формованій

адресі прочитування

відповідних терезів розрядам лічильника,

починаючи з другого. На

першій ітерації розрядам лічильника з

другого по шостий представляються вага

з першого по п'ятий відповідно. При

виконанні другої

ітерації розрядам лічильника з другого

по п'ятий привласнюються вага з першого

по четвертий і т д. На п'ятій ітерації

розряду 2 лічильника привласнюється

вага розряду 1. на шостій ітерації

значення

функції

(i÷2)

mod 1 рівне 0. Розряди 7 – 9 формують

номер ітерації без одиниці (j -1) і

реалізують функцію

(i÷64).

Обчислення по алгоритму [27-j(i÷27-j)] mod64 реалізується використанням відповідних розрядів лічильника. На 1-й ітерації значення функції [26(i÷26)] mod64 рівне 0. На 2-й ітерації розряд 6 лічильника є розрядом 6 адреси прочитування. На 3-й ітерації розряди 6 і 5 лічильника є розрядами 6 і 5 Асч відповідно і т, д. На шостій ітерації розряди лічильника з другого по шостий відповідають розрядам Асч також з другого по шостий.

Комутація розрядів лічильника залежно від номера ітерації здійснюється за допомогою мультиплексорів . в табл 3.3 наведені номери розрядів лічильника, що підключаються

Таблиця 3.3

|

Код управління |

Вихідні розряди мультиплексора |

|||||

|

6 |

5 |

4 |

3 |

2 |

1 |

|

|

000 001 010 011 100 101 |

1 6 6 6 6 6 |

6 1 5 5 5 5 |

5 5 1 4 4 4 |

4 4 4 1 3 3 |

3 3 3 3 1 2 |

2 2 2 2 2 1 |

До виходу мультиплексора залежно від коду управління (номер ітерації), що поступає з розрядів 7-9 лічильника. Початкова адреса формується установкою в 0 лічильника і вихідного регістра. По кожному тактовому імпульсу сформована адреса записується в регістр і тим самим формується наступна адреса прочитування. Реалізація структурної схеми рис 3.12 при використанні ІС серії 133 забезпечується трьома ІС 133ИЕ7, шістьма ІС 133КП5, однією ІС 133ИР13.

Для виконання кожної базової операції на АУ необхідно подати r-1 поворотний коефіцієнт Wp, де W==e-2jπ/N при прямому БПФ і W=e2jπ/N при зворотному БПФ. Для алгоритму БПФ з проріджуванням за часом значення р пов'язані з номерами відліків п з (3.21), беруть участь у виконанні базової операції на j-й ітерації, наступним співвідношенням:

де j=1 ..., r-1 - номер поворотного коефіцієнта, що бере участь в базовій операції; ki - розряди r-ого кода номерів операндів з (3.21).

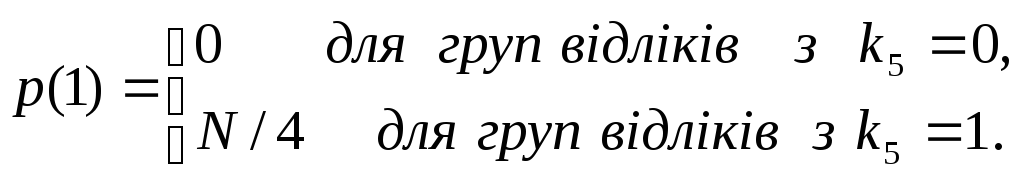

Наприклад, для N=64 і r=2 на 1-й ітерації значення р(1) для всіх груп відліків рівне 0, на 2-й ітерації р(1}=k524= =k5N/4, т. д.

На третій ітерації

і т д.

Алгоритм формування адрес ПЗП коефіцієнтів визначається алгоритмом виклику груп відліків і порядком розташування в ПЗП поворотних коефіцієнтів.

Для ПЗП з часом прочитування τсч<Тбо/r поворотні коефіцієнти можуть бути розташовані в порядку Wk, де k=0 ... ... .N-1 - адреса ПЗП. При виклику відліків з ОЗУ згідно (3.22) алгоритм формування адрес ПЗП

AСЧ ПЗУ(i)=rL-1(imodr)rij-1[Aсч(i)÷rL-j+1]

де j — номер ітерації; Асч(i) —адрес прочитування з ОЗУ; rila — r-чна інверсія l молодших розрядів r-ого кода а.

Таблиця 3.4

|

Код управління мультиплексором |

Розряди адрес прочитування ПЗП |

||||

|

5 |

4 |

3 |

2 |

1 |

|

|

000 001 010 011 100 101 |

0 6 5 4 3 2 |

0 0 6 5 4 3 |

0 0 0 6 5 4 |

0 0 0 0 6 5 |

0 0 0 0 0 6 |

Для ПЗП з часом прочитування τсч ≥ T6о /r и τсч < T6о необхідне розпаралелювання ПЗП. Тоді за однією адресою зберігаються Wk,W2k, ..., W(r-1)k. При виклику відліків з ОЗУ по алгоритму (3.22) алгоритм формування адрес ПЗП

![]() (3.23)

(3.23)

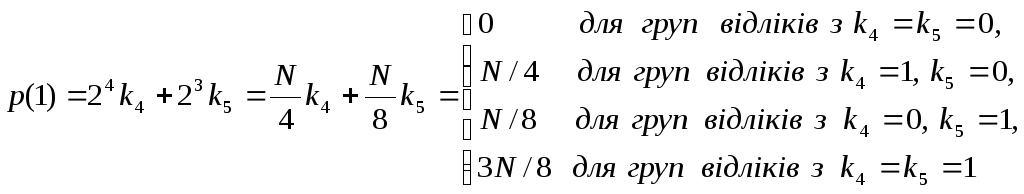

Спрощена структурна схема вузла, реализуємого алгоритму (3.23) для N=64 і г=2 наведена на мал. 3.13. Формування Асч ПЗУ (i) здійснюється комутацією розрядів Асч (i) згідно табл. 3.4. В таблиці показані розряди Асч , що підключаються до виходів мультиплексора, який реализуеться на п'яти ІС 133КП5.

Ф

Рис.

3.13 Спрощена структурна схема вузла

формування адреси читання з ПЗУ

коефіцієнтів повертаючих множників

при N=64, г=2, K=1

ФУ управління ОБПФ. Алгоритм ОБПФ відрізняється від алгоритму БПФ тільки значенням W, тому ФЕ управління ОБПФ аналогічний ФЕ управління БПФ. Для управління БПФ і ОБПФ може використовуватися один функціональний вузол.

Ф

Рис. 3.13 Упрощенная структурная схема

узла формирувания адреса считывания

из ПЗУ коэфициентов поворачивающих

множителей при N=64, г=2,

K=1

А1сч(i) = А2сч(i) = … =AKcч(i)=Al + i ÷ K,

де А1 — початкова адреса прочитування; К—коэффициент розпаралелювання ОЗУ.

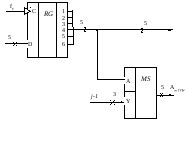

Вузол формування адрес прочитування ОЗУ реалізується двійковим лічильником і суматором. На мал. 3.14 наведена спрощена структурна схема для N=64, К=2. Реалізація структурної схеми мал. 3.14 забезпечується при використанні двох ІС 133ИЕ7 і по одній ІС 133ИМ2, 133ИМЗ, 133ИР13.

Порядок режимів роботи ЦВ залежить від вмісту інформації (команди управління)керівника, приходить на вузол управління ВУ. Послідовність режимів роботи ЦВ записується в ПЗП програм вузла управління ВУ. Залежно від команди, що прийшла, вибирається та область ПЗП програм, яка містить необхідну послідовність режимів, т. д. команда управління служить як би адресою осередку ПЗП, в якому зберігається 3-й з необхідної послідовності режимів. Після виконання чергового режиму адреса ПЗП програм збільшується на одиницю і встановлюється наступний режим роботи ЦВ і т. д.

Пристрій управління. Початковими даними для проектування пристрою управління однопроцесорного ЦВ є алгоритм обробки сигналів, структурна побудова і параметри вузлів ЦВ, елементна база.

Алгоритм обробки сигналів складається з наступних етапів (режимів) роботи ЦВ: запис вхідної інформації в ОЗУ, корекція вхідної інформації (включаючи вагову обробку), виконання обчислень по алгоритму БПФ, множення на частотну характеристику, ОБПФ, видача вихідній інформації.

В даному прикладі пристрій управління повинен формувати наступну інформацію.

1. Чотири адреси запису і прочитування інформації з ОЗУ (А1—А4), оскільки для прочитування будь-якого з 1024 комплексних чисел необхідна роздільна адресація кожної частини пам'яті, в якій зберігаються 256 комплексних чисел. Розрядність адрес А1, А2, А3, А4 рівна 8.

2. Імпульси запису в ОЗУ.

3. Імпульси запису в регістри СОЗУ1 і СОЗУ2. Для роздільного запису у вхідні регістри СОЗУ1 вимагається сформувати чотири імпульси на чотирьох шинах.

4. Коди управління мультиплексорами СОЗУ1 і СОЗУ2. Кожний мультиплексор має чотири виходи з незалежним управлінням. Для підключення до кожного виходу одного з чотирьох входів мультиплексора кожний з чотирьох кодів управління повинен мати два розряди.

5. Команду управління мультиплексорами СОЗУ1, забезпечуючу прийом з АУ або АЦП.

6. Адреса прочитування для ПЗП поворотних коефіцієнтів, розрядність адреси 9.

7. Тактові імпульси і імпульси запису у вихідні регістри ПЗП коректуючої функції і частотної характеристики в режимах корекції вхідної інформації і множення на частотну характеристику.

8. Команду установки одиничних коефіцієнтів на виході ПЗП коректуючої функції і частотної характеристики після завершення режимів корекції і множення на частотну характеристику.

Режим запису вхідної інформації в ОЗУ. Алгоритм запису вхідної інформації розглядався в § 3.3. У випадку г=4, К=4 алгоритм запису вхідної інформації доцільно, для спрощення роботи пристрою управління в подальших режимах, видозмінити відповідно до наступних виразів:

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

де А1ЗП, А2ЗП, А3ЗП, А4ЗП — адреси запису в ОЗУ при роздільному управлінні частинами розпаралелюючої пам'яті; КУпр1, КУпр2, КУпр3, КУпр4 - коди управління вихідними мультиплексорами СОЗУ1; i=0, 1, 2 ..., N—1 — номер відліку вхідної інформації;

÷ - цілочисельний діленян; а mod b — залишок від цілочисельного ділення а па b.

При коді управління вихідним мультиплексором, рівному 0, до виходу підключається перший вхід мультиплексора, при 1—другий, при 2 — третій, при 3 — четвертий.

Структурна схема вузла управління, що здійснює формування адрес ОЗУ і кодів управління мультиплексорами СОЗУ1, представлена на мал. 4.5. На вхід двійкового лічильника поступають імпульси супроводу вхідної інформації. Перед початком прийому поступає команда «Начальный установ». Дешифратор і схеми І формують імпульси записи у вхідні регістри СОЗУ1. Імпульси використовуються також для запису у вихідні регістри СОЗУ1.

При використанні ІС серії 133 наведена структурна схема може бути реалізована на трьох ІС 133ИЕ7, двох ИС133ИР13, однією ІС 133ЛИ1, однією ІС 133ИДЗ, однією ІС 133ЛП5.

М ал.

4.5. Структурна схема формування керуючих

сигналів однопроцесорного ЦВ з r=4,

K=4 в режимі

запису вхідної інформації.

ал.

4.5. Структурна схема формування керуючих

сигналів однопроцесорного ЦВ з r=4,

K=4 в режимі

запису вхідної інформації.

Алгоритм корекції вхідної інформації і множення на частотну характеристику (для зменшення часу обробки) суміщені з першими ітераціями відповідно БПФ і ОБПФ. Для виконання операцій множення в структурну схему однопроцесорного ЦВ введені додаткові помножувачі, як показано на мал. 4.3. При виконанні алгоритмів корекції вхідної інформації і множення на частотну характеристику пристрій управління повинен формувати на ПЗП коректуючої функції і частотної характеристики пачку з N/2 імпульсів. Після виконання алгоритмів (на ітераціях БПФ і ОБПФ, починаючи з другою) пристрій управління повинен встановлювати вихідні регістри ПЗП коректуючої функції і частотної характеристики в стан, відповідний подачі на додаткові помножувачі одиничних коефіцієнтів.

-

0K3K2K10

3K3K2K11

2K3K2K12

1K3K2K13

1K3K2K10

0K3K2K11

3K3K2K12

2K3K2K13

2K3K2K10

1K3K2K11

0K3K2K12

3K3K2K13

3K3K2K10

2K3K2K11

1K3K2K12

0K3K2K13