[irt.od.ua]КонспектАПСПК / КонспектАПСПК

.pdf

12.2.Структура современного процессора

На рис. 12.4. дана структура современного процессора.

|

|

|

|

|

|

5. MMX |

|

|

|

9. L1 Tag |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1. |

|

|

|

3. |

|

5. |

SSE |

|

8. |

|

|

|

12. |

|

De- |

|

|

|

Instr. |

|

|

|

|

Load |

|

10.L1 Data |

|

|

In- |

|

|

|

|

|

|

|

|

|||||||

coder |

|

|

|

Con- |

|

5. |

3Dnow |

|

/ |

|

|

|

ter- |

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

trol |

|

|

|

|

Store |

|

|

|

|

face |

|

|

|

|

|

6. |

SR |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

11. L2 |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

7. Integer |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

7. Integer |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

2.Table |

|

|

3. TLB |

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

7. Integer |

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 12.4. Структура современного процессора

Процессор содержит следующие блоки.

1.Декодер команд CISC – RISC - Instrution Decoder.

2.Блок предсказания переходов и таблица переходов - Prediction Table.

3.Блок распределения инструкций – Instrution Control (72–entry).

4.Регистры хранения декодированных команд TLB.

5.Конвейеры с плавающей точкой FPU (MMX, SSE, 3Dnow!)

6.Регистры и блок их быстрого переименования – Stack Rename.

7.Конвейер целочисленных вычислений – Integer.

8.Блок выгрузки-загрузки данных – Load/Store.

9.L1 Tag – кэш 1-го уровня для хранения инструкций.

10.L1 Data – кэш 1-го уровня для хранения данных

11.L2 – кэш 2-го уровня.

12.Интерфейс 64 бита - Interface.

В процессоре используются следующие технологии.

Risk-ядро. Для увеличения быстродействия в CPU CISC-команды декодируются в RISC-подобные команды.

Конвейер. Команда делится на стадии. Каждая стадия выполняется отдельным блоком.

Блоки соединены в цепочку - конвейер. Закономерность такова: чем больше стадий конвейера, тем проще блоки и выше тактовая частота. Однако большее число команд выполняется одновременно и возникает проблема правильных переходов. Проблема решается предсказанием переходов и решением параллельной задачи во время перезагрузки конвейера (Hyper Threading)

51

Суперскалярность – способность выполнять несколько команд одновременно.

Система предсказания переходов: статическое (предопределенное), динамическое (на основе полученной ранее статистики переходов) и по предположению – выполняются сразу несколько ветвлений.

Виртуальные регистры.

Вместо перемещения данных в регистрах, меняются их имена. Кэш-память. Хранит промежуточные вычисления и текущие команды. MMX (Multi Media Extention – мультимедийное расширение ).

Hyper Threading (многопоточность). Применяется в процессорах Pentium IV для лучшей загрузки ядра при перезагрузке конвейера после ошибке предсказания перехода.

SIMD – одна инструкция – много данных. Технология 3Dnow! используется в процессорах AMD K6 и позже. SSE (Streaming SIMD Extensions), SSE2, SSE3 – ускоренная обработка многомерных массивов – используется в процессорах Pentium и Athlon.

Процессор связан с внешним миром через шинный интерфейс с тактовой частотой FSB=100-800МГц и разрядностью 64 бит. Ядро работает на частоте K*FSB, где K – коэффициент умножения.

Существует оптимальное значение Kopt (Kopt=10…12 для процессоров Athlon XP) в зависимости от типа решаемой задачи (потоковые вычисления, научные расчеты), при котором система имеет максимальное быстродействие. Быстродействие также возрастает при увеличении объема кэш-памяти, и, очевидно, от возрастания FSB и разрядности.

Технологии энергосбережения.

DBS – технология в Pentium 4 отключения компонентов по требованию (Enhanced Intel SpeedStep - Demand-Based Switching)

Cool’n Quiet – в Athlon64 снижение тактовой частоты при снижении нагрузки на процессор.

C1E - улучшенный режим состояния простоя C1E (Enhanced Halt Mode) ODCM - модуляция тактовой частоты

TM – Thermal Monitor

TM1режим автоматической защиты от перегрева

TM2 - Thermal Monitor 2. Является заменой TM1 и в случае сильного перегрева процессора понижает напряжение на ядре и снижает множитель.

Технологии шифрования и защиты

Запрещают удаленным пользователям устанавливать программы без разрешения ОС или пользователя. Это так называемый N-бит или Execute Disable Bit (EDB) - аналог AMD Enhanced Virus Protection (EVP). Принцип работы технологий состоит в запрете выполнение кода из отдельных областей памяти.

Поддерживается ОС Vista и позволяет решить проблему вирусов и Троянов. Intel Trusted Execution Technology – технология обеспечения защиты виртуальных вычислительных сред.

52

VT – технология виртуализации. Позволяет запустить две ОС одновременно.

12.3. Режимы работы центрального процессора

Реальный режим (Real Mode) соответствует возможностям CPU 8086/8088, позволяя адресовать не более 1 Мбайт памяти. С появление процессора 80286 появился дополнительный сегмент 64 Кбайт верхней памяти. В этом режиме стартуют все процессоры стандарта Х86.

Виртуальный режим (Virtual 8086 Mode). Этот режим является особым состоянием задачи защищенного режима, в котором процессор функционирует как 256 независимых процессоров 8086. На одном процессоре в таком режиме могут одновременно исполняться до 256 задач с изолированными друг от друга ресурсами. В этом режиме работает эмулятор MS DOS из ОС Windows. Защищенный режим (Protected Mode) появился впервые в CPU 80286. В этом режиме современный CPU может адресовать до 4 Гбайт физической и до 16 терабайт виртуальной памяти. Если физическая память полностью загружена, то данные, не поместившиеся в память, располагаются на винчестере в виде файла подкачки. Таким образом, CPU работает не с реальными, а с виртуальными адресами, которые управляются с помощью специальных таблиц. Эту память называют еще виртуальной памятью потому, что фактически она не существует как единое целое.

Защищенный режим позволяет системе запустить несколько защищенных друг от друга процессов. Структура этого режима приведена на рис. 12.2.

Защита памяти с помощью сегментации запрещает:

•использовать сегменты не по назначению (например, пытаться трактовать область данных как коды инструкций);

•нарушать права доступа (пытаться модифицировать сегмент, предназначенный только для чтения, обращаться к сегменту, не имея достаточных привилегий, и т. п.);

•адресоваться к элементам, выходящим за лимит сегмента;

•изменять содержимое таблиц дескрипторов (то есть параметров сегментов), не имея достаточных привилегий.

Используется четырехуровневая иерархическая система привилегий,

представленная на рис.12.5.

Для попадания в более высокий приоритет необходимы соответствующие права (лицензия).

На рис. 12.6 представлены уровни привилегий ОС Windows.

В ОС Vista имеется только два уровня привилегий: ядро операционной системы и пользовательские приложения. Это обеспечивает надежность системы и не требует перезагрузки системы при установке программ.

53

Селектор (16 бит) |

|

(Номер задачи) |

Смещение (32 бит) |

|

|

|

|

|

|

Таблица дескрипторов |

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

+ |

|

||||||

|

|

|

|

|

Базовый адрес (32 бит) |

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Линейный адрес (32 бит) |

||||

|

Регистр CR3 (32 бит) |

|

|

|

|

|

|

|

(Виртуальный адрес) |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

Индекс таблицы (18 бит) |

|

Индекс страницы (18 бит) |

|

|

Смещение (12 бит) |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

+ |

|

Каталог таблиц |

|

+ |

|

Таблица страниц |

|

|

+ |

|

||||

|

|

|

Адрес таблицы |

|

|

|

Адрес страницы |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Физ. адрес (32 бит)

Рис. 12.5. Формирование линейного адреса в защищенном режиме

3 2

1 0

Рис. 12.6. Уровни привилегий

0 – Ядро операционной системы и драйвера (высшая степень защиты) 1 – Оболочка операционной системы 2 – Менее важные части операционной системы

3 – Пользовательское приложение (низший приоритет)

13.1.Кэширование инструкций и данных

Впереводе слово «кэш» (cache) означает склад. Он является дополнительным быстродействующим хранилищем копий блоков большей, но относительно медленной памяти, к которым, вероятно, в ближайшее время будет обращение.

Кэширование – эффективный способ повышение пиковой производительности системы за счет использования буферной памяти высокого быстродействия. Статическая память в ядре процессора кэширует ОЗУ компьютера. ОЗУ в свою очередь кэширует обращения к жесткому диску, а последний используется для кэширования записи на оптический диск.

Для сохранения приемлемой стоимости системы используется кэш-память относительно небольшого объема.

54

CPU |

|

Cache |

|

Mem |

|

HD |

|

CD |

32G/s |

|

32G/s |

|

3.2G/s |

|

100M/s |

|

10M/s |

|

|

|

|

|

|

|

|

|

Рис. 13.1. Последовательность кэширования данных

Архитектура кэш. Кэш CPU состоит из ячеек статической памяти для достижения максимального быстродействия, а также контроллера памяти, который решает задачи помещения или извлечения данных.

Cache=Tag+Data

Tag – характеристики данных: адрес + параметры (действительные или недействительные)

Существуют следующие архитектуры кэш.

•Принстонская, использующая общую память для команд и данных;

•Гарвардская с разделенной областью инструкций и данных;

•Супергарвардская, позволяющая обмениваться данными между областями кэш.

Для многоядерных процессоров вторая кэш L2 бывает

•раздельная для каждого ядра (Athlon X2)

•общая (неразделенная) для нескольких ядер (Conroe).

Последняя архитектура используется в Core 2 Duo позволяет более эффективно использовать объем памяти, однако более медленная.

В настоящее время кэш центрального процессора функционирует с частотой процессорного ядра. При этом встречаются два ее типа:

•Инклюзивная (поглощающая). L1 – 2 такта, L2 – также 2 такта (Pentium).

•Эксклюзивная (дополняющая) L1 – 2 такта, L2 – 4 такта (Athlon). Существуют также два основных алгоритма записи данных из кэша в основ-

ную память: сквозная запись WT (Write Through) и обратная запись WB (Write Back).

Алгоритм WT предусматривает выполнение каждой операции записи, попадающей в кэшированный блок, одновременно и в строку кэша, и в основную память. При этом процессору при каждой операции записи придется ожидать окончания относительно длительной записи в основную память. Алгоритм достаточно прост в реализации и легко обеспечивает целостность данных за счет постоянного совпадения копий данных в кэше и основной памяти. Для него нет необходимости хранения признаков — вполне достаточна только информация о тегах. Но эта простота оплачивается низкой эффективностью записи. Существуют варианты этого алгоритма с применением отложенной буферированной записи, при которой данные в основную память переписываются через FIFO-буфер во время свободных тактов шины.

Алгоритм WB позволяет уменьшить количество операций записи на шине основной памяти. Если блок памяти, в который должна производиться запись,

55

отображен и в кэше, то физическая запись сначала будет произведена в эту действительную строку кэша, и она будет отмечена как грязная (dirty), или модифицированная, то есть требующая выгрузки в основную память. Только после этой выгрузки (записи в основную память) строка станет чистой (clean), и ее можно будет использовать для кэширования других блоков без потери целостности данных. В основную память данные переписываются только целой строкой (после заполнения всех ее секторов в случае секторированного кэша) или непосредственно перед ее замещением в кэше новыми данными. Данный алгоритм сложнее в реализации, но существенно эффективнее, чем WT.

В зависимости от способа определения взаимного соответствия строки кэша и области основной памяти различают три способа построения кэш-памяти: кэш прямого отображения (direct-mapped cache), полностью ассоциативный кэш (fully associative cache) и их комбинация — частично или наборноассоциативный кэш (set-associative cache).

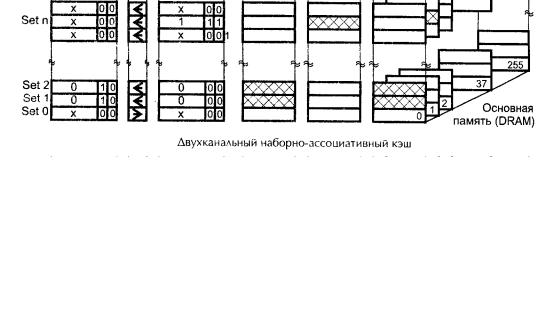

На рис. 13.2. приведена структура наборно-ассоциативной кэш.

Рис. 13.2. Наборно-ассоциативная кэш

13.2. Системные ресурсы и карта памяти в ОС Windows

Современный компьютер – это взаимодействие большого количества различных цифровых устройств. Для их взаимодействия необходимо рациональное распределение ресурсов, которыми располагает система PC. К системным ресурсам PC относятся:

•области системной памяти - для хранения данных устройств

•порты ввода-вывода (всего 64к) – в том числе для сетевых устройств (Интернет)

•прерывания (как номера, так и функции) – для обслуживания по запросу

•каналы ПДП (15 каналов + UDMA) – для работы с памятью

Память в Windows 95/98 распределяется на следующие области

56

1. Стандартная оперативная память (Conventional Memory) – первые 640

кБ

2.Аппаратная память (UMA – Upper Memory Area) – 384 кБ

3.Верхняя память (HMA – High Memory Area) – 64 кБ. Появилась вследствие ошибки в процессоре 286.

4.Расширенная память (XMS – Extended Memory Specification) - расположена выше HMA.

4.1.Растянутая память (EMS – Expanded Memory Specification) – первая часть XMS

5.Виртуальная память – файл подкачки на HD – продолжение памяти

XMS.

В ОС Windows NT/XP используется единое адресное пространство через защищенный режим. При этом в 32-разрядных ОС адреса внешних устройств (видеоадаптер, BIOS и др.) расположены в 4-м гигабайте общего адресного пространства. Поэтому максимальный объем ОЗУ составляет 3.25 ГБ. В 64разрядных системах объем ОЗУ практически неограничен.

13.3.Технология Plug & Play

Технология Plug & Play подразумевает автоматизацию подключения устройств в систему путем распределения между ними системных ресурсов.

В ПК действуют три группы базовых аппаратно-программных средств:

•Базовая система ввода/вывода

•Базовая аппаратная часть ПК – CPU + контроллеры на системной плате + слоты расширения PCI

•Операционная система + дополнительное программное обеспечение. Взаимодействие базовых средств позволяет автоматизировать процесс

подключение новых (дополнительных) устройств к ПК. Процесс установки осуществляется следующим образом.

•устанавливаются (либо уже имеются в ОС ПК) драйвера нового устройства.

•с помощью BIOS или ОС запрашивается тип устройства (шина PCI)

•новое устройство выдает ID код

•в соответствии с ID кодом выделяются и закрепляются необходимые системные ресурсы для нового устройства.

Контрольные вопросы

1.Из каких основных узлов состоит ядро современного процессора?

2.В чем реальность реального режима?

3.Почему виртуальный режим так называется? В чем его суть?

4.От чего защищает защищенный режим? Как он функционирует?

5.Что такое кэш и политика кэширования?

6.Приведите существующие типы архитектур кэш-памяти.

7.Как технология Plug & Play связана с системными ресурсами?

57

Лекция 14. Интерфейсы

14.1. Классификация интерфейсов

Интерфейсом называется способ соединения различных устройств системы. Наиболее часто используемыми интерфейсами являются:

ISA – архитектура индустриального стандарта – шина, разработанная для IBM/PC. В настоящее время не поддерживается в новых разработках.

PCI – Peripheral Component Interconnect – периферийное соединение компонентов. Универсальная шина для Pentium-систем.

PS/2 – порты для подключения мыши и клавиатуры. LAN – Local Area Network - сетевое соединение. USB – универсальная последовательная шина.

SCSI (скази) – Small Computer System Interface – высокоскоростной интерфейс для рабочих станций.

IrDA – InterFace Red Data Association

MIDI – Musical Instrumens Digital Interface – интерфейс для подключения музыкальных инструментов.

IDE – Integrated Drivers Electronics - интерфейс подключения жестких дисков. Часто используется эквивалент ATA – AT (улучшенный) attachment или SATA – последовательный ATA. eSATA – для внешних подключений.

В таблице 14.1. проведена классификация различных интерфейсов.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Таблица 14.1. |

||

|

|

|

|

|

|

|

|

|

Интерфейс |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Внешний |

|

|

|

|

|

|

|

|

|

|

Внутренний |

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

Проводной |

|

Беспроводной |

|

|

Универсальный |

|

|

Специализиров. |

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

Универ- |

Специали- |

|

|

ИК-лучи, |

|

|

|

ISA, PCI, |

|

AGP, IDE |

||||||||||||

сальный: |

зирован- |

|

|

BlueTooth, |

|

PCI- |

|

(ATA, |

||||||||||||||

COM, |

ный: |

802.11 |

|

|

|

|

exp1…4x, |

|

SATA), |

|||||||||||||

LPT, USB, |

PS/2 |

|

|

(WiFi) |

|

|

|

NCR, SCSI |

|

Floppy, |

||||||||||||

FireWire, |

DialUp, |

|

|

|

|

|

|

|

|

|

|

|

|

|

FCI- |

|||||||

PCMCA, |

LAN, |

|

|

|

|

|

|

|

|

|

|

|

|

|

exp16x |

|||||||

eSATA |

MIDI |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

Основные характеристики интерфейсов сведены в таблицу 14.2.

Таблица 14.2.

58

Интерфейс |

Пропускная спо- |

Кол- |

Горячая |

Расстояние |

Кол. кон- |

|

собность |

во у-в |

замена |

|

тактов |

Последовательн. порт COM |

11 кБ/с |

1 |

Нет |

10 м |

9(25) |

Параллельный порт LPT |

0.6-2 МБ/с |

64 |

Нет |

4 м |

25(36) |

USB 1.0/2.0(3.0 - 2008г.) |

0.5..60(600)МБ/с |

127 |

Да |

5 м |

4 |

FireWire (IEEE 1394a/b) |

50/100 МБ/с |

63 |

Да |

4.5 м |

6 |

DialUp 56к |

5.5кБ/с |

1 |

Нет |

>1км |

2 (RJ-11) |

LAN 10/100 |

1…10МБ/с |

1 (>1) |

Да |

100 м |

4 (RJ-45) |

IrDA |

10 кБ/с |

1 |

Да |

3 м |

- |

BlueTooth |

до 60кБ/с |

1 |

Да |

10…100 м |

- |

802.11 |

≥5МБ/с |

1 |

Да |

10…100 м |

- |

ISA |

1МБ/с |

8 |

Нет |

0 |

62 |

PCI /PCI-X |

0.1-0.5/2ГБ/с |

1 |

Нет |

0 |

94 |

PCI Express |

≥4ГБ/с |

1 |

? |

0 |

|

AGP 1x/2x/4x/8x |

0.26…2ГБ/с |

1 |

Нет |

0 |

|

Floppy |

35кБ/с |

2 |

Нет |

1 м |

34 |

IDE |

до 133МБ/с |

2 |

Нет |

0.5 м |

40/80 |

Serial ATA |

≥150MБ/с |

|

Да |

1 м |

|

SCSI |

≥300MБ/с |

|

Нет |

6 м |

50…80 |

На практике FireWire быстрее USB на 20%. Хотя теоретическая пропускная способность данной шины на 20% медленнее, чем у USB. Две витые пары FireWire против одной у USB, автономная (аппаратная) работа и наличие выделенной шины адреса на практике приводит к такой ситуации.

Wireless USB

802.15.4 (ZigBee). Разработка этого стандарта, в которой приняли участие Ember, Freescale, Honeywell, Invensys, Mitsubishi, Motorola, Philips и Samsung, велась прежде всего для обеспечения недорогой широкополосной беспроводной связи в сеть устройств промышленной автоматики, сенсоров и других автономных устройств, которым достаточно небольшой пропускной способности сети, но желательна работа от батарей в течение долгого времени. Также изначально в стандарт закладывается принцип построения mesh-сетей, распределённых сетей равноправных устройств без чётко прописанного маршрута следования сигнала.

Однако благодаря своей универсальности технология сейчас позиционируется в «цифровой дом» для подсоединения мышей, клавиатур и «мудрых кофеварок» к домашнему серверу, централизованного управления видео— и аудиоаппаратурой, кондиционерами, воротами и прочим. Технические характеристики:

•Частотные диапазоны: 16 каналов 2,4 ГГц для всего мира, где эти частоты свободны (250 Кбит/с), 1 канал 868 МГц для Европы (20 Кбит/с) и 10 каналов 915 МГц для Америки (40 Кбит/с). Дальность связи узлов в зависимости от частотного диапазона 70-300 метров. Это собственно спецификации 802.15.4.

•В ZigBee добавлены логический уровень, безопасность и программный интерфейс. В сеть может входить до 65 536 (!) клиентов, она может быть организована по топологии звезда, кластер (созвездие) или mesh, очень малое время реакции клиентов и изменения их состояния со спящего до активного (всё менее секунды). Она

59

может «самонастраиваться», — функции координаторов сети не закреплены жёстко за каким-либо узлом.

14.2. Параллельный интерфейс (LPT)

Назначение. Первоначально использовался стандарт от фирмы Centronics для связи принтера с ПК. Получил название SPP (стандартный параллельный порт). Широко применяется и для других устройств: сканеры, плоттеры, а также может использоваться для подключения адаптера внешнего цифрового устройства. В настоящее время вытесняется интерфейсом USB. Распределение сигналов. Разъем содержит 25 контактов согласно таблице 14.3.

|

|

|

Таблица 14.3. |

№конт. |

Обозначение сигнала |

Вход/выход |

Назначение |

|

|

от-но ПК |

|

1 |

-STROBE (-WRITE) |

Выход |

Готовность (запись) |

2-9 |

Data 0 – Data 7 |

Выход/вход |

Биты данных |

10 |

-ACK (- INTR) |

Вход |

Подтверждение (запрос на прерывание) |

11 |

BUSY (- WAIT) |

Вход |

Принтер занят (ожидание) |

12 |

PE (Paper end) |

Вход |

Конец бумаги |

13 |

SLCT (Select) |

Вход |

Контроль состояния принтера |

14 |

AF (-DATA STB) |

Выход |

Перевод строки (строб данных) |

15 |

ERROR |

Вход |

Ошибки |

16 |

-INIT (-RESET) |

Выход |

Инициализация (сброс) |

17 |

SLCT IN (-ADDRSTB) |

Выход |

Состоян. On-Line (строб адреса) |

18-25 |

GND |

|

Корпус |

В скобках указаны альтернативные сигналы в стандарте EPP.

Стандарты LPT

1) SPP – стандартный параллельный порт.

•Полубайтная передача данных: вначале младший полубайт, затем – старший.

2)EPP – улучшенный параллельный порт:

•Увеличена тактовая частота до 800 кБ/с.

•Двунаправленная побайтная передача.

•Поддержка до 64 устройств.

3)ECP – порт с расширенными возможностями:

•Дополнен режимом DMA.

•Поддерживает до 128 устройств.

•Аппаратное сжатие данных.

•Повышена скорость передачи до 2 МБ/с.

60