- •Министерство образования и науки

- •Лабораторная работа № 1.1

- •Интерфейс программного комплекса Electronics Workbench

- •Порядок работы с системой схемотехнического моделирования Electronics Workbench 5:

- •Пробное моделирование радиоэлектронных устройств при помощи программного комплекса Electronics Workbench

- •Моделирование интегрирующей rc – цепи

- •Моделирование дифференцирующей rc – цепи

- •Задание

- •Лабораторная работа № 1.2

- •Теоретические сведения:

- •Задание

- •Краткие выводы

- •Контрольные вопросы и задачи

- •Лабораторная работа № 1.3

- •Теоретические сведения

- •Задание

- •Лабораторная работа № 2

- •Теоретические сведения

- •Задание

- •Теоретические сведения

- •Задание

- •Лабораторная работа №4

- •Теоретические сведения Операционный усилитель

- •Инвертирующий усилитель

- •Неинвертирующий усилитель

- •Инвертирующий сумматор

- •Дифференциальный усилитель

- •Интегратор

- •Задание

- •Лабораторная работа №5

- •Основные теоретические положения

- •Задание

- •Лабораторная работа № 6.1

- •Теоретические сведения

- •Rs-триггеры

- •Двухступенчатый синхронный rs-триггер

- •D-триггер(триггер задержки)

- •Т-триггер

- •Jk-триггер

- •Задание

- •Лабораторная работа № 6.2

- •Теоретические сведения

- •Задание

- •Литература

Задание

Используя компоненты Electronics WorkBench соберите поочередно схемы для исследования логических элементов И, ИЛИ, НЕ, И-НЕ, ИЛИ-НЕ.

Пример схемы для исследования элемента И приведен на рис. 14.

Рис. 14

В этой схеме переключателями X1 и X2 задаются значения двух входных сигналов логического элемента И, которые контролируются вольтметрами V1, V2. Верхнее положение переключателя соответствует логической 1 (высокий уровень напряжения: +5 В), а нижнее – логическому 0 (низкий уровень напряжения: 0 В). Выходной сигнал анализируется по показанию вольтметра V3 или состоянию светодиода. При логической 1 на выходе элемента И светодиод светится (включен), а при логической 0 – не светится (выключен). Резистор 330 Ом ограничивает ток светодиода в пределах допустимого.

Задавая с помощью переключателей X1 и X2 все возможные комбинации входных сигналов, составьте таблицу истинности для каждого логического элемента.

Для того, чтобы попрактиковаться в применении конкретных интегральных микросхем, при исследовании элемента И-НЕ используйте один из четырех элементов микросхемы К155ЛА3 (зарубежный аналог SN 7400). При этом необходимо подключить положительный полюс источника питания 5 В к выводу 14, а отрицательный («земля») – к выводу 7.

Проведите полную минимизацию функции, представленной в п.2.7. Для минимальной формы функции составьте схему реализующего её устройства с использованием заданных преподавателем логических элементов или микросхем. Если микросхемы не заданы, используйте К155ЛА3, К155ЛА4 (SN 7410). Составьте таблицу истинности для построенной схемы.

Лабораторная работа № 6.1

Тема: Исследование триггеров

Цель работы: Изучить схемы и работу различных триггеров, научиться составлять таблицы переходов и строить временные диаграммы

Теоретические сведения

Триггеры - это устройства, предназначенные для хранения одного разряда двоичной информации. Триггеры имеют два устойчивых состояния: состояние "0" и состояние "1".

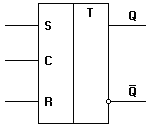

Триггер имеет два выхода: прямой и инверсный. Состояние триггера определяется по прямому выходу. Состояние триггера можно изменять входными сигналами.

Rs-триггеры

Асинхронный RS-триггер с прямыми входами. Вход R - это вход установки триггера в состояние логического 0, вход S - это вход установки триггера в состояние логической 1.

Асинхронным называется такой триггер, который меняет свое состояние в момент подачи входного сигнала на входы S и R. Активным сигналом для этой схемы является логическая 1. Работа триггера определяется таблицей переходов:

|

S |

R |

Q |

Примеч. |

|

0 |

0 |

Q |

Хранен. |

|

0 |

1 |

0 |

Устан. 0 |

|

1 |

0 |

1 |

Устан. 1 |

|

1 |

1 |

Не определено |

Запрет |

Схема, условное обозначение и временные диаграммы триггера:

Асинхронный RS-триггер с инверсными входами. Активным сигналом для этой схемы является логический 0.

Работа триггера определяется таблицей переходов:

|

|

|

Q |

Примеч. |

|

0 |

0 |

Не определено |

Запрет |

|

0 |

1 |

1 |

Устан. 1 |

|

1 |

0 |

0 |

Устан. 0 |

|

1 |

1 |

Q |

Хранен. |

Схема, условное обозначение и временные диаграммы триггера:

Синхронный RS-триггер

Триггер называется синхронным, если у него помимо информационных входов S и R, существует синхронизирующий вход С. Триггер будет менять свое состояние только при логической 1 на входе С.

Активным сигналом для этой схемы является логическая 1.

Таблица переходов триггера

|

С |

S |

R |

Q |

Примеч. |

|

0 |

0 или 1 |

0 или 1 |

Q |

Хранен. |

|

1 |

0 |

0 |

Q |

Хранен. |

|

1 |

0 |

1 |

0 |

Устан. 0 |

|

1 |

1 |

0 |

1 |

Устан. 1 |

|

1 |

1 |

1 |

Не определено |

Запрет |

Схема,

условное обозначение, временные

диаграммы:

В рассмотренном триггере информационные входы воспринимаются все время пока на входе С логическая 1. Такая синхронизация называется статической, в отличае от рассматриваемой ниже динамической, когда триггер переключается только по переднему или заднему фронту синхроимпульса (прямой или импульсный синхровход).