- •5. Лабораторная работа № 4 «Синтез триггеров на логических элементах»

- •1. Исследование асинхронного rs-триггера

- •2. Исследование rs-триггера, синхронизируемого по уровню

- •3. Исследование rs-триггера, синхронизируемого фронтом

- •4. Исследование d-триггера, синхронизируемого по уровню

- •5. Исследование d-триггера, синхронизируемого фронтом

- •6. Исследование т-триггера

- •7. Исследование jk-триггера

- •Синтез триггеров на лэ с коммутирующими бистабильными ячейками (бя)

- •Готовых триггеров на примере srff

- •Порядок выполнения работы

- •Задание для самостоятельной работы

- •Контрольные вопросы

- •Содержание отчета

- •Литература

5. Лабораторная работа № 4 «Синтез триггеров на логических элементах»

Цель работы: создание и исследование работы триггеров на логических элементах, создание триггеров на базе готовых триггеров другого типа.

1. Исследование асинхронного rs-триггера

1.1. Открыть приложение MAX+plusII.

1.2. Создать новый графический файл (см. раздел 1 лабораторной работы № 1), сохранить его как c:\Student\AT\RSasync.gdf и сделать данный проект текущим Ctrl+Shift+J.

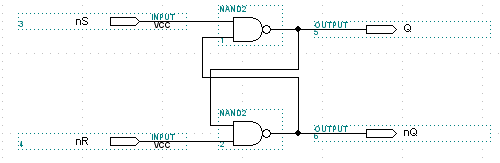

1.3. Собрать в рабочем поле схему асинхронного RS-триггера на ЛЭ «И-НЕ» (nand):

Здесь

и далее названия инверсных входов и

выходов будем предварять буквой n,

например,

![]() ,

и т.д.

,

и т.д.

1.4. Указать тип ПЛИС FLEX 8000 EPF8282ALC84-4 в меню Assign\Device.

1.5. Сохранить и откомпилировать проект Save & Compile (Ctrl+L). Перекомпиляцию данного проекта с опцией Processing\ Functional SNF Extractor делать не следует, т.к. в этом случае САПР не может корректно провести симуляцию схемы и выдает сообщение об ошибке. Это касается и других проектов, содержащих схемы, в которых возможно неопределенное состояние выходов при запрещенных комбинациях на входе.

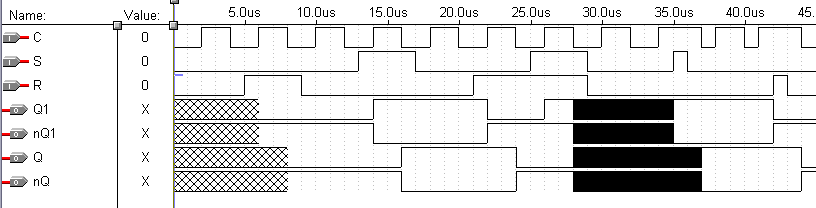

1.6. Создать файл входных данных RSasync.scf в редакторе временных диаграмм и провести симуляцию (см. раздел 2 лабораторной работы № 1). Сравнить результаты с исходной таблицей работы триггера:

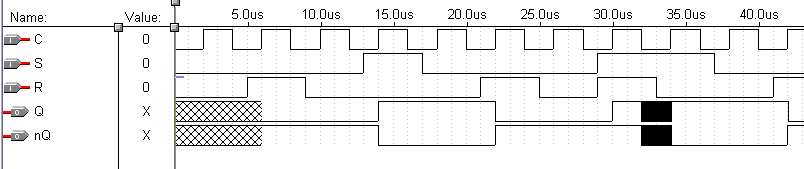

Заштрихованная область соответствует безразличному состоянию (Х), а в неопределенном состоянии уровень постоянно меняется (в зависимости от этапа расчетов САПР), в результате чего получается зачерненная область.

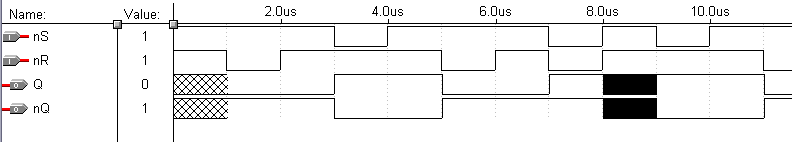

2. Исследование rs-триггера, синхронизируемого по уровню

2.1. Открыть файл RSasync.gdf и сохранить его как c:\Student\AT\ RSlevel.gdf, сделать данный проект текущим Ctrl+Shift+J (см. раздел 2 лабораторной работы № 1).

2.2. Вставить из библиотеки примитивов дополнительные элементы и изменить схему таким образом, чтобы получился RS-триггер, синхронизируемый по уровню.

2.3. Указать тип ПЛИС FLEX 8000 EPF8282ALC84-4 в меню Assign\Device.

2.4. Сохранить и откомпилировать проект Save & Compile (Ctrl+L). Перекомпиляцию данного проекта с опцией Processing\ Functional SNF Extractor делать не следует.

2.5. Создать файл входных данных RSlevel.scf в редакторе временных диаграмм и провести симуляцию (см. раздел 2 лабораторной работы № 1). Сравнить результаты с исходной таблицей работы триггера.

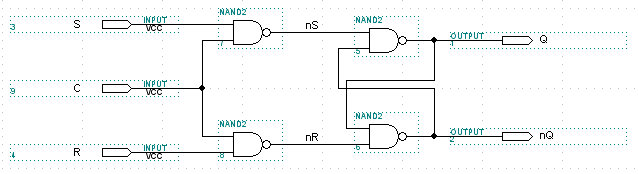

3. Исследование rs-триггера, синхронизируемого фронтом

3.1. Открыть файл RSlevel.gdf и сохранить его как c:\Student\AT\RSfront.gdf, сделать данный проект текущим Ctrl+Shift+J (см. раздел 2 лабораторной работы № 1).

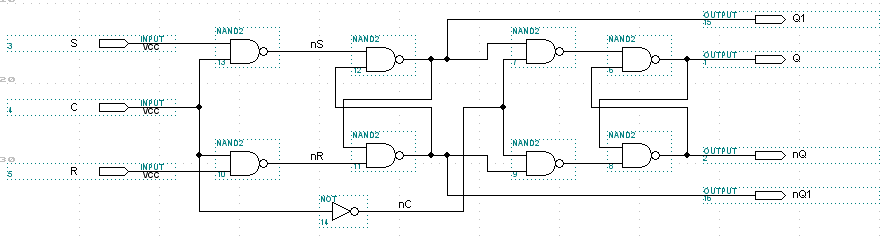

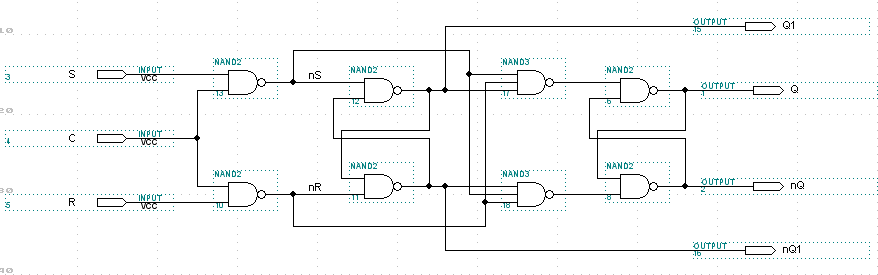

3.2. Вставить из библиотеки примитивов дополнительные элементы и собрать RS-триггер, синхронизируемый фронтом, по MS-схеме либо с инвертором (рис. 1), либо с запрещающими связями (рис. 2) (выбрать по указанию преподавателя).

Рис. 1

Рис. 2

3.3. Указать тип ПЛИС FLEX 8000 EPF8282ALC84-4 в меню Assign\Device.

3.4. Сохранить и откомпилировать проект Save & Compile (Ctrl+L). Перекомпиляцию данного проекта с опцией Processing\ Functional SNF Extractor делать не следует.

3.5. Создать файл входных данных RSfront.scf в редакторе временных диаграмм и провести симуляцию (см. раздел 2 лабораторной работы № 1). Сравнить результаты с исходной таблицей работы триггера.