Оборудование

На кафедре АТ имеются :

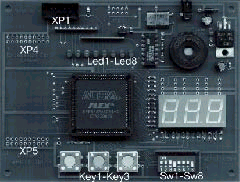

Лабораторный макет LabKit 8000;

Лабораторный макет Stend 001;

САПР фирмы Altera MAX+plusII;

Кабель типа ByteBlaster.

Лабораторные макеты LabKit 8000 и Stend 001 предназначена для практических работ по созданию цифровых устройств на ПЛИС фирмы Altera. На плате установлена микросхема ПЛИС FPGA типа EPF8282ALC84. Загрузка конфигурации FPGA осуществляется через кабель типа ByteBlaster.

САПР MAX+plusII специально разработан фирмой Altera для проектирования устройств на ПЛИС этой фирмы.

Кабель типа ByteBlaster стандартный кабель для прошивки микропроцессорных устройств с помощью PC.

Внешний

вид макета

LabKit

8000

Внешний

вид макета

LabKit

8000

Описание плис epf8282alc84

Компания Altera выпускает широкую номенклатуру ПЛИС, отличающихся структурой и степенью интеграции, которые обеспечивают возможности эффективной реализации комбинационных и последовательностных устройств различного назначения. В настоящем лабораторном практикуме используются ПЛИС типа EPF8282A семейства Flex8000. В состав этого семейства входят 13 типов ПЛИС, имеющих степень интеграции от 5000 до 32000 эквивалентных вентилей.

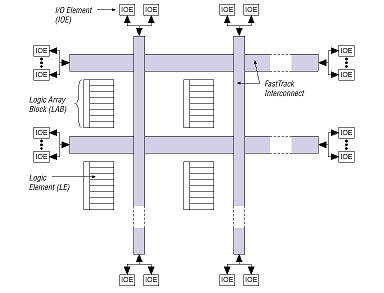

ПЛИС типа EPF8282A содержит 5000 эквивалентных логических вентилей. Структура этой ПЛИС приведена на рис. П1.1.

Структкра ПЛИС рис. П1.1.

В состав ПЛИС входят 26 логических блоков LAB (Logic Array Block) рис.П1.3, которые размещены на кристалле в виде матрицы, содержащей 2 строки (А и В) и 13 столбцов. Каждый блок LAB содержит 8 логических элементов LE (Logic Element), соединяемых между собой программируемой локальной матрицей соединений (ЛМС). Таким образом данная ПЛИС содержит 208 элементов LE. Соединения между блоками LAB и подключение буферных элементов ввода-вывода IOE (Input-Output Element) выполняется с помощью программируемой глобальной матрицы соединений (ГМС). В состав элементов LE и IOЕ входят синхронизируемые фронтом D-триггеры, общее число которых составляет 282.

При проектировании реальных цифровых устройств коэффициент использования элементов составляет около 50%, поэтому на базе этой ПЛИС можно реализовать устройства, сложность которых эквивалентна 2500 логических вентилей.

Базовые логические элементы

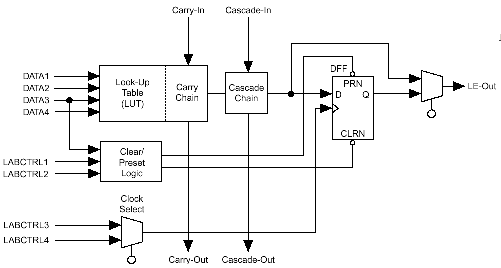

Схема базового элемента LE показана на рис. П1.2.

Базовый

ЛЕ рис.

П1.2.

Базовый

ЛЕ рис.

П1.2.

Основные логические функции выполняются программируемым логическим модулем (ПЛМ), который реализован на базе мультиплексера. В зависимости от типа проектируемого устройства ПЛМ программируется на выполнение любой заданной логической функции четырех переменных DАТА1-DАТА4 или используется для выполнения двух логических функций трех переменных. Выбор выполняемых ПЛМ функций осуществляется подачей определенной комбинации электрических сигналов, поступающих от внутреннего ОЗУ, содержимое которого определяет конфигурацию и функции, реализуемые ПЛИС. Соответствующее содержимое заносится в это ОЗУ в процессе предварительного программирования ПЛИС.

В состав элемента LE входит также синхронизируемый фронтом D-триггер со схемами синхронизации и предварительного (асинхронного) сброса-установки. Ко всем 8 элементам LE, входящим в состав одного логического блока LAB, подведены четыре общих локальных управляющих сигнала LABCTRL1-LABCTRL4 (рис. П1.2). В качестве синхросигнала может быть использован один из сигналов LABCTRL1,LABCTRL4. Сигналы LABCTRL1, LABCTRL2 совместно с одной из логических переменных DATA3 служит для формирования сигналов асинхронного сброса DFF и установки CLRN для D-триггера (рис. П1.2). Различные варианты выбора синхросигнала и формирования сигналов DFF, CLRN реализуются с помощью программируемых мультиплексеров (ПМ), которые выбирают тот или иной вариант выходного сигнала в зависимости от управляющего (программмирующего) сигнала, поступающего от внутреннего ОЗУ, содержимое которого задает требуемую конфигурацию ПЛИС.

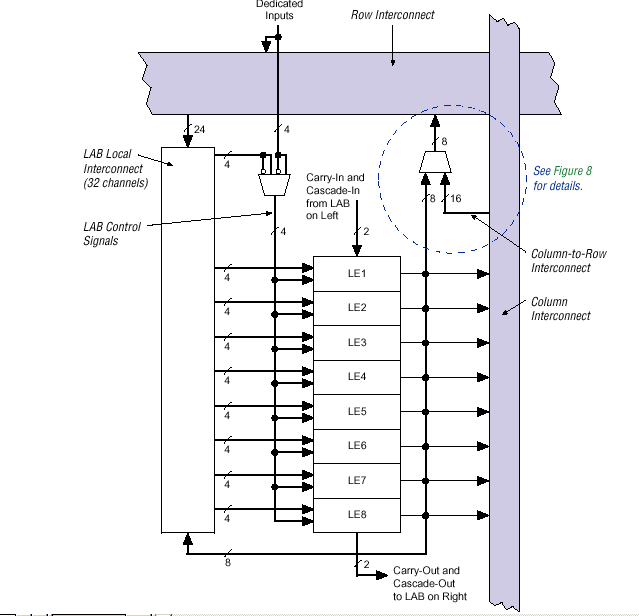

Л огический

блок рис.П1.3

огический

блок рис.П1.3

Особенностью элементов LE и логических блоков LAB является наличие специальных цепей для формирования и передачи сигналов переноса и каскадирования. Эти сигналы передаются по специальным линиям, которые последовательно соединяют все элементы, входящие в состав LAB, от LE1 до LE8. На входы первого элемента LE1 сигналы переноса и каскадирования поступают с выходов последнего элемента LE8 в логическом блоке, расположенном в этом ряду слева. С выхода последнего элемента LE8 в данном блоке эти сигналы поступают на входы элемента LE1 в соседнем блоке, расположенном в этом ряду справа. Таким образом с помощью цепей переноса и каскадирования можно последовательно соединить все блоки в одном ряду.

Выходной сигнал каскадирования SO = SI*F образуется путем конъюнкции входного сигнала каскадирования SI и функции F, реализуемой ПЛМ данного элемента LE. Таким образом путем каскадирования нескольких LE можно реализовать логические функции многих переменных, поступающих на их входы (до 4x8=32 переменных для элементов одного блока LAB). Если формировать инверсные значения сигналов SI и F, то в цепи каскадирования будет реализована дизъюнкция этих переменных (в соответствии с теоремой Де-Моргана).

Система проектирования MAX+Plus II автоматически выбирает режим ПЛМ для используемых LE в зависимости от заданного закона функционирования разрабатываемого устройства.