- •3. Создание принципиальной схемы

- •3.1. Выбор цифрового интерфейса

- •3.2 Микроконтроллер amd186 cc

- •3.2.1 Характеристики

- •3.2.2 Общее архитектурное представление.

- •3. Universal Serial Bus

- •3.2.3 Работа с hdlc.

- •3.2.4 Системные периферийные устройства.

- •1. Контроллер прерываний.

- •2. Универсальные каналы dma.

- •3. Программируемые I/o сигналы.

- •4. Программируемые таймеры.

- •5. Аппаратный Watchdog Timer.

- •3.2.5. Памятно-периферийные интерфейсы (Memory and Peripheral Interface).

- •1. Шинный интерфейс.

- •2. Dynamic Random Access Memory.

- •3. Chip Selects.

- •3.2.6. Применение Am186cc.

- •3.3 Документация для программиста контроллера

- •3.3.1. Введение в hdlc.

- •3.3.2 Этапы конфигурирования hdlc-каналов

- •3.3.3. Коммуникационные интерфейсы

- •1. SmartDma Interface

- •2. Programmed I/o Interface

- •3.3.4. Обеспечение основных функций hdlc.

- •3.3.5 Передатчик hdlc

- •3.3.6 Приемник hdlc.

- •3.3.7 Hdlc и SmartDma.

- •3.3.8 Прерывания.

- •3.3.9 Информация для сравнения с другими устройствами

- •3.3.10 Инициализация

- •3.4. Плис

- •3.4.1. Выбор элементной базы

- •3.4.2. Микросхемы плис 10к30.

- •3.4.3. Конфигурация и функционирование плис

- •Задание режима конфигурирования

- •3.5. Выбор микросхем flash.

- •Чтение.

- •3.6 Выбор микросхем озу

- •3.7 Описание интерфейса q2.

- •Требования к q-стыку

- •Типы кадров

- •Взаимодействие

- •Режим нормального ответа

- •Установление звена данных

- •Разъединение звена данных

- •Процедура в режиме разъединения

- •Обмен кадрами I

- •Подтверждения

- •Тестирование

- •3.7.5 Информирование об особых условиях и восстановление Действия при занятости станции

- •Ошибка в последовательности Ns

- •Восстановление по тайм-ауту

- •Неприем кадра

- •3.7.6 Другие параметры уровня звена передачи данных.

3.5. Выбор микросхем flash.

Из всего разнообразия микросхем флэш-памяти наиболее подходящей по таким показателям как емкость, быстродействие, потребляемая мощность и стоимость, наиболее подходящей является микросхема фирмы Atmelмодели AT45DB321. Технические характеристики ее таковы:

Напряжение питания – 2,7…3,6 В

Интерфейс – последовательный

Страничная организация памяти, т.е.

возможность перезаписи отдельной страницы

всего 8192 страницы по 528 байт

работа с группами страниц

Два 528-байтных буфера данных типа SRAM

Максимальная частота работы устройства – 13 МГц

Логические уровни входов и выходов: КМОП- и ТТЛ- совместимые

Исполнение: коммерческое и индустриальное

Рис. 3.3 Внешний вид микросхемы.

AT45DB321 содержит 34,603,008 бит памяти, организованной в 8192 страницы по 528 байт каждая. В дополнение к основной памяти AT45DB321 также содержит два SRAM буфера данных по 528 байт каждый. Буферы позволяют получать данные в то время как репрограммируется страница в главной памяти. Последовательный интерфейс легче стыкуется с устройствами, повышает надежность системы, минимизирует помехи переключения и требует меньше выводов.

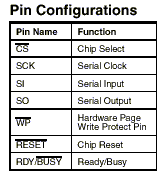

Устройство работает на частоте до 13 МГц, потребляя ток до 4 мА. Активизация AT45DB321 осуществляется через вывод chip select (CS) и обмен данными производится по трехпроводному интерфейсу, в который входят:

Serial Input (SI)

Serial Output (SO)

Serial Clock (SCK).

Для обеспечения гибкости работы с массивом памяти, в AT45DB321 существует трехуровневое иерархическое подразделение участков памяти на сектора, блоки и страницы. Программирование осуществляется на уровне страниц, стирание может производиться и на уровне страниц и на уровне блоков.

Рис. 3.4 Внутренняя организация

Действия устройства производятся в соответствии с инструкциями хост-процессора. Прием инструкции начинается по заднему фронту на CS. После этого принимается 8-битное слово, представляющее из себя код операции, а затем идет адрес буфера или участка памяти, над которым будут производиться какие-либо действия. Пока на CSнизкий уровень, синхронизирующая частота подается на входSCK.

Чтение.

В зависимости от кода операции, данные могут быть считаны как из памяти, так и из одного из буферов.

Ч тение

страниц из памяти:можно произвести

чтение любой из 8192 страниц памяти, минуя

буфера и не влияя на их содержимое. Для

начала чтения устройству посылается

8-битный код 52H, сопровождается 24 битами

адреса и 32 не значащими битами. Следующие

13 адресных бит (PA12-PA0) определяют адрес

страницы, а последующие 10 (BA9-BA0) адресуют

стартовый байт в странице. 32 не значащих

бита, которые следуют за 24 адресными

битами посылаются для инициализации

операции чтения. После их приема в

соответствии с синхроимпульсами на

выходеSO(serial

output) появляется считываемая

информация. После того, как выдана вся

информация, устройство будет продолжать

выдачу ее начиная с начала адресованной

страницы. По переднему фронту наCSпроисходит завершение операции чтения

и шинаSO переводится в

высокоимпендансное состояние.

тение

страниц из памяти:можно произвести

чтение любой из 8192 страниц памяти, минуя

буфера и не влияя на их содержимое. Для

начала чтения устройству посылается

8-битный код 52H, сопровождается 24 битами

адреса и 32 не значащими битами. Следующие

13 адресных бит (PA12-PA0) определяют адрес

страницы, а последующие 10 (BA9-BA0) адресуют

стартовый байт в странице. 32 не значащих

бита, которые следуют за 24 адресными

битами посылаются для инициализации

операции чтения. После их приема в

соответствии с синхроимпульсами на

выходеSO(serial

output) появляется считываемая

информация. После того, как выдана вся

информация, устройство будет продолжать

выдачу ее начиная с начала адресованной

страницы. По переднему фронту наCSпроисходит завершение операции чтения

и шинаSO переводится в

высокоимпендансное состояние.

Рис. 3.5 Блок-схема микросхемы.

Чтение из буфера: данные могут быть считаны с одного из двух буферов, используя различные кодовые комбинации для инициализации определенного буфера. Код 54Н используется для считывания данных из первого буфера, 56Н – для второго. Чтобы произвести чтение буфера, 8 бит кода операции должны следовать за 14 незначащими битами, 10 адресными битами и 8 опять незначащими.

Копирование страницы памяти в буфер. Содержимое страницы памяти может быть переписано в один из буферов. Код операции 53Н – для трансфера данных в буфер 1, код 55Н – для буфера 2. Код следует за одним зарезервированным битом, 13 адресными битами (PA12-PA0), которые определяют трансферную страницу в главной памяти и 10 незначащими битами. Во время трансфера страницы в регистре статуса находится информация о том, завершен трансфер или нет.

Сравнение содержимого буфера и страницы памяти: код операции 60Н для данных буфера 1 и 61Н для второго буфера. Код следует за 24 адресными битами, состоящими из одного зарезервированного бита, 13 адресных бит страницы в памяти (PA12-PA0) и 10 не значащих бит. По переднему фронту сигнала на CSпроисходит сравнение. По завершению операции сравнения в бит 6 статусного регистра заносится результат сравнения.

Программирование.

Запись в буфер: для занесения данных в буфер код команды 84H для первого буфера и 87H для второго. После кода следуют 14 незначащих бит и 10 адресных (BFA9-BFA0), которые определяют первый байт для чтения в буфере. Записываемые данные следуют за адресными битами. По окончанию занесения информации на CS выставляется высокий уровень.

Занесение данных из буфера в память с предварительным стиранием: кодовое слово 83H для первого буфера и 86H для буфера 2.Код следует за 24 адресными битами, состоящими из одного зарезервированного бита, 13 адресных бит записываемой страницы в памяти (PA12-PA0) и 10 не значащих бит.По выставлению высокого уровня наCSпроисходит перезапись, причем данные в странице предварительно стираются. Регистр статуса указывает в это время на то, что устройство занято во время всей процедуры.

Занесение данных из буфера в память без предварительного стирания: в предварительно стертую страницу может быть записана информация из буфера. Кодовое слово 88H для первого буфера и 89H для буфера 2.Код следует за 24 адресными битами, состоящими из одного зарезервированного бита, 13 адресных бит записываемой страницы в памяти (PA12-PA0) и 10 незначащих бит.По выставлению высокого уровня наCSпроисходит перезапись. Регистр статуса указывает в это время на то, что устройство занято во время всей процедуры. Необходимо предварительное очищение перезаписываемой страницы.

Стирание страницы: Сигналом для выполнения стирания служит код 81H , сопровождаемыйодним зарезервированным битом, 13 адресными битами записываемой страницы в памяти (PA12-PA0) и 10 незначащими битами.По выставлению высокого уровня наCSпроисходит стирание. Регистр статуса указывает в это время на то, что устройство занято во время всей процедуры.

Стирание блока: блок из восьми страниц может быть очищен одной командой для экономии времени при занесении больших объемов данных в устройство. Сигналом для выполнения стирания служит код 50H , сопровождаемыйодним зарезервированным битом, 13 адресными битами начальной записываемой страницы блока памяти (PA12-PA0) и 10 незначащими битами.По выставлению высокого уровня наCSпроисходит стирание. Регистр статуса указывает в это время на то, что устройство занято во время всей процедуры.

Запись содержимого страницы непосредственно в памяти: это комбинация процедур записи в буфер и перезаписи содержимого буфера в память с сопутствующим стиранием. Кодовое слово 82H для первого буфера и 85H для буфера 2 сопровождаетсяодним зарезервированным битом и 23 адресными битами. Первые13 бит адреса (PA12-PA0) определяют перезаписываемую страницу памяти, следующие 10 бит (BFA9-BFA0) определяют первый записываемый байт буфера. После считывания адресной информации, данные с входа SI поступают в буфер. По выставлению высокого уровня наCSпроисходит стирание страницы и перезапись в нее данных. Регистр статуса указывает в это время на то, что устройство занято во время всей процедуры.

Перезапись содержимого страницы: содержимое страницы сперва заносится в буфер а после этого те же данные заносятся обратно. Представляет собой комбинацию процедур записи в буфер из памяти и записи содержимого буфера в память с сопутствующим стиранием. Кодовое слово 58H для первого буфера и 59H для буфера 2 сопровождаетсяодним зарезервированным битом и 13 адресными битами(PA12-PA0), которые определяют перезаписываемую страницу памяти, следующие 10 бит незначащие. Выполнение процедуры происходит при выставлении высокого уровня наCS.Регистр статуса указывает в это время на то, что устройство занято во время всей процедуры.

Р егистр

статуса:этот регистр используется

для индикации занятости или готовности

устройства, результатов процедуры

сравнения содержимого буфера и страницы

памяти и для системной инициализации

устройства. Для чтения регистра

используется код 57H. После получения

последнего бита кода на выходSOподаются 8 бит статусного регистра,

начиная со старшего бита (бит 7). Первые

пять бит регистра статуса содержат

служебную информацию, остальные три

зарезервированы. После выдачи всех

восьми бит регистра цикл выдачи

повторяется. Это продолжается до тех

пор, пока на вход CS не будет подан высокий

уровень. Данные в регистре статуса

непрерывно обновляются и на выход будут

подаваться каждый раз обновленные

данные. Статус Ready/Busy устройства

индицируется битом 7 (1/0

соответственно). Результат последней

процедуры сравнения заносится в бит 6

регистра. Нулевое значение этого бита

означает совпадение данных в странице

памяти и буфере. Для системной инициализации

устройства служат биты 5, 4 и 3 статусного

регистра. Для

AT45DB321выставляемая комбинация трех бит

1, 1, 0.

егистр

статуса:этот регистр используется

для индикации занятости или готовности

устройства, результатов процедуры

сравнения содержимого буфера и страницы

памяти и для системной инициализации

устройства. Для чтения регистра

используется код 57H. После получения

последнего бита кода на выходSOподаются 8 бит статусного регистра,

начиная со старшего бита (бит 7). Первые

пять бит регистра статуса содержат

служебную информацию, остальные три

зарезервированы. После выдачи всех

восьми бит регистра цикл выдачи

повторяется. Это продолжается до тех

пор, пока на вход CS не будет подан высокий

уровень. Данные в регистре статуса

непрерывно обновляются и на выход будут

подаваться каждый раз обновленные

данные. Статус Ready/Busy устройства

индицируется битом 7 (1/0

соответственно). Результат последней

процедуры сравнения заносится в бит 6

регистра. Нулевое значение этого бита

означает совпадение данных в странице

памяти и буфере. Для системной инициализации

устройства служат биты 5, 4 и 3 статусного

регистра. Для

AT45DB321выставляемая комбинация трех бит

1, 1, 0.

Рис. 3.6 Формат регистра.

Аппаратная защита перезаписи страниц памяти: при низком уровне на входе WP первые 256 страниц памяти не могут быть перезаписаны.

Сброс (RESET): подача низкого уровня на вход RESET прерывает выполнение текущей процедуры и переводит устройство в режим ожидания до тех пор, пока на входе не появится высокий уровень. Вход RESET, будучи неподключенным, расценивается устройством, как если бы на него был подан высокий уровень, так что если данная функция не затребована, вывод RESET не нуждается в подключении.

READY/BUSY: на этом выводе низкий уровень, когда устройство занято.

Состояние Power-on/Reset: при первом включении устройства или после подачи сигнала reset, устройство переводится в т.н. SPI Mode 3. Вывод SO переводится в высокоимпендансное состояние, и только задний фронт сигнала на входе CS позволяет начать прием инструкции.