- •Лекция 4.Структурная организация и режимы работы процессора ibm pc.

- •4.1. Структурная организация процессора.

- •4.2..Стадии (этапы) выполнения команды

- •4.3. Режимы работы процессоров Intelи сегментная организация памяти

- •4.4. Особенности реального режима

- •4.5. Особенности защищенного режима

- •4.6.Регистровая структура процессора реального режима

- •4.7. Формирование физического адреса в реальном режиме

4.7. Формирование физического адреса в реальном режиме

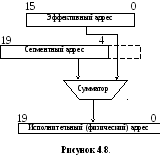

Напомним, что физическая память, к которой МП имеет доступ по ША, организована как последовательность ячеек. В IBM PC адресуется каждый байт информации, хотя передаваться по ШД может и не один байт, например, для МП Pentium – 8 байт. Диапазон значений физических адресов зависит от разрядности ША МП. Для i80486 и Pentium ША 32-х разрядная и позволяет адресовать до 4 Гб. Для обращения к конкретному физическому адресу в ОЗУ (ячейке с одним байтом) необходимо определить, как известно, адрес начала сегмента и адрес смещения внутри сегмента. Адрес сегмента представляет собой 16-ти битовое значение и является содержимым одного из сегментных регистров CS, DS, SS или ES. Исполнительный адрес (эффективный) может быть константой или чаще содержимым регистра РОН или указательных, или индексных, но тоже 16-разрядным. Таким образом, физический адрес операнда или команды формируется суммированием начального адреса соответствующего сегмента (содержимого сегментного регистра, сдвинутого на четыре разряда влево, т.е. дополненного нулями в четырех младших разрядах) и адреса смещения, так же называемого эффективным адресом. Адрес смещения вычисляется в МП на основе содержащейся в команде информации о способе формирования адреса операнда. Формирования физического адреса показано на рисунке 4.8.

Контрольные вопросы и задания:

Назовите структурные элементы ЭВМ, изображенные на рис. 1.

Чем отличаются команды и данные

Какими двумя параметрами можно охарактеризовать ячейку памяти

Чем отличаются ячейки, хранящие данные и команды

Что такое «линия», «шина» и «магистраль» Изобразите их.

Какое устройство ЭВМ является источником информации для ША.

Если ША имеет ширину 4 двоичных разряда, каков размер адресного пространства ЭВМ.

Если размер адресного пространства ЭВМ равен 4, какова разрядность ША.

Перечислите стадии выполнения команды, этапы выполнения программы

Какие шины участвуют при выполнении любого обращения процессора к памяти

Назовите управляющие регистры МП и их назначение

Что такое «флаг»

В чем отличия в назначении между Счетчиком команд и Регистром команд.

Какими параметрами характеризуется сегмент в реальном режиме и какими – в защищенном.

В каком режиме МП исполняемая программа может иметь размер значительно больший, чем ОЗУ ЭВМ.

Какие из регистров указывают на сегмент: 1)CS 2)ES 3)IP 4)BP 5)SS 6)F 7)ES 8)BH 9)ES.

Какой из регистров указывает на сегмент, содержащий данные для текущей (исполняемой) программы: 1)CS 2)ES 3)IP 6)F 7)DS 8)BH

Какой из регистров указывает на смещение в сегменте кода программы: 1)IP 2)SР и ВР 3)АХ 4)BX, SI, DI

Какие из регистров могут указывать на смещение в сегменте стека: 1)IР 2)SР и ВР 3)АХ 4)BX, SI, DI

Что такое «полный указатель».

Из каких компонентов состоит адрес ЛЮБОЙ ячейки памяти:

Адреса сегмента данных и адреса текущего элемента данных;

Адреса сегмента и адреса смещения;

Адреса сегмента кода и адреса сегмента данных;

Каков может быть размер сегмента для 16-разрядного МП:

Вычислить физический адрес и представить его в b– и –h-кодах, если адрес сегмента =005Аh, а адрес смещения в сегменте = 0025h.

Приведите пример результата (в b-коде и формате байта) некоторой операции, выполненной в АЛУ, если известно, что флаг Р = 1.

Приведите значение флага Zвb-коде некоторой операции, выполненной в АЛУ, если известно, что результат этой операции вb-коде равен 00011100.

Литература.

Цилькер Б.Я. , Орлов С.А. Организация ЭВМ и систем.-Спб.: Питер, 2004.-668 с. Гл.1

Архитектура и программирование реального режима микропроцессоров фирмы Intel: Уч. пособие /Сост. Т. К. Щемелева; Перм. техн. ун-т. Пермь,2001. 96 c. Тема 4.

Любой из 4-х источников в следующем списке:

Абель П. Язык ассемблера для IBM PC и программирования. – М.: Высш. шк., 1992. 447 с.

Рудаков П.И., Финогенов К.И. Программируем на языке Ассемблера IBM PC . [B 4 ч]. –М.: Энтроп. Ч.1. Основы программирования. 1995. – 164 с

Юров В. Ассемблер. Учебник. 2000.

Юров В. и др. Accembler: [17 уроков для освоения языка]. СПб.: Питер. Ком, 1999. – 665 с.