3.3. Этапы выполнения программы

Выполнение программы состоит из следующих этапов работы ПК:

- чтение процессором из ОЗУ очередной команды,

- последующее чтение процессором из ОЗУ операнда и, при необходимости,- второго,

- исполнение в процессоре закодированной в команде операции,

- запись результата операции, при необходимости, в ОЗУ или в порт,

-

формирование адреса следующей команды и обращение за ней в ОЗУ.

При каждом чтении из ОЗУ процессор выставляет на ША адрес ячейки памяти, на ШУ - сигнал ”читать”, в ответ на которые ОЗУ выставляет на ШД, а процессор принимает содержимое ячейки памяти как очередную команду или операнд. При каждой записи в ОЗУ (например, при сохранении результата операции), процессор выставляет на ША адрес ячейки памяти, на ШУ - сигнал ”записать”, в ответ на которые ОЗУ принимает с ШД в указанную шиной адреса ячейку.

Как следует из адресного принципа, если команды программы расположены в ячейках памяти с последовательно возрастающими адресами, для перехода к следующей команде достаточно в процессоре увеличить адрес предыдущей команды и выставить его на ША. Это автоматическое изменение адресов команд и составляет основу автоматического управления ходом вычислительного процесса в ЭВМ.

3.4. Структурная организация процессора.

. Основные типы логических схем аппаратуры ЭВМ Преобразование информации в ЭВМ выполняется при помощи электронных схем, имеющих различную сложность. По функциональной сложности принято делить электронные схемы ВТ на элементы, узлы (блоки) и устройства.

3.4.1. Логические элементы.

Элемент - это простейшая схема, выполняющая операции над значениями двоичных разрядов (битами). Основные элементы делятся на логические и элементы памяти. Логические элементы выполняют двоичные (бинарные) операции, на основе которых осуществляются практически все преобразования информации. В качестве логических элементов используются элементы И, ИЛИ, НЕ и другие, производные от них - И-НЕ, ИЛИ-НЕ, И-ИЛИ-НЕ и т.д. Элементы памяти чаще всего представляют собой триггеры различных типов, но любой триггер хранит только один двоичный разряд.. Кроме логических элементов используются и вспомогательные элементы, усиливающие или формирующие сигналы стандартной формы, но, как правило, не выполняющие никаких логических функций. Элементы и триггеры обозначаются так, как показано на рис.3.6 а): элемент изображается прямоугольником, входы - линиями слева, выходы – справа.

3.4.2. Узлы

Узлы (функциональные блоки, далее - просто блоки) состоят из элементов и выполняют операции преобразования информации над байтами или структурами, состоящими из нескольких байтов, называемых словами. В зависимости от состава узлы могут быть 2-х типов: комбинационного (комбинационные схемы — КС) или накапливающего (автоматы , схемы с памятью, последовательные схемы).

1) Узлы комбинационного типа состоят из логических элементов. Их главная особенность заключается в том, что выходной сигнал (Y) в момент времени t зависит только от комбинации входных сигналов (X) в тот же момент времени, при этом каждой комбинации сигналов на входе соответствует определенный выходной сигнал. Выходной сигнал может измениться только при получении другого входного сигнала. При неоднократном повторении одного и того же входного сигнала значение выходного также повторяется, поэтому комбинационная схема фактически осуществляет перекодировку входных сигналов в выходные. Несмотря на кажущуюся примитивность логики работы комбинационных схем, все основные преобразования информации в ЭВМ выполняются с их помощью. Это объясняется тем, что в основе преобразования данных в ВТ заложено выполнение логических или арифметических операций. К типовым узлам ВТ комбинационного типа, сумматоры, дешифраторы, компараторы, мультиплексоры и др.

2) Узлы с памятью (автоматы) состоят из логических элементов и элементов памяти. Информация, записанная в памяти автомата, называется состоянием автомата (Q). Выходной сигнал автомата в общем случае зависит от сигнала на входе и состояния автомата, поэтому при одном и том же входном сигнале, но в разные моменты времени автомат может выдавать различные выходные сигналы. При работе автомата в его памяти накапливается обобщенная информация обо всех входных сигналах, поступивших к данному моменту времени, поэтому состояние автомата и выходной сигнал зависят от всей предыстории входных сигналов. Наличие памяти позволяет автомату выполнять не только отдельные операции, но и последовательности взаимосвязанных операций, т.е. заданные алгоритмы обработки данных. К типовым узлам ВТ с памятью относятся регистры и счетчики. Обозначения узлов в схемах ЭВМ аналогично обозначениям элементов. Например, обозначение суммирующего n-разрядного счетчика с прямыми и инверсными выходами – на рис. 3.6. б. На вход, обозначенный как +1, поступают суммируемые логические сигналы (единицы), с выхода счетчика Q, состоящего из n выходных линий, снимается состояние счетчика в виде n – разрядного двоичного кода.

Несколько узлов могут объединяться в функциональные блоки (например, блок сумматора может включать в себя собственно сумматор и регистр сумматора).

n

Q

n

а) б)

Рис.3.6.а) и б)

3.4.3..Устройства ЭВМ.

Строятся из элементов и узлов и выполняют определенный набор однотипных операций. К устройствам, например, компьютера относятся запоминающие устройства, арифметико-логическое устройство, центральное устройство управления, устройства ввода и вывода. Устройства ВТ конструктивно выполняют отдельно или несколько устройств объединяют в один конструктивный блок (например, процессор ЭВМ).

Для понимания организации средств ВТ и процессов преобразования информации в них необходимо изучить логику работы его составных частей, прежде всего состав и работу элементов и типовых узлов.

Процессор является основным «мозговым» устройством ЭВМ, в задачу которого входит исполнение находящегося в памяти программного (исполняемого) кода, который получается в результате трансляции текста программы на каком-либо языке программирования. В настоящее время под словом процессор обычно подразумевают МП – микросхему, которая, помимо соответственно процессора, может содержать и другие узлы. Процессор ЭВМ объединяет

-устройство управления (УУ);

- арифметико-логическое устройство (АЛУ);

- блоки регистров.

3.4.4. Типовые узлы и устройства аппаратуры ЭВМ

3.4.4.1. Регистры предназначены для приема, временного хранения и выдачи данных. Регистр – основная схема хранения информации в процессоре, контроллере, адаптере и порту ЭВМ всех классов и типов. Кроме хранения данных регистры могут выполнять сдвиг данных, по этой причине различают регистры параллельные и сдвигающие. На основе регистра строят схемы счета единиц (нулей). Основу регистра составляют триггеры, число которых равно разрядности хранимых в регистре данных, т.е. n-разрядный двоичный код хранится в n- разрядном регистре.

Параллельным называют . n-разрядный регистр с одновременной (т.е. параллельной записью.) записью в него всех n разрядов двоичного кода. Параллельный регистр имеет наиболее простую схему. Обычно именно его называют просто регистром. Обычно регистр имеет один общий вход сброса (установки в 0) и n входов записываемого в него двоичного кода

3.4.4.2. Счетчиком называется регистр, который «считает» входные сигналы, т.е. под действием каждого входного сигнала хранимый двоичный код изменяется на «1». . Счетчики могут считать с различными коэффициентами пересчета. Счетчики, считающие с коэффициентом пересчета 2n , где n –число триггеров, называются двоичными.

В зависимости от направления счета счетчики могут быть суммирующими, вычитающими и реверсивными. Суммирующие счетчики при поступлении каждого входного импульса увеличивают показания (состояния каждого триггера, т.е. состояние счетчика) на единицу, вычитающие – уменьшают. Принято обозначать вход суммирующего счетчика «+1», а вычитающего - «-1» . Реверсивные счетчики могут работать как в режиме – суммирования, так и в режиме вычитания.

3.4.3. Арифметико-логическое устройство (АЛУ) предназначено для выполнения арифметических и логических операций над данными разного формата. В зависимости от характера выполняемой операций и формата данных различают следующие типы операций в АЛУ:

-

арифметические операции над целыми числами с ФТ (операции целочисленной арифметики);

-

арифметические операции над числами с ПТ;

-

арифметические операции над двоично-десятичными числами (операции десятичной арифметики);

-

логические операции.

В зависимости от набора операций и особенностей реализации алгоритмов их выполнения организация АЛУ может быть различной.

По характеру использования различают многофункциональные и блочные АЛУ. В многофункциональных АЛУ все операции выполняются с использованием в основном одних и тех же аппаратных средств, которые настраиваются на заданный тип операций с помощью для управляющих сигналов. Обратим внимание, что входы АЛУ для управляющих сигналов (а значит и сами сигналы) на схемах АЛУ в этой лекции не показаны. Блочные АЛУ включают в себя отдельные блоки для операций различного типа. Эти блоки могут работать параллельно, что повышает быстродействие АЛУ, однако требует больших затрат на оборудование.

На входы АЛУ поступают операнды, а на его выходе формируется результат преобразования операндов (результат операции). В ходе выполнения операции АЛУ выдает признаки (условия), характеризующие результат. К таким признакам относятся, например, знак результата, равенство результата нулю, значение цифры множителя при умножении, знак остатка при делении и т.д.

АЛУ состоит из комбинационных схем, поэтому в операциях над двумя операндами оба операнда должны устанавливаться на обоих входах АЛУ одновременно! Основу АЛУ составляет двоичный сумматор, т.к. сложение двоичных дополнительных или обратных кодов составляет основу 4-х арифметических операций: сложение, вычитание, умножение, деление. В зависимости от числа магистралей различают трех-, двух- и одномагистральные (3-,2-,1-шинные) АЛУ.

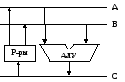

а) Трехмагистральное АЛУ

Структура трехмагистрального АЛУ (рис.3.7) позволяет выполнить за один такт чтение операндов из регистров, их суммирование в АЛУ и запись суммы в регистр. Однако три магистрали занимают значительную часть кристалла микросхемы.

Рис.3.7. Трехмагистральное АЛУ:

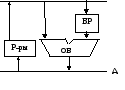

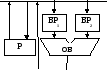

б)Двухмагистральное АЛУ

Двухмагистральные АЛУ (рис.3.8.) содержит буферный (промежуточный) регистр (БР) и требует для сложения двух машинных тактов. В первом такте по магистрали В из Регистра в БР считывается операнд В. Во втором такте операнд А по той же освободившейся от операнда В магистрали В считывается из Регистра на вход АЛУ, операнды А и В суммируются и результат по магистрали А записывается в РОН.

В

В

Рис.3.8. Двухмагистральное АЛУ

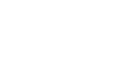

в) Одномагистральное АЛУ

Одномагистральное АЛУ использует два буферных регистра (рис.3.9.). В таком АЛУ сложение выполняется за три такта. В первом такте осуществляется чтение операнда А из Р в БР1, во втором - операнда В из Р в БР2, а в третьем суммируются операнды; результат записывается в один из регистров блока Р.

:

Рис 3.9. Одномагистральное АЛУ

Контрольные вопросы и задания:

1) Нарисуйте блочную схему алгоритма операции вычитания в одномагистральном АЛУ.

2) Составьте 5-8 простых и 5-8 сложных ( на Ваш взгляд ) вопросов и заданий по теме лекции.