СПЭ и МСвП лаб 2

.docxМинистерство образования Российской Федерации

Санкт-Петербургский государственный электротехнический

университет “ЛЭТИ”

Кафедра ЭУТ

Отчет по лабораторной работе № 2

«Изучение работы 8-миразрядных микропроцессоров (Z80)».

|

|

Санкт-Петербург2015

|

Цель работы — ознакомиться с функционированием восьмиразрядных микропроцессоров на примере выполнения команд микропроцессором Z80.

Описание микропроцессора Z80.

Микропроцессор Z80 является типичным представителем серии восьмиразрядных однокристальных микропроцессоров, предназначенных для построения различных вычислительных и управляющих устройств.

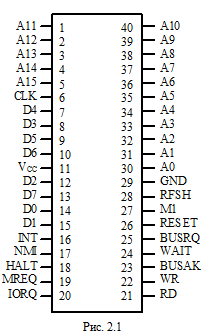

Схема расположения

выводов Z80 показана на рис. 2.1. Здесь

D0–D7 – восьмиразрядная шина данных;

A0–A15 – шестнадцатиразрядная шина

адреса; M1 – (машинный цикл 1) низкий

уровень указывает, что процессор

находится в состоянии выборки кода

операции; MREQ, IORQ – состояния машинного

цикла (операции чтения/записи памяти M

или внешних устройств IO); RD – управление

чтением; WR – управление записью; WAIT

– вход сигнала, низкий уровень которого

задерживает работу процессора на целое

число циклов; BUSRQ – вход сигнала запроса

использования шин адреса и данных;

BUSAK – выход сигнала, высокий уровень

которого указывает, что процессор

перевел шины в состояние высокого

импеданса; INT, NMI – входы сигналов

прерываний; HALT – выходной сигнал,

указывающий на то, что выполнена команда

останова; RESET – вход сигнала.

Описание лабораторного стенда

Схема стенда представлена на рис. 2.2. Здесь CPU – микропроцессор Z80, линии шины данных которого D0–D7 через резисторы R1–R8 подсоединены к шине питания + 5 В. Высокий уровень на входных линиях CPU (BUSRQ, WAIT, RESET, NMI, INT) также получен путем подсоединения их через резисторы к шине питания. Вывод М1 подведен к клемме “СИНХР.” для синхронизации осциллографа. Сигнал тактовой частоты от генератора G подан на вход CLK микропроцессора. Сброс CPU может осуществляться нажатием кнопки К (подача нулевого уровня на вход RESET).

В ходе лабораторной работы были сняты временные диаграммы следующих сигналов: CLK, M1, RD, WR, RFSH, D0–D7,А0–А15. Они представлены на рисунке 2.3 Временные диаграммы были сняты с соблюдением временных соотношений между фронтами этих сигналов.

Рис. 2.3

Описание сигналов с выводов микропроцессора:

Vcc – напряжение питания +5 В; GND – общий вывод; CLK – тактовый вход. Выводы D0-D7 – информационная шина; A0-A15 – адресная шина. Оставшиеся выводы присоединены к линиям, которые несут управляющие сигналы.

RD – линия считывания – становиться активной, когда байт информации должен быть считан из памяти или порта.

WR – линия записи – активна, когда байт информации должен быть записан в память или порт.

MREQ – состояния машинного цикла, запрос памяти – активно в тех случаях, когда требуется обращение к памяти.

Байт информации считывается из памяти в соответствии с адресом, помещенным на адресной шине. Далее, в соответствии с откликом на сигналы RD и MREQ, байт информации поступает на информационную шину, с которой эта информация в дальнейшем считывается микропроцессором. Для записи байта данных в память микропроцессор помещает требуемые адреса на адресную шину и требуемую информацию на шину данных. Сигналы MREQ и WR активизируются, и байт данных записывается в память.

RFSH - линия регенерации - используется для регенерации динамической памяти.

M1- активизируется при выполнении машинного цикла и показывает, что проходящий машинный цикл обработки команды находится в состоянии “ввода кода операции” при выполнении некоторой команды. Сигнал М1 при выполнении двухбайтовой команды формируется при вызове каждого байта кода операции. Сигнал M1 появляется вместе с сигналом IORQ в цикле приема прерывания. Выборка инструкции требует, чтобы все три сигнала MI, MREQ и RD были активизированы. В то же время выборка байта данных из ячейки памяти требует, чтобы только MREQ и RD были активизированы.

lORQ - линия выход - активна при выполнении команд IN или OUT.

HALT – останов; BUSRQ - линия запроса.

Z-80 позволяет внешним устройствам использовать адресную и информационную шину в режиме пропуска цикла. Запрос микропроцессору пропустить следующий цикл выполняется внешними устройствами путем активизации этой линии (BUSAK – линия подтверждения).

Оставшиеся 4 вывода находятся под контролем пользователя.

RESET - линия сброса - используется для инициализации микропроцессора, активизируется при включении питания. Сброс может быть осуществлен соединением линий RESET и GND.

WAIT - линия ожидания. “Медленная” память может требовать большего времени для цикла считывания или записи и об этом сообщает микропроцессору путем активизации линии WAIT.

NMI - “немаскируемое прерывание”. Активизация этой линии приводит к остановке выполнения микропроцессором текущей программы, и вместо нее микропроцессор выполняет программу прерывания, записанную специально для этой цели.

INT- “маскируемое прерывание”.

Анализируя временные диаграммы, снятые при проведении лабораторной работы и зная, что низкий уровень сигнала M1 характеризует состояние чтения кода операции, а также что на восьмиразрядной шине данных в этот момент находятся следующие данные: 1111 11112 = FFh,

соответствующие команде RST 7, можно сделать вывод, что МП выполняет эту команду.

При выполнении этой команды этот адрес фиксирован и определяется следующим образом: adr=N*8, где N – номер команды (0..7) – нашем случае N = 7.

adr=7*8 = 5610=001110002=0038h,

Выводы: Ознакомились со схемой 8-миразрядного микропроцессора Z80, сняли и проанализировали временные диаграммы сигналов на выходах процессора.