- •Contents

- •1. Video and Image Processing Suite Overview

- •Release Information

- •Device Family Support

- •Latency

- •In-System Performance and Resource Guidance

- •Stall Behavior and Error Recovery

- •2. Interfaces

- •Video Formats

- •Avalon-ST Video Protocol

- •Video Data Packets

- •Static Parameters of Video Data Packets

- •Control Data Packets

- •Ancillary Data Packets

- •User-Defined and Altera-Reserved Packets

- •Packet Propagation

- •Transmission of Avalon-ST Video Over Avalon-ST Interfaces

- •Packet Transfer Examples

- •Avalon-MM Slave Interfaces

- •Specification of the Type of Avalon-MM Slave Interfaces

- •Avalon-MM Master Interfaces

- •Specification of the Type of Avalon-MM Master Interfaces

- •Buffering of Non-Image Data Packets in Memory

- •3. Getting Started

- •IP Catalog and Parameter Editor

- •Specifying IP Core Parameters and Options

- •Installing and Licensing IP Cores

- •OpenCore Plus IP Evaluation

- •4. Clocked Video Interface IP Cores

- •Control Port

- •Clocked Video Input Format Detection

- •Interrupts

- •Clocked Video Output Video Modes

- •Interrupts

- •Generator Lock

- •Underflow and Overflow

- •Timing Constraints

- •Handling Ancillary Packets

- •Modules for Clocked Video Input II IP Core

- •Clocked Video Interface Parameter Settings

- •Clocked Video Interface Signals

- •Clocked Video Interface Control Registers

- •5. 2D FIR Filter IP Core

- •Calculation Precision

- •Coefficient Precision

- •Result to Output Data Type Conversion

- •2D FIR IP Core Parameter Settings

- •2D FIR Filter Signals

- •2D FIR Filter Control Registers

- •6. Video Mixing IP Cores

- •Alpha Blending

- •Video Mixing Parameter Settings

- •Video Mixing Signals

- •Video Mixing Control Registers

- •7. Chroma Resampler IP Core

- •Horizontal Resampling (4:2:2)

- •Vertical Resampling (4:2:0)

- •Chroma Resampler Parameter Settings

- •Chroma Resampler Signals

- •8. Video Clipping IP Cores

- •Video Clipping Parameter Settings

- •Video Clipping Signals

- •Video Clipping Control Registers

- •9. Color Plane Sequencer IP Core

- •Combining Color Patterns

- •Rearranging Color Patterns

- •Splitting and Duplicating

- •Subsampled Data

- •Color Plane Sequencer Parameter Settings

- •Color Plane Sequencer Signals

- •10. Color Space Conversion IP Cores

- •Input and Output Data Types

- •Color Space Conversion

- •Result of Output Data Type Conversion

- •Color Space Conversion Parameter Settings

- •Color Space Conversion Signals

- •Color Space Conversion Control Registers

- •11. Control Synchronizer IP Core

- •Using the Control Synchronizer IP Core

- •Control Synchronizer Parameter Settings

- •Control Synchronizer Signals

- •Control Synchronizer Control Registers

- •12. Deinterlacing IP Cores

- •Deinterlacing Methods

- •Bob with Scanline Duplication

- •Bob with Scanline Interpolation

- •Weave

- •Motion-Adaptive

- •Sobel-Based HQ Mode

- •Pass-Through Mode for Progressive Frames

- •Frame Buffering

- •Frame Rate Conversion

- •Bandwidth Requirement Calculations for 10-bit YCbCr Video

- •Behavior When Unexpected Fields are Received

- •Handling of Avalon-ST Video Control Packets

- •Deinterlacing Parameter Settings

- •Deinterlacing Signals

- •Deinterlacing Control Registers

- •Design Guidelines for Broadcast Deinterlacer IP Core

- •13. Frame Reader IP Core

- •Single-Cycle Color Patterns

- •Frame Reader Output Pattern and Memory Organization

- •Frame Reader Parameter Settings

- •Frame Reader Signals

- •Frame Reader Control Registers

- •14. Frame Buffer IP Cores

- •Double Buffering

- •Triple Buffering

- •Locked Frame Rate Conversion

- •Handling of Avalon-ST Video Control Packets

- •Color Format

- •Frame Buffer Parameter Settings

- •Frame Buffer Signals

- •Frame Buffer Control Registers

- •15. Gamma Corrector IP Core

- •Gamma Corrector Parameter Settings

- •Gamma Corrector Signals

- •Gamma Corrector Control Registers

- •16. Interlacer IP Core

- •Interlacer Parameter Settings

- •Interlacer Signals

- •Interlacer Control Registers

- •17. Scaler II IP Core

- •Nearest Neighbor Algorithm

- •Bilinear Algorithm

- •Bilinear Algorithmic Description

- •Polyphase and Bicubic Algorithm

- •Double-Buffering

- •Polyphase Algorithmic Description

- •Choosing and Loading Coefficients

- •Edge-Adaptive Scaling Algorithm

- •Scaler II Parameter Settings

- •Scaler II Signals

- •Scaler II Control Registers

- •18. Video Switching IP Cores

- •Mixer Layer Switching

- •Video Switching Parameter Settings

- •Video Switching Signals

- •Video Switching Control Registers

- •19. Test Pattern Generator IP Cores

- •Test Pattern

- •Generation of Avalon-ST Video Control Packets and Run-Time Control

- •Test Pattern Generator Parameter Settings

- •Test Pattern Generator Signals

- •Test Pattern Generator Control Registers

- •20. Trace System IP Core

- •Trace System Parameter Settings

- •Trace System Signals

- •Operating the Trace System from System Console

- •Loading the Project and Connecting to the Hardware

- •Trace Within System Console

- •TCL Shell Commands

- •21. Avalon-ST Video Monitor IP Core

- •Packet Visualization

- •Monitor Settings

- •Avalon-ST Video Monitor Parameter Settings

- •Avalon-ST Video Monitor Signals

- •Avalon-ST Video Monitor Control Registers

- •Avalon-ST Video Class Library

- •Running the Tests

- •Video File Reader Test

- •Example Test Environment

- •Video Field Life Cycle

- •Constrained Random Test

- •Complete Class Reference

- •c_av_st_video_control

- •c_av_st_video_data

- •c_av_st_video_file_io

- •c_av_st_video_item

- •c_av_st_video_source_sink_base

- •c_av_st_video_sink_bfm_’SINK

- •c_av_st_video_source_bfm_’SOURCE

- •c_av_st_video_user_packet

- •c_pixel

- •Raw Video Data Format

- •Cadence Detection and Reverse Pulldown in the Deinterlacer II IP Core

- •Document Revision History

- •How to Contact Altera

UG-VIPSUITE |

Avalon-ST Video Protocol |

2-7 |

|

2015.01.23 |

|||

|

|

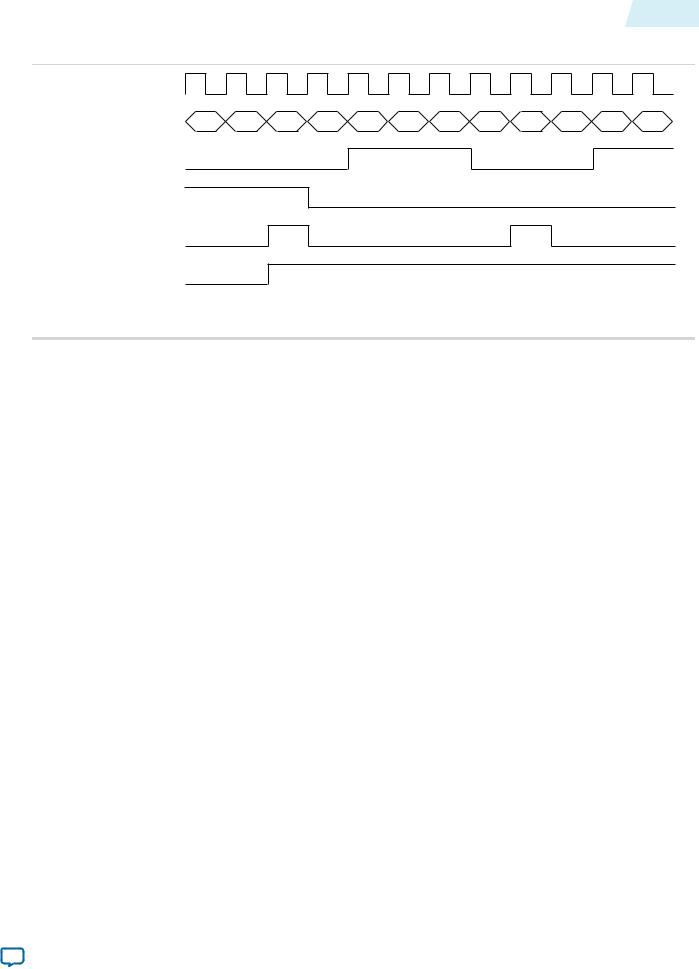

Figure 2-6: Separate Synchronization Signals Timing Diagram

vid_data |

D0 |

D1 |

DN |

Dn+1 Dn+2 |

vid_de/vid_datavalid (1)

vid_v_sync

vid_h_sync

vid_f

(1): vid_datavalid: Clocked Video Output IP core vid_de: Clocked Video Input IP core

The CVI IP cores only read the vid_data, vid_de, vid_h_sync, vid_v_sync, and vid_f signals when vid_datavalid is 1. This allows the CVI IP cores to support oversampling where the video clock is running at a higher rate than the pixel clock.

Video Locked Signal

The vid_locked signal indicates that the clocked video stream is active. When the signal has a value of 1, the CVI IP cores take the input clocked video signals as valid, and read and process them as normal. When the signal has a value of 0 (if for example the video cable is disconnected or the video interface is not receiving a signal):

•Clocked Video Input IP core: The IP core takes the input clocked video signals as invalid and do not process them.

•Clocked Video Input II IP core: The vid_clk domain registers of the IP core are held in reset and no video is processed. The control and Avalon-ST Video interfaces are not held in reset and will respond as normal. The vid_locked signal is synchronized internally to the IP core and is asynchronous to the

vid_clk.

If the vid_locked signal goes invalid while a frame of video is being processed, the CVI IP cores end the frame of video early.

Avalon-ST Video Protocol

The Avalon-ST Video protocol is a packet-oriented way to send video and control data over Avalon-ST connections. The IP cores in the Video and Image Processing Suite use the Avalon-ST Video protocol.

Using the Avalon-ST Video protocol allows the construction of image processing data paths which automatically configure to changes in the format of the video being processed. This minimizes the external control logic required to configure a video system.

Interfaces |

Altera Corporation |

|

|

Send Feedback

2-8 |

Avalon-ST Video Protocol |

|

|

|

|

|

UG-VIPSUITE |

||||

|

|

|

|

2015.01.23 |

|||||||

|

|

|

|

|

|

|

|

|

|||

|

Table 2-3: Avalon-ST Video Protocol Parameters |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Parameter Values |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IP Cores |

|

Frame Width/ |

|

Interlaced/ |

|

Bits per Color |

|

Color Pattern |

|

|

|

|

|

Height |

|

Progressive |

|

Sample |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2D FIR Filter |

|

User-defined— |

|

Progressive |

|

User-defined— |

|

One, two, or three |

|

|

|

|

|

through |

|

|

|

through |

|

channels in sequence. |

|

|

|

|

|

parameter editor |

|

|

|

parameter editor |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Alpha Blending Mixer |

|

Run-time |

|

Progressive |

|

User-defined— |

|

• din and dout: One, |

|

|

|

|

|

controlled |

|

|

|

through |

|

two or three |

|

|

|

|

|

|

|

|

|

parameter editor |

|

channels in |

|

|

|

|

|

|

|

|

|

Specified |

|

sequence |

|

|

|

|

|

|

|

|

|

separately for |

|

• alpha_in: A single |

|

|

|

|

|

|

|

|

|

image data and |

|

color plane |

|

|

|

|

|

|

|

|

|

alpha blending. |

|

representing the |

|

|

|

|

|

|

|

|

|

|

|

alpha value for each |

|

|

|

|

|

|

|

|

|

|

|

pixel |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Mixer II |

|

No run-time |

|

Progressive |

|

User-defined— |

|

Two or three channels |

|

|

|

|

|

control |

|

|

|

through |

|

in parallel. |

|

|

|

|

|

|

|

|

|

parameter editor |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Chroma Resampler |

|

Run-time |

|

Progressive |

|

User-defined— |

|

User-defined—through |

|

|

|

|

|

controlled |

|

|

|

through |

|

parameter editor |

|

|

|

|

|

|

|

|

|

parameter editor |

|

|

|

|

|

Clipper/Clipper II |

|

Run-time |

|

Either one— |

|

User-defined— |

|

Any combination of |

|

|

|

|

|

controlled |

|

interlaced inputs |

|

through |

|

one, two, three, or four |

|

|

|

|

|

|

|

are accepted but |

|

parameter editor |

|

channels in each of |

|

|

|

|

|

|

|

treated as |

|

|

|

sequence or parallel. |

|

|

|

|

|

|

|

progressive |

|

|

|

|

|

|

|

|

|

|

|

inputs. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Color Plane Sequencer |

|

Run-time |

|

Either one |

|

User-defined— |

|

User-defined—through |

|

|

|

|

|

controlled |

|

|

|

through |

|

parameter editor |

|

|

|

|

|

|

|

|

|

parameter editor |

|

|

|

|

|

Color Space Converter |

|

Run-time |

|

Either one |

|

User-defined— |

|

Three color planes in |

|

|

|

|

|

controlled |

|

|

|

through |

|

parallel or sequence |

|

|

|

|

|

|

|

|

|

parameter editor |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Color Space Converter |

|

No run-time |

|

Either one |

|

User-defined— |

|

Three color planes in |

|

|

|

II |

|

control |

|

|

|

through |

|

parallel or sequence |

|

|

|

|

|

|

|

|

|

parameter editor |

|

|

|

|

|

Control Synchronizer |

|

Run-time |

|

Run-time |

|

User-defined— |

|

Up to four color planes |

|

|

|

|

|

controlled |

|

controlled |

|

through |

|

in parallel, with any |

|

|

|

|

|

|

|

|

|

parameter editor |

|

number of color planes |

|

|

|

|

|

|

|

|

|

|

|

in sequence. |

|

|

|

|

|

|

|

|

|

|

|

|

|

Altera Corporation |

Interfaces |

|

|

Send Feedback

UG-VIPSUITE |

|

|

|

|

|

Avalon-ST Video Protocol |

2-9 |

|||

2015.01.23 |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Parameter Values |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IP Cores |

|

Frame Width/ |

|

Interlaced/ |

|

Bits per Color |

|

Color Pattern |

|

|

|

|

Height |

|

Progressive |

|

Sample |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Deinterlacer |

|

Run-time |

|

Interlaced input |

|

User-defined— |

|

• One, two, or three |

|

|

|

|

controlled |

|

and progressive |

|

through |

|

channels in |

|

|

|

|

|

|

output (plus |

|

parameter editor |

|

sequence |

|

|

|

|

|

|

optional |

|

|

|

• alpha_in: A single |

|

|

|

|

|

|

passthrough |

|

|

|

|

|

|

|

|

|

|

|

|

|

color plane |

|

|

|

|

|

|

|

mode for |

|

|

|

|

|

|

|

|

|

|

|

|

|

representing the |

|

|

|

|

|

|

|

progressive |

|

|

|

|

|

|

|

|

|

|

|

|

|

alpha value for each |

||

|

|

|

|

|

input) |

|

|

|

||

|

|

|

|

|

|

|

|

pixel |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Deinterlacer II |

|

Run-time |

|

Interlaced input |

|

User-defined— |

|

Any combination of |

|

|

|

|

controlled |

|

and progressive |

|

through |

|

two or three channels |

|

|

|

|

|

|

output (plus |

|

parameter editor |

|

in each of parallel. |

|

|

|

|

|

|

passthrough |

|

|

|

|

|

|

|

|

|

|

mode for |

|

|

|

|

|

|

|

|

|

|

progressive |

|

|

|

|

|

|

|

|

|

|

input) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Broadcast Deinterlacer |

|

Run-time |

|

Interlaced input |

|

User-defined— |

|

Two channels in |

|

|

|

|

controlled |

|

and progressive |

|

through |

|

parallel (4:2:2 only) |

|

|

|

|

|

|

output (plus |

|

parameter editor |

|

|

|

|

|

|

|

|

passthrough |

|

|

|

|

|

|

|

|

|

|

mode for |

|

|

|

|

|

|

|

|

|

|

progressive |

|

|

|

|

|

|

|

|

|

|

input) |

|

|

|

|

|

|

Frame Reader |

|

User-defined— |

|

User-defined— |

|

User-defined— |

|

Up to four color planes |

|

|

|

|

through Avalon- |

|

through Avalon- |

|

through |

|

in parallel, with up to |

|

|

|

|

MM slave |

|

MM slave |

|

parameter editor |

|

three color planes in |

|

|

|

|

control port |

|

control port |

|

|

|

sequence. |

|

|

|

|

|

|

|

|

|

|

|

|

|

Frame Buffer |

|

Run-time |

|

Progressive; in |

|

User-defined— |

|

Any combination of |

|

|

|

|

controlled |

|

some cases |

|

through |

|

one, two, three, or four |

|

|

|

|

|

|

interlaced data |

|

parameter editor |

|

channels in each of |

|

|

|

|

|

|

accepted |

|

|

|

sequence or parallel. |

|

|

Frame Buffer II |

|

No run-time |

|

Progressive |

|

User-defined— |

|

Any combination of |

|

|

|

|

control |

|

inputs only |

|

through |

|

one, two, three, or four |

|

|

|

|

|

|

|

|

parameter editor |

|

channels in each of |

|

|

|

|

|

|

|

|

|

|

parallel. |

|

|

|

|

|

|

|

|

|

|

|

|

|

Gamma Corrector |

|

Run-time |

|

Either one |

|

User-defined— |

|

One, two or three |

|

|

|

|

controlled |

|

|

|

through |

|

channels in sequence |

|

|

|

|

|

|

|

|

parameter editor |

|

or parallel. |

|

|

|

|

|

|

|

|

|

|

|

|

Interfaces |

Altera Corporation |

|

|

Send Feedback

2-10 |

Avalon-ST Video Protocol |

|

|

|

|

|

UG-VIPSUITE |

||||

|

|

|

|

2015.01.23 |

|||||||

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Parameter Values |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IP Cores |

|

Frame Width/ |

|

Interlaced/ |

|

Bits per Color |

|

Color Pattern |

|

|

|

|

|

Height |

|

Progressive |

|

Sample |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Interlacer |

|

Run-time |

|

Progressive; |

|

User-defined— |

|

One, two or three |

|

|

|

|

|

controlled |

|

interlaced data is |

|

through |

|

channels in sequence |

|

|

|

|

|

|

|

either discarded |

|

parameter editor |

|

or parallel. |

|

|

|

|

|

|

|

or propagated |

|

|

|

|

|

|

|

|

|

|

|

without change |

|

|

|

|

|

|

|

|

|

|

|

in parameter |

|

|

|

|

|

|

|

|

|

|

|

editor |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Test Pattern Generator |

|

User-defined— |

|

User-defined— |

|

User-defined— |

|

One, two or three |

|

|

|

|

|

through |

|

through |

|

through |

|

channels in sequence |

|

|

|

|

|

parameter editor |

|

parameter editor |

|

parameter editor |

|

or parallel. |

|

|

|

|

|

or run-time |

|

|

|

|

|

|

|

|

|

|

|

controlled |

|

|

|

|

|

|

|

|

|

Test Pattern Generator |

|

User-defined— |

|

User-defined— |

|

User-defined— |

|

RGB 4:4:4 or YCbCr |

|

|

|

II |

|

through |

|

through |

|

through |

|

4:4:4, 4:2:2 or 4:2:0 in |

|

|

|

|

|

parameter editor |

|

parameter editor |

|

parameter editor |

|

parallel or sequence. |

|

|

|

|

|

or run-time |

|

|

|

|

|

|

|

|

|

|

|

controlled |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Packets

The packets of the Avalon-ST Video protocol are split into symbols—each symbol represents a single piece of data. For all packet types on a particular Avalon-ST interface, the number of symbols sent in parallel (that is, on one clock cycle) and the bit width of all symbols is fixed. The symbol bit width and number of symbols sent in parallel defines the structure of the packets.

The functions predefine the following three types of packet:

•Video data packets containing only uncompressed video data

•Control data packets containing the control data configure the cores for incoming video data packets

•Ancillary (non-video) data packets containing ancillary packets from the vertical blanking period of a video frame

Another seven packet types are reserved for users, and five packet types reserved for future definition by Altera.

The packet type is defined by a 4-bit packet type identifier. This type identifier is the first value of any packet. It is the symbol in the least significant bits of the interface. Functions do not use any symbols in parallel with the type identifier.

Table 2-4: Avalon-ST Video Packet Types

Type Identifier |

|

Description |

|

|

|

0 |

|

Video data packet |

|

|

|

1–8 |

|

User packet types |

|

|

|

9–12 |

|

Reserved for future Altera use |

|

|

|

Altera Corporation |

Interfaces |

|

|

Send Feedback