- •Contents

- •1. Video and Image Processing Suite Overview

- •Release Information

- •Device Family Support

- •Latency

- •In-System Performance and Resource Guidance

- •Stall Behavior and Error Recovery

- •2. Interfaces

- •Video Formats

- •Avalon-ST Video Protocol

- •Video Data Packets

- •Static Parameters of Video Data Packets

- •Control Data Packets

- •Ancillary Data Packets

- •User-Defined and Altera-Reserved Packets

- •Packet Propagation

- •Transmission of Avalon-ST Video Over Avalon-ST Interfaces

- •Packet Transfer Examples

- •Avalon-MM Slave Interfaces

- •Specification of the Type of Avalon-MM Slave Interfaces

- •Avalon-MM Master Interfaces

- •Specification of the Type of Avalon-MM Master Interfaces

- •Buffering of Non-Image Data Packets in Memory

- •3. Getting Started

- •IP Catalog and Parameter Editor

- •Specifying IP Core Parameters and Options

- •Installing and Licensing IP Cores

- •OpenCore Plus IP Evaluation

- •4. Clocked Video Interface IP Cores

- •Control Port

- •Clocked Video Input Format Detection

- •Interrupts

- •Clocked Video Output Video Modes

- •Interrupts

- •Generator Lock

- •Underflow and Overflow

- •Timing Constraints

- •Handling Ancillary Packets

- •Modules for Clocked Video Input II IP Core

- •Clocked Video Interface Parameter Settings

- •Clocked Video Interface Signals

- •Clocked Video Interface Control Registers

- •5. 2D FIR Filter IP Core

- •Calculation Precision

- •Coefficient Precision

- •Result to Output Data Type Conversion

- •2D FIR IP Core Parameter Settings

- •2D FIR Filter Signals

- •2D FIR Filter Control Registers

- •6. Video Mixing IP Cores

- •Alpha Blending

- •Video Mixing Parameter Settings

- •Video Mixing Signals

- •Video Mixing Control Registers

- •7. Chroma Resampler IP Core

- •Horizontal Resampling (4:2:2)

- •Vertical Resampling (4:2:0)

- •Chroma Resampler Parameter Settings

- •Chroma Resampler Signals

- •8. Video Clipping IP Cores

- •Video Clipping Parameter Settings

- •Video Clipping Signals

- •Video Clipping Control Registers

- •9. Color Plane Sequencer IP Core

- •Combining Color Patterns

- •Rearranging Color Patterns

- •Splitting and Duplicating

- •Subsampled Data

- •Color Plane Sequencer Parameter Settings

- •Color Plane Sequencer Signals

- •10. Color Space Conversion IP Cores

- •Input and Output Data Types

- •Color Space Conversion

- •Result of Output Data Type Conversion

- •Color Space Conversion Parameter Settings

- •Color Space Conversion Signals

- •Color Space Conversion Control Registers

- •11. Control Synchronizer IP Core

- •Using the Control Synchronizer IP Core

- •Control Synchronizer Parameter Settings

- •Control Synchronizer Signals

- •Control Synchronizer Control Registers

- •12. Deinterlacing IP Cores

- •Deinterlacing Methods

- •Bob with Scanline Duplication

- •Bob with Scanline Interpolation

- •Weave

- •Motion-Adaptive

- •Sobel-Based HQ Mode

- •Pass-Through Mode for Progressive Frames

- •Frame Buffering

- •Frame Rate Conversion

- •Bandwidth Requirement Calculations for 10-bit YCbCr Video

- •Behavior When Unexpected Fields are Received

- •Handling of Avalon-ST Video Control Packets

- •Deinterlacing Parameter Settings

- •Deinterlacing Signals

- •Deinterlacing Control Registers

- •Design Guidelines for Broadcast Deinterlacer IP Core

- •13. Frame Reader IP Core

- •Single-Cycle Color Patterns

- •Frame Reader Output Pattern and Memory Organization

- •Frame Reader Parameter Settings

- •Frame Reader Signals

- •Frame Reader Control Registers

- •14. Frame Buffer IP Cores

- •Double Buffering

- •Triple Buffering

- •Locked Frame Rate Conversion

- •Handling of Avalon-ST Video Control Packets

- •Color Format

- •Frame Buffer Parameter Settings

- •Frame Buffer Signals

- •Frame Buffer Control Registers

- •15. Gamma Corrector IP Core

- •Gamma Corrector Parameter Settings

- •Gamma Corrector Signals

- •Gamma Corrector Control Registers

- •16. Interlacer IP Core

- •Interlacer Parameter Settings

- •Interlacer Signals

- •Interlacer Control Registers

- •17. Scaler II IP Core

- •Nearest Neighbor Algorithm

- •Bilinear Algorithm

- •Bilinear Algorithmic Description

- •Polyphase and Bicubic Algorithm

- •Double-Buffering

- •Polyphase Algorithmic Description

- •Choosing and Loading Coefficients

- •Edge-Adaptive Scaling Algorithm

- •Scaler II Parameter Settings

- •Scaler II Signals

- •Scaler II Control Registers

- •18. Video Switching IP Cores

- •Mixer Layer Switching

- •Video Switching Parameter Settings

- •Video Switching Signals

- •Video Switching Control Registers

- •19. Test Pattern Generator IP Cores

- •Test Pattern

- •Generation of Avalon-ST Video Control Packets and Run-Time Control

- •Test Pattern Generator Parameter Settings

- •Test Pattern Generator Signals

- •Test Pattern Generator Control Registers

- •20. Trace System IP Core

- •Trace System Parameter Settings

- •Trace System Signals

- •Operating the Trace System from System Console

- •Loading the Project and Connecting to the Hardware

- •Trace Within System Console

- •TCL Shell Commands

- •21. Avalon-ST Video Monitor IP Core

- •Packet Visualization

- •Monitor Settings

- •Avalon-ST Video Monitor Parameter Settings

- •Avalon-ST Video Monitor Signals

- •Avalon-ST Video Monitor Control Registers

- •Avalon-ST Video Class Library

- •Running the Tests

- •Video File Reader Test

- •Example Test Environment

- •Video Field Life Cycle

- •Constrained Random Test

- •Complete Class Reference

- •c_av_st_video_control

- •c_av_st_video_data

- •c_av_st_video_file_io

- •c_av_st_video_item

- •c_av_st_video_source_sink_base

- •c_av_st_video_sink_bfm_’SINK

- •c_av_st_video_source_bfm_’SOURCE

- •c_av_st_video_user_packet

- •c_pixel

- •Raw Video Data Format

- •Cadence Detection and Reverse Pulldown in the Deinterlacer II IP Core

- •Document Revision History

- •How to Contact Altera

UG-VIPSUITE |

|

|

|

Stall Behavior and Error Recovery |

1-11 |

|||||

2015.01.23 |

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

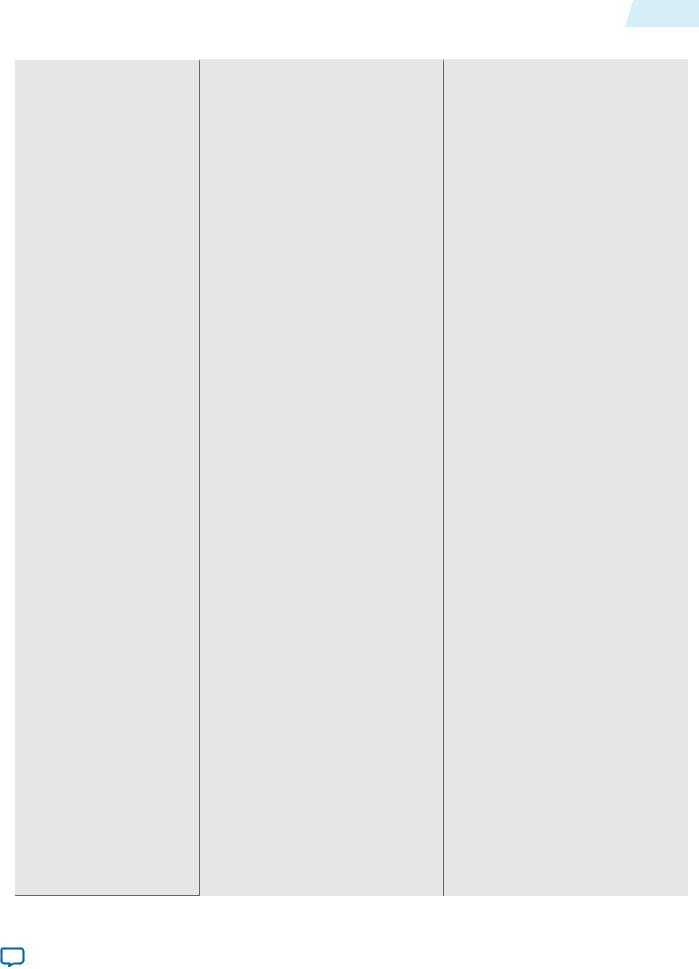

IP Core |

|

Configuration |

|

ALM |

|

RAM |

|

|

DSP |

|

|

|

|

|

|

|

|

|

|

|

|

Scaler II |

|

• Symbols in parallel = 3 |

|

1,010 |

|

12 |

|

|

12 |

|

|

|

• Scaling algorithm = Polyphase |

|

|

|

|

|

|

|

|

|

|

• Enable run-time control of input/output |

|

|

|

|

|

|

|

|

|

|

frame size = On |

|

|

|

|

|

|

|

|

|

|

• Vertical/horizontal filter taps = 4 |

|

|

|

|

|

|

|

|

|

|

• Vertical/horizontal filter phases = 14 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Test Pattern |

|

• Color space = RGB |

|

65 |

|

0 |

|

|

0 |

|

Generator |

|

• Run-time control of image size = Off |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Trace System |

|

• Buffer size = 8192 |

|

1,224 |

|

12 |

|

|

0 |

|

|

|

• Bit width of capture interface(s) = 32 |

|

|

|

|

|

|

|

|

|

|

• Number of inputs = 2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Stall Behavior and Error Recovery

The Video and Image Processing Suite IP cores do not continuously process data. Instead, they use flowcontrolled Avalon-ST interfaces, which allow them to stall the data while they perform internal calculations.

During control packet processing, the IP cores might stall frequently and read or write less than once per clock cycle. During data processing, the IP cores generally process one input or output per clock cycle. There are, however, some stalling cycles. Typically, these are for internal calculations between rows of image data and between frames/fields.

When stalled, an IP core indicates that it is not ready to receive or produce data. The time spent in the stalled state varies between IP cores and their parameterizations. In general, it is a few cycles between rows and a few more between frames.

If data is not available at the input when required, all of the IP cores stall, and thus do not output data. With the exceptions of the Deinterlacer and Frame Buffer in double or triple-buffering mode, none of the IP cores ever overlap the processing of consecutive frames. The first sample of frame F + 1 is not input until after the last sample of frame F has been output.

When the IP core receives an endofpacket signal unexpectedly (early or late), the IP cores recover from the error and prepare for the next valid packet (control or data).

Video and Image Processing Suite Overview |

Altera Corporation |

|

|

Send Feedback

1-12 |

Stall Behavior and Error Recovery |

|

UG-VIPSUITE |

|||||

2015.01.23 |

||||||||

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

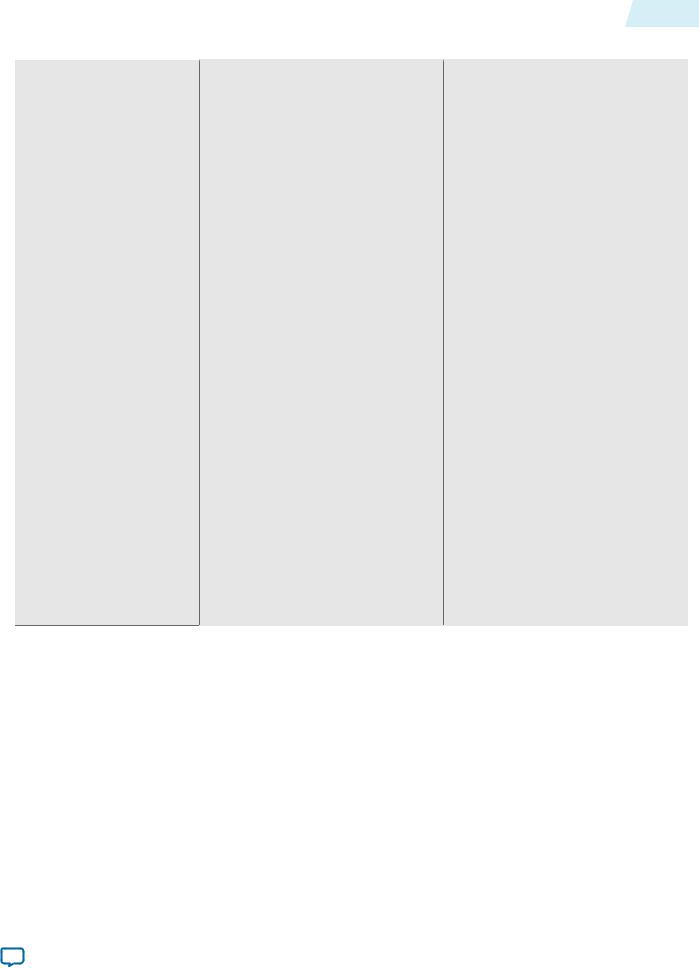

IP Core |

|

Stall Behavior |

|

Error Recovery |

|

|

|

|

|

|

|

|

|

|

|

|

|

2D FIR Filter |

|

• Has a delay of a little more than N–1 |

|

• Resolution is not configurable at |

||

|

|

|

|

lines between data input and output |

|

run time. |

||

|

|

|

|

in the case of a N×N 2D FIR Filter. |

|

• Does not read the control |

||

|

|

|

|

• Delay caused by to line buffering |

|

packets passed through it. |

||

|

|

|

|

internal to the IP core. |

|

An error condition occurs if an |

||

|

|

|

|

|

|

|||

|

|

|

|

|

|

endofpacket signal is received too |

||

|

|

|

|

|

|

early or too late for the compile time |

||

|

|

|

|

|

|

configured frame size. In either case, |

||

|

|

|

|

|

|

the 2D FIR Filter always creates |

||

|

|

|

|

|

|

output video packets of the |

||

|

|

|

|

|

|

configured size. |

||

|

|

|

|

|

|

• If an input video packet has a late |

||

|

|

|

|

|

|

endofpacket signal, then the |

||

|

|

|

|

|

|

extra data is discarded. |

||

|

|

|

|

|

|

• If an input video packet has an |

||

|

|

|

|

|

|

early endofpacket signal, then |

||

|

|

|

|

|

|

the video frame is padded with |

||

|

|

|

|

|

|

an undefined combination of the |

||

|

|

|

|

|

|

last input pixels. |

||

|

|

|

|

|

|

|

|

|

Altera Corporation |

Video and Image Processing Suite Overview |

|

|

Send Feedback

UG-VIPSUITE |

|

|

|

Stall Behavior and Error Recovery |

1-13 |

|

2015.01.23 |

|

|

|

|||

|

|

|

|

|

||

|

|

|

|

|

|

|

|

IP Core |

|

Stall Behavior |

|

Error Recovery |

|

|

|

|

|

|

|

|

Alpha Blending Mixer/

Mixer II

All modes stall for a few cycles after each output frame and between output lines.

Between frames, the IP core processes non-image data packets from its input layers in sequential order and may exert backpressure during the process until the image data header has been received for all its input.

During the mixing of a frame, the IP core:

•reads from the background input for each non-stalled cycle.

•reads from the input ports associated with layers that currently cover the background image.

Because of pipelining, the foreground pixel of layer N is read approximately N active cycles after the corresponding background pixel has been read.

•If the output is applying backpres sure or if one input is stalling, the pipeline stalls and the backpressure propagates to all active inputs.

•When alpha blending is enabled, one data sample is read from each alpha port once each time that a whole pixel of data is read from the corresponding input port.

There is no internal buffering in the IP core, so the delay from input to output is just a few clock cycles and increases linearly with the number of inputs.

The Alpha Blending Mixer IP core processes video packets from the background layer until the end of packet is received.

• If an endofpacket signal is received too early for the background layer, the IP core enters error mode and continues writing data until it has reached the end of the current line. The endofpacket signal is then set with the last pixel sent.

•If an endofpacket signal is received early for one of the foreground layers or for one of the alpha layers, the IP core stops pulling data out of the corresponding input and pads the incomplete frame with undefined samples.

•If an endofpacket signal is received late for the background layer, one or more foreground layers, or one or more alpha layers, the IP core enters error mode.

When the IP core function enters error mode (because of an early end of packet for the background layer or a late end of packet for any layer), it has to discard data until the end of packet has been reached for all input layers.

This error recovery process maintains the synchronization between all the inputs and is started once the output frame is completed. A large number of samples may have to be discarded during the operation and backpressure can be applied for a long time on most input layers. Consequently, this error recovery mechanism could trigger an overflow at the input of the system.

Video and Image Processing Suite Overview |

Altera Corporation |

|

|

Send Feedback

1-14 |

Stall Behavior and Error Recovery |

|

UG-VIPSUITE |

|||||

2015.01.23 |

||||||||

|

|

|

|

|

||||

|

|

|

|

|

|

|

||

|

|

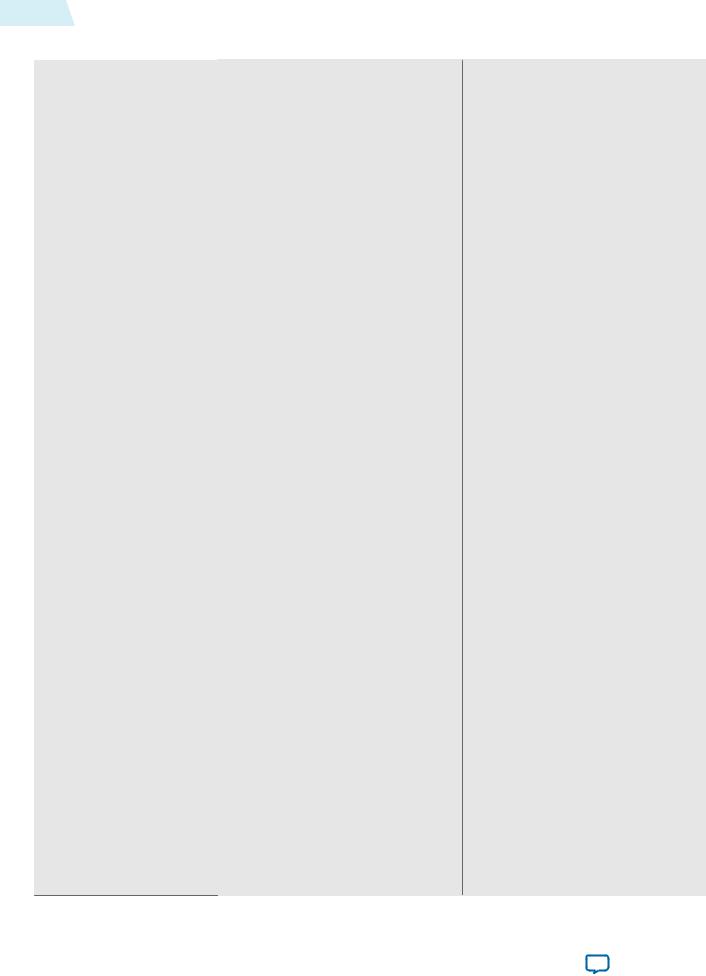

IP Core |

|

Stall Behavior |

|

Error Recovery |

|

|

|

|

|

|

|

|

|

|

|

|

|

Chroma Resampler |

|

All modes stall for a few cycles between |

|

• Receiving an early endofpacket |

||

|

|

|

|

frames and between lines. |

|

signal—the IP core stalls its input |

||

|

|

|

|

Latency from input to output varies |

|

but continues writing data until |

||

|

|

|

|

|

it has sent an entire frame. |

|||

|

|

|

|

depending on the operation mode of |

|

|||

|

|

|

|

|

• Not receiving an endofpacket |

|||

|

|

|

|

the IP core. |

|

|||

|

|

|

|

|

signal at the end of a frame—the |

|||

|

|

|

|

• The only modes with latency of |

|

|||

|

|

|

|

|

IP core discards date until it |

|||

|

|

|

|

more than a few cycles are 4:2:0 to |

|

finds end-of-packet. |

||

|

|

|

|

4:2:2 and 4:2:0 to 4:4:4— |

|

|

|

|

|

|

|

|

corresponding to one line of 4:2:0 |

|

|

|

|

|

|

|

|

data |

|

|

|

|

|

|

|

|

• The quantities of data input and |

|

|

|

|

|

|

|

|

output are not equal because this is a |

|

|

|

|

|

|

|

|

rate-changing function. |

|

|

|

|

|

|

|

|

• Always produces the same number |

|

|

|

|

|

|

|

|

of lines that it accept—but the |

|

|

|

|

|

|

|

|

number of samples in each line |

|

|

|

|

|

|

|

|

varies according to the subsampling |

|

|

|

|

|

|

|

|

pattern used. |

|

|

|

|

|

|

|

|

When not stalled, always processes one |

|

|

|

|

|

|

|

|

sample from the more fully sampled |

|

|

|

|

|

|

|

|

side on each clock cycle. For example, |

|

|

|

|

|

|

|

|

the subsampled side pauses for one |

|

|

|

|

|

|

|

|

third of the clock cycles in the 4:2:2 case |

|

|

|

|

|

|

|

|

or half of the clock cycles in the 4:2:0 |

|

|

|

|

|

|

|

|

case. |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

Clipper/ |

|

• Stalls for a few cycles between lines |

|

• Receiving an early endofpacket |

|

|

|

|

Clipper II |

|

and between frames. |

|

signal—the IP core stalls its input |

|

|

|

|

|

|

• Internal latency is less than 10 |

|

but continues writing data until |

|

|

|

|

|

|

cycles. |

|

it has sent an entire frame. |

|

|

|

|

|

|

• During the processing of a line, it |

|

• Not receiving an endofpacket |

|

|

|

|

|

|

reads continuously but only writes |

|

signal at the end of a frame—the |

|

|

|

|

|

|

when inside the active picture area |

|

IP core discards data until it |

|

|

|

|

|

|

as defined by the clipping window |

|

finds end-of-packet. |

|

|

|

|

|

|

|

|

|

|

|

|

|

Clocked Video Input/ |

|

• Dictated by incoming video. |

|

If an overflow is caused by a |

||

|

|

Clocked Video Input II |

|

• If its output FIFO is empty, during |

|

downstream core failing to receive |

||

|

|

|

|

horizontal and vertical blanking |

|

data at the rate of the incoming |

||

|

|

|

|

periods the IP core does not produce |

|

video, the Clocked Video Input |

||

|

|

|

|

any video data. |

|

sends an early end of packet and |

||

|

|

|

|

|

|

restart sending video data at the |

||

|

|

|

|

|

|

start of the next frame or field. |

||

|

|

|

|

|

|

|

|

|

Altera Corporation |

Video and Image Processing Suite Overview |

|

|

Send Feedback

UG-VIPSUITE |

|

|

|

Stall Behavior and Error Recovery |

1-15 |

|

2015.01.23 |

|

|

|

|||

|

|

|

|

|

||

|

|

|

|

|

|

|

|

IP Core |

|

Stall Behavior |

|

Error Recovery |

|

|

|

|

|

|

|

|

|

Clocked Video Output/ |

|

• Dictated by outgoing video. |

|

• Receiving an early end of packet |

|

|

Clocked Video Output II |

|

• If its input FIFO is empty, during |

|

— the IP core resynchronizes the |

|

|

|

|

horizontal and vertical blanking |

|

outgoing video data to the |

|

|

|

|

periods the IP core stalls and does |

|

incoming video data on the next |

|

|

|

|

not take in any more video data. |

|

start of packet it receives. |

|

|

|

|

|

|

• Receiving a late end of packet— |

|

|

|

|

|

|

the IP core resynchronizes the |

|

|

|

|

|

|

outgoing video data to the |

|

|

|

|

|

|

incoming video immediately. |

|

|

|

|

|

|

• If Genlock functionality is |

|

|

|

|

|

|

enabled—the IP core does not |

|

|

|

|

|

|

resynchronize to the incoming |

|

|

|

|

|

|

video. |

|

|

|

|

|

|

|

|

|

Color Plane Sequencer |

|

• Stalls for approximately 10 cycles |

|

• Processes video packets per line |

|

|

|

|

after processing each line of a video |

|

until the IP core receives an |

|

|

|

|

frame. |

|

endofpacket signal on din0— |

|

|

|

|

• Between frames the IP core stalls for |

|

the line width is taken from the |

|

|

|

|

approximately 30 cycles |

|

control packets on din0. |

|

|

|

|

|

|

• Receiving endofpacket signal on |

|

|

|

|

|

|

either din0 or din1: IP core |

|

|

|

|

|

|

ceases output. |

|

|

|

|

|

|

For the number of cycles left to |

|

|

|

|

|

|

finish the line, the IP core continues |

|

|

|

|

|

|

to drain the inputs that have not |

|

|

|

|

|

|

indicated end of packet. |

|

|

|

|

|

|

• Drains din0 until it receives an |

|

|

|

|

|

|

endofpacket signal on this port |

|

|

|

|

|

|

(unless it has already indicated |

|

|

|

|

|

|

end of packet), and stalls for up |

|

|

|

|

|

|

to one line after this |

|

|

|

|

|

|

endofpacket signal. |

|

|

|

|

|

|

• Signals end of packet on its |

|

|

|

|

|

|

outputs and continue to drain its |

|

|

|

|

|

|

inputs that have not indicated |

|

|

|

|

|

|

end of packet. |

|

|

|

|

|

|

|

|

Video and Image Processing Suite Overview |

Altera Corporation |

|

|

Send Feedback

1-16 |

Stall Behavior and Error Recovery |

|

UG-VIPSUITE |

|||||

2015.01.23 |

||||||||

|

|

|

|

|

||||

|

|

|

|

|

|

|

||

|

|

IP Core |

|

Stall Behavior |

|

Error Recovery |

|

|

|

|

|

|

|

|

|

|

|

|

|

Color Space Converter/ |

|

• Only stalls between frames and not |

|

• Processes video packets until the |

|

|

|

|

Color Space Converter II |

|

between rows. |

|

IP core receives an endofpacket |

|

|

|

|

|

|

• It has no internal buffering apart |

|

signal; the control packets are |

|

|

|

|

|

|

from the registers of its processing |

|

not used. |

|

|

|

|

|

|

pipeline—only a few clock cycles of |

|

• Any mismatch of the |

|

|

|

|

|

|

latency. |

|

endofpacket signal and the |

|

|

|

|

|

|

|

|

frame size is propagated |

|

|

|

|

|

|

|

|

unchanged to the next IP core. |

|

|

|

|

|

|

|

|

|

|

|

|

|

Control Synchronizer |

|

• Stalls for several cycles between |

|

• Processes video packets until the |

||

|

|

|

|

packets. |

|

IP core receives an endofpacket |

||

|

|

|

|

• Stalls when it enters a triggered state |

|

signal; the image width, height |

||

|

|

|

|

while it writes to the Avalon-MM |

|

and interlaced fields of the |

||

|

|

|

|

Slave ports of other IP cores. |

|

control data packets are not |

||

|

|

|

|

• If the slaves do not provide a wait |

|

compared against the following |

||

|

|

|

|

request signal, the stall lasts for no |

|

video data packet. |

||

|

|

|

|

more than 50 clock cycles. |

|

• Any mismatch of the |

||

|

|

|

|

Otherwise the stall is of unknown |

|

endofpacket signal and the |

||

|

|

|

|

length. |

|

frame size of video data packet is |

||

|

|

|

|

|

|

propagated unchanged to the |

||

|

|

|

|

|

|

next IP core. |

||

|

|

|

|

|

|

|

|

|

Altera Corporation |

Video and Image Processing Suite Overview |

|

|

Send Feedback

UG-VIPSUITE |

|

|

|

Stall Behavior and Error Recovery |

1-17 |

|

2015.01.23 |

|

|

|

|||

|

|

|

|

|

||

|

|

|

|

|

|

|

|

IP Core |

|

Stall Behavior |

|

Error Recovery |

|

|

|

|

|

|

|

|

Deinterlacer |

• Bob algorithm |

|

• While the bob algorithm (with |

|

no buffering) is producing an |

|

output frame, it alternates |

|

between simultaneously between |

|

• receiving a row on the input |

|

port and producing a row of |

|

data on the output port |

|

• just producing a row of data |

|

on the output port without |

|

reading any data from the |

|

input port |

The delay from input to output is just a few clock cycles.

•While a field is being discarded, input is read at the maximum rate and no output is generated.

•Weave algorithm

•The IP core may stall for longer than the usual periods between each output row of the image.

•Stalls of up to 45 clock cycles are possible due to the time taken for internal processing in between lines.

•Motion-adaptive algorithm

•The IP core may stall up to 90 clock cycles.

•Receiving endofpacket signal too early or too late is relative to the field dimensions contained in the last control packet processed.

•Receiving endofpacket signal too late: discards extra data in all configurations.

•Receiving an early endofpacket signal when it is configured for no buffering: the IP core interrupts its processing within one or two lines sending undefined pixels, before propagating the endofpacket signal.

•Receiving an early endofpacket signal when it is configured to buffer data in external memory, the input side of the IP core stops processing input pixels. It is then ready to process the next frame after writing undefined pixels for the remainder of the current line into external RAM. The output side of the IP core assumes that incomplete fields have been fully received and pads the incomplete fields to build a frame, using the undefined content of the memory.

Video and Image Processing Suite Overview |

Altera Corporation |

|

|

Send Feedback

1-18 |

Stall Behavior and Error Recovery |

|

UG-VIPSUITE |

|||||

2015.01.23 |

||||||||

|

|

|

|

|

||||

|

|

|

|

|

|

|

||

|

|

IP Core |

|

Stall Behavior |

|

Error Recovery |

|

|

|

|

|

|

|

|

|

|

|

|

|

Deinterlacer II/ |

|

Stores input video fields in the external |

|

• Generates a line with the correct |

||

|

|

Broadcast Deinterlacer |

|

memory and concurrently uses these |

|

length if the IP core receives an |

||

|

|

|

|

input video fields to construct deinter |

|

early endofpacket signal. |

||

|

|

|

|

laced frames. |

|

• The video data in the output |

||

|

|

|

|

|

|

|||

|

|

|

|

• Stalls up to 50 clock cycles for the |

|

frame is valid up to the point |

||

|

|

|

|

first output frame. |

|

where the IP core receives the |

||

|

|

|

|

• Additional delay of one line for |

|

endofpacket signal. |

||

|

|

|

|

second output frame because the IP |

|

• The IP core then stops |

||

|

|

|

|

core generates the last line of the |

|

generating output until it |

||

|

|

|

|

output frame before accepting the |

|

receives the next startofpacket |

||

|

|

|

|

first line of the next input field. |

|

signal. |

||

|

|

|

|

• Delay of two lines for the following |

|

• Receiving a late endofpacket |

||

|

|

|

|

output frames, which includes the |

|

signal, the IP core completes |

||

|

|

|

|

one line delay from the second |

|

generating the current output |

||

|

|

|

|

output frame. |

|

frame with the correct number of |

||

|

|

|

|

• For all subsequent fields, the delay |

|

lines as indicated by the last |

||

|

|

|

|

alternates between one and two |

|

control packet. |

||

|

|

|

|

lines. |

|

• The IP core discards the |

||

|

|

|

|

|

|

subsequent input lines. Once it |

||

|

|

|

|

|

|

receives a startofpacket signal, |

||

|

|

|

|

|

|

the IP core performs a soft reset |

||

|

|

|

|

|

|

and it loses the stored cadence or |

||

|

|

|

|

|

|

motion values. |

||

|

|

|

|

|

|

• The IP core resumes deinter |

||

|

|

|

|

|

|

lacing when it receives the next |

||

|

|

|

|

|

|

startofpacket signal. |

||

|

|

|

|

|

|

|

||

|

|

Frame Reader |

|

Stalls the output for several tens of |

|

The IP core can be stalled due to |

|

|

|

|

|

|

cycles before producing each video data |

|

backpressure, without consequences |

|

|

|

|

|

|

packet, and stalls the output where |

|

and it does not require error |

|

|

|

|

|

|

there is contention for access to |

|

recovery. |

|

|

|

|

|

|

external memory. |

|

|

|

|

|

|

|

|

|

|

|

|

|

Altera Corporation |

Video and Image Processing Suite Overview |

|

|

Send Feedback

UG-VIPSUITE |

|

|

|

Stall Behavior and Error Recovery |

1-19 |

|

2015.01.23 |

|

|

|

|||

|

|

|

|

|

||

|

|

|

|

|

|

|

|

IP Core |

|

Stall Behavior |

|

Error Recovery |

|

|

|

|

|

|

|

|

|

Frame Buffer/ |

|

• May stall frequently and read or |

|

• Does not rely on the content of |

|

|

Frame Buffer II |

|

write less than once per clock cycle |

|

the control packets to determine |

|

|

|

|

during control packet processing. |

|

the size of the image data |

|

|

|

|

• During data processing at the input |

|

packets. |

|

|

|

|

or at the output, the stall behavior of |

|

• Any early or late endofpacket |

|

|

|

|

the IP core is largely decided by |

|

signal and any mismatch |

|

|

|

|

contention on the memory bus. |

|

between the size of the image |

|

|

|

|

|

|

data packet and the content of |

|

|

|

|

|

|

the control packet is propagated |

|

|

|

|

|

|

unchanged to the next IP core. |

|

|

|

|

|

|

• Does not write outside the |

|

|

|

|

|

|

memory allocated for each non- |

|

|

|

|

|

|

image and image Avalon-ST |

|

|

|

|

|

|

video packet; packets are |

|

|

|

|

|

|

truncated if they are larger than |

|

|

|

|

|

|

the maximum size defined at |

|

|

|

|

|

|

compile time. |

|

|

|

|

|

|

|

|

|

Gamma Corrector |

|

• Stalls only between frames and not |

|

• Processes video packets until the |

|

|

|

|

between rows. |

|

IP core receives an endofpacket |

|

|

|

|

• Has no internal buffering aside from |

|

signal; non-image packets are |

|

|

|

|

the registers of its processing |

|

propagated but the content of |

|

|

|

|

pipeline— only a few clock cycles of |

|

control packets is ignored. |

|

|

|

|

latency |

|

• Any mismatch of the |

|

|

|

|

|

|

endofpacket signal and the |

|

|

|

|

|

|

frame size is propagated |

|

|

|

|

|

|

unchanged to the next IP core. |

|

|

|

|

|

|

|

|

|

Interlacer |

|

• Alternates between propagating and |

|

• Receiving endofpacket signal |

|

|

|

|

discarding a row from the input port |

|

later than expected: discards |

|

|

|

|

while producing an interlaced |

|

extra data. |

|

|

|

|

output field—the output port is |

|

• Receiving an early endofpacket |

|

|

|

|

inactive every other row. |

|

signal: the current output field is |

|

|

|

|

• The delay from input to output is a |

|

interrupted as soon as possible |

|

|

|

|

few clock cycles when pixels are |

|

and may be padded with a single |

|

|

|

|

propagated. |

|

undefined pixel. |

|

|

|

|

|

|

|

|

Video and Image Processing Suite Overview |

Altera Corporation |

|

|

Send Feedback

1-20 |

Stall Behavior and Error Recovery |

|

|

UG-VIPSUITE |

||||

|

2015.01.23 |

|||||||

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

IP Core |

|

|

Stall Behavior |

|

Error Recovery |

|

|

|

|

|

|

|

|

|

|

Scaler II |

• The ratio of reads to writes is |

|

proportional to the scaling ratio and |

|

occurs on both a per-pixel and a |

|

per-line basis. |

|

• The frequency of lines where reads |

|

and writes occur is proportional to |

|

the vertical scaling ratio. |

|

• For example scaling up vertically by |

|

a factor of 2 results in the input |

|

being stalled every other line for the |

|

length of time it takes to write one |

|

line of output; scaling down |

|

vertically by a factor of 2 results in |

|

the output being stalled every other |

|

line for the length of time it takes to |

|

read one line of input. |

|

• In a line that has both input and |

|

output active, the ratio of reads and |

|

writes is proportional to the |

|

horizontal scaling ratio. For |

|

example, scaling from 64×64 to |

|

128×128 causes 128 lines of output, |

|

where only 64 of these lines have |

|

any reads in them. For each of these |

|

64 lines, there are two writes to |

|

every read. |

|

The internal latency of the IP core |

|

depends on the scaling algorithm and |

|

whether any run time control is |

|

enabled. The scaling algorithm impacts |

|

stalling as follows: |

|

• Bilinear mode: a complete line of |

|

input is read into a buffer before any |

|

output is produced. At the end of a |

|

frame there are no reads as this |

|

buffer is drained. The exact number |

|

of possible writes during this time |

|

depends on the scaling ratio. |

|

• Polyphase mode with Nv vertical |

|

taps: Nv – 1 lines of input are read |

|

into line buffers before any output is |

|

ready. The scaling ratio depends on |

|

the time at the end of a frame where |

|

no reads are required as the buffers |

|

are drained. |

|

|

•Receiving an early endofpacket signal at the end of an input line: the IP core stalls its input but continues writing data until it has sent on further output line.

•Receiving an early endofpacket signal part way through an input line: the IP core stalls its input for as long as it would take for the open input line to complete; completing any output line that may accompany that input line. Then continues to stall the input, and writes one further output line.

•Does not receive endofpacket signal at the end of a frame: discards extra data end of packet is found.

Altera Corporation |

Video and Image Processing Suite Overview |

|

|

Send Feedback

UG-VIPSUITE |

|

|

|

Stall Behavior and Error Recovery |

1-21 |

|

2015.01.23 |

|

|

|

|||

|

|

|

|

|

||

|

|

|

|

|

|

|

|

IP Core |

|

Stall Behavior |

|

Error Recovery |

|

|

|

|

|

|

|

|

|

Scaler II |

|

Enabling run-time control of |

|

|

|

|

|

|

resolutions affects stalling between |

|

|

|

|

|

|

frames: |

|

|

|

|

|

|

• With no run-time control: about 10 |

|

|

|

|

|

|

cycles of delay before the stall |

|

|

|

|

|

|

behavior begins, and about 20 cycles |

|

|

|

|

|

|

of further stalling between each |

|

|

|

|

|

|

output line. |

|

|

|

|

|

|

• With run-time control of |

|

|

|

|

|

|

resolutions: about additional 25 |

|

|

|

|

|

|

cycles of delay between frames. |

|

|

|

|

|

|

|

|

|

|

|

Switch/ |

|

• Only stalls its inputs when |

|

|

|

|

Switch II |

|

performing an output switch. |

|

|

|

|

|

|

• Before switching its outputs, the IP |

|

— |

|

|

|

|

core synchronizes all its inputs and |

|

|

|

|

|

|

|

|

|

|

|

|

|

the inputs may be stalled during this |

|

|

|

|

|

|

synchronization. |

|

|

|

|

|

|

|

|

|

|

|

Test Pattern Generator/ |

|

• All modes stall for a few cycles after |

|

|

|

|

Test Pattern Generator II |

|

a field control packet, and between |

|

|

|

|

|

|

lines. |

|

|

|

|

|

|

• When producing a line of image |

|

|

|

|

|

|

data, the IP core produces one |

|

— |

|

|

|

|

sample output on every clock cycle, |

|

|

|

|

|

|

|

|

|

|

|

|

|

but it can be stalled without |

|

|

|

|

|

|

consequences if other functions |

|

|

|

|

|

|

down the data path are not ready |

|

|

|

|

|

|

and exert backpressure. |

|

|

|

|

|

|

|

|

|

|

Video and Image Processing Suite Overview |

Altera Corporation |

|

|

Send Feedback