Troubleshooting JUNOS Platforms

|

|

|

Reproduction |

|

|

|

|

|

|

|

|

RTOS Pack Flow |

|

|

The slide highlights the topics we cover in this appendix. We discuss the highlighted |

|

|

topic first. |

Not |

for |

|

|

|

|

|

|

|

Packet Flow Details • B–3

Troubleshooting JUNOS Platforms

|

|

|

|

Reproduction |

|

|

|

|

|

|

|

|

|

|

Packet Processing |

|

|

|

The J Series Routing Engine (RE) and software Packet Forwarding Engine (PFE) are |

|

|

|

both implemented the primary x86 architecture microprocessor. An RTOS kernel |

|

|

|

mediates access to the underlying hardware. The real-time kernel ensures that |

|

|

for |

|

|

|

ope ating system services go out in a constant, load-independent, amount of time. |

|

|

|

This p ocess ensu es that the forwarding and services real-time threads deliver |

|

|

|

predictable packet forwarding performance. |

|

|

|

While the s ftwa e handles packet forwarding decisions with the virtual PFE, the Intel |

|

|

|

IXP netw |

rk processors still provide performance scalability. These network |

|

|

|

pr cess |

rs handle Layer 2 functions such as cyclic redundancy check (CRC) |

|

Not |

validation, statistics gathering, classification, and keepalives. |

|

An IXP network processor is included on each Physical Interface Module (PIM). As a |

|

|

|

result, overall router capability increases as you add PIMs.

B–4 • Packet Flow Details

Troubleshooting JUNOS Platforms

|

|

|

Reproduction |

|

|

|

|

|

|

|

|

ABC Chips Pack t Flow |

|

|

The slide highlights the topic we discuss next. |

Not |

for |

|

|

|

|

|

|

|

Packet Flow Details • B–5

Troubleshooting JUNOS Platforms

forSystem Boa d. TheReproductionM7i and M10i routers combine Flexible PIC Concentrators (FPCs) and System Boa d functionality into the Compact Forwarding Engine Board (CFEB).

ABC ASICs

The slide displays the applicat |

-sp cific integrated circuits (ASICs) that make up an |

ABC chipset router’s PFE. We d |

tail the function of each ASIC on subsequent slides. In |

ABC chipset platforms the ASICs that comprise the PFE are in the PICs, FPCs, and the |

The CFEB makes use of a combined I/O manager ASIC, Distributed Buffer Manager

ASIC, and Inte net Processor II ASIC to educe cost and power consumption while also

impr ving reliability. This ASIC set is sometimes referred to as the ABC ASIC in keeping with the internal ASIC designation of A, B, and C for the Distributed Buffer Manager, I/

O Manager, and Internet Processor II ASICS, respectively. Not

B–6 • Packet Flow Details

Troubleshooting JUNOS Platforms

|

Reproduction |

|

|

|

|

ABC Chips |

Pack t Flow: Part 1 |

When a pack |

arriv s on an input interface of the router, the PIC controller ASIC |

performs all the m |

dia-sp cific operations such as Physical Layer framing and Data |

Link Layer FCS (C |

C) verification. The PIC then passes a serial stream of bits to the |

I/O Manager ASIC on the FPC. |

for |

|

|

|

|

|

Packet Flow Details • B–7

Troubleshooting JUNOS Platforms

|

|

|

|

packet.Reproduction |

|

|

|

|

|

|

|

|

|

|

ABC Chipset Pack t Flow: Part 2 |

|

|

|

The I/O Manager ASIC pars s the bit stream to locate the Layer 2 and Layer 3 |

|

|

|

encapsulation and chops the pack into 64-byte chunks named J-cells. These J-cells |

|

|

|

then travel to the inbound Distributed Buffer Manager ASIC. |

|

|

for |

|

|

|

The I/O Manager ASIC also performs the following: |

|

|

|

• |

Removes Layer 2 encapsulation to locate the beginning of the Layer 3 |

|

|

|

• |

Identifies incoming logical interface. |

|

Not |

• |

Performs basic packet integrity checks. |

|

• |

Counts packets and bytes for each logical circuit. |

|

|

|

|

|

|

• |

Performs behavior aggregate (BA)-based traffic classification to |

|

|

|

|

associate traffic with a forwarding class for egress queuing and |

|

|

|

|

scheduling operations. Examples of BA classification include IP |

|

|

|

|

precedence, DiffServ code points, and MPLS EXP bit settings. |

B–8 • Packet Flow Details

Troubleshooting JUNOS Platforms

Reproduction |

|

|

|

ABC Chips |

Pack t Flow: Part 3 |

The Distribut |

Buff Manager 1 ASIC receives J-cells from each FPC’s I/O Manager |

ASIC and writ s th m into the shared memory bank. The shared memory bank is |

made up of memory contributed by each FPC installed in the router. |

for |

|

|

|

The Buffer Manager 1 ASIC also extracts the key information, which is normally the fi st 64-bytes of a Layer 3 packet, and passes this information to the Internet

P cessor II ASIC in the form of a notification cell. The Internet Processor II performs a l ngest-match route lookup against the forwarding table to identify the packet’s

utg ing interface and forwarding next hop.

Packet Flow Details • B–9

Troubleshooting JUNOS Platforms

|

Reproduction |

|

|

|

|

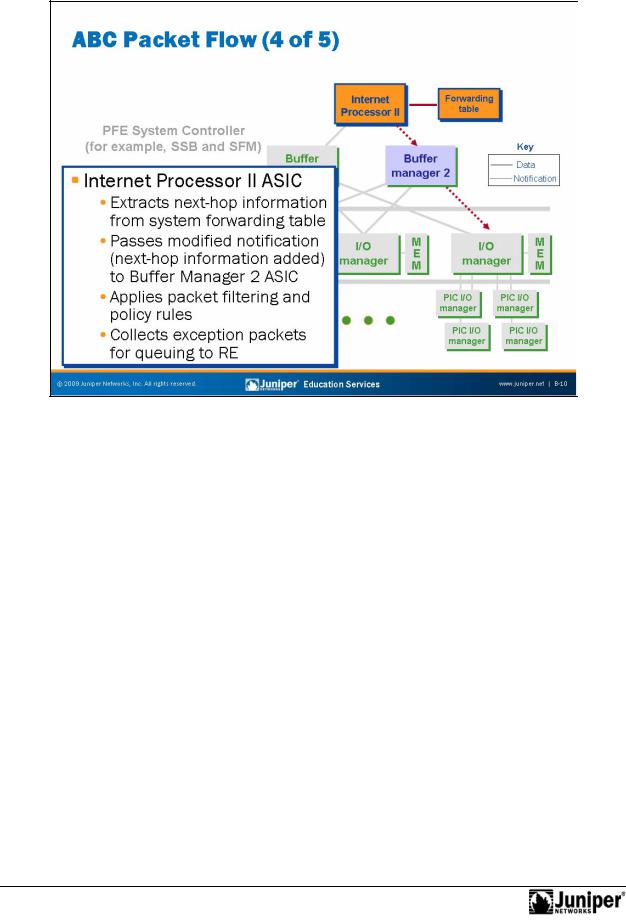

ABC Chipset Pack t Flow: Part 4 |

The Internet Processor II ASIC |

rmines the ultimate destination for every packet |

arriving on a transit int rface. The Internet Processor ASIC consults a copy of the |

forwarding table, which contains destination prefixes and their corresponding next |

hops. The E constructs the forwarding table and the JUNOS Software kernel |

for |

|

|

|

|

maintains it. |

|

|

|

|

After the Inte net Processor II ASIC determines the packet’s egress interface and rwa ding next hop, it amends the notification cell with this information and passes

the n tificati n cell to the second Distributed Buffer Manager ASIC. The second Distributed Buffer Management ASIC then passes the notification cell to the I/O Manager ASIC on the egress FPC (as identified by the modified contents of the notification cell). The Distributed Buffer Manager 2 ASIC acts as an agent for the FPC’s I/O Manager ASIC. Once the I/O Manager ASIC receives a notification cell indicating hat a packet is waiting for servicing, it issues read requests to the Buffer Manager 2 ASIC for the J-cells associated with the packet. As the I/O Manager receives the J-cells, it transmits them to the PIC Controller ASIC, which in turn transmits them out the appropriate port.

In the case of a multicast packet, multiple outgoing interfaces might exist, in which case the notification cell is directed to multiple FPCs or to the same FPC multiple times—once for each outgoing interface served by that FPC.

B–10 • Packet Flow Details

Troubleshooting JUNOS Platforms

ABC ChipsReproductiont Pack Flow: Part 5

When the gr ss FPC is ady to service the packet, the I/O Manager ASIC issues read

requests for the 64-byte J-c lls that comprise the packet. In response, the Distributed Buffer Manager 2 ASIC retrieves the J-cells from shared memory and feeds them to

the I/O Manager ASIC. The I/O Manager ASIC reassembles the packet, decrements forthe packet’s TTL, adds the Layer 2 framing, and then sends the bit stream to the

eg ess PIC.

The I/O Manager ASIC is responsible for class-of-service (CoS)-related queuing, scheduling, and congestion avoidance operations at packet egress. Note that the packet itself never queues on the FPC; rather, a pointer to the packet, in the form of a notification cell, queues on the egress FPC. Each output port on a given PIC associates with four forwarding classes (or queues). You configure schedulers to provide each forwarding class with some share of the port’s bandwidth.

Note that traffic classification, which associates traffic with one of the defined forwarding classes, occurs at the ingress FPC. Once identified at ingress, the traffic is handled in accordance with the parameters configured for that traffic class by the I/O Manager on the egress FPC. The I/O Manager implements the random early detection (RED) algorithm during egress processing to avoid tail drops and the resulting risk of global synchronization of TCP retransmissions. A full coverage of JUNOS Software CoS capabilities is beyond the scope of this class.

Packet Flow Details • B–11

Troubleshooting JUNOS Platforms

|

|

|

Reproduction |

|

|

|

|

|

|

|

|

LMNR Chipset Pack Flow |

|

|

The slide highlights the topic we discuss next. |

Not |

for |

|

|

|

|

|

|

|

B–12 • Packet Flow Details