Scan Engineering Telecom

!"(0732) 51-21-99, 72-71-01

E-mail: capt@set.vrn.ru, http://www.setltd.com

Xilinx |

Xilinx |

144 |

PROM |

PROM |

|

XC18V04 |

XC18V04 |

|

Power |

|

|

SuperVisor |

|

|

Поставляемый модуль конфигурируется в соответствии с опциями поставки:

Плата Set-Mini-V

%Xilinx ISP PROM конфигурации ПЛИС объёмом 4МБит при установке XCV400 и XCV600 либо две ISP PROM по 4МБит при установке XCV800

%встроенные цифровые преобразователи +2.5В и +3.3В до 2А

%встроенный супервизор напряжений +2.5В и +3.3В

%разъём JTAG отладки ПЛИС и загрузки PROM Xilinx

Опции поставки:

-600V5 |

объём и быстродействие ПЛИС Virtex в FG676 (XCV400/600/800) |

Программное обеспечение

%VHDL-проект тестирования под ISE

%ядро 8-ми разрядного RISC микроконтроллера PIC15C5x (опционально)

41

Scan Engineering Telecom

!"(0732) 51-21-99, 72-71-01

E-mail: capt@set.vrn.ru, http://www.setltd.com

Инструментальный модуль

SETCORE-1M

Модуль SETCORE-1M предназначен для построения на своей основе широкого спектра цифровых устройств, начиная от многоканального сбора и обработки цифровой информации до многофункциональных специализированных контроллеров.

Характеристики серии ПЛИС Xilinx Virtex и окрытая архитектура модуля позволяют эффективно реализовывать на базе SETCORE-1M спектр ядер цифровой обработки сигналов (цифровые фильтры, корреляторы, БПФ), телекоммуникаций (модуляторы, кодеки и т.д.) и заказные пользовательские узлы, например, многоканальные ШИМ-контроллеры.

Возможные области применения:

#цифровая обработка сигналов

#системы сбора и обработки цифровых данных

#специализированные контроллеры

Особенности:

$ широкий ряд устанавливаемых ПЛИС Xilinx XCV50 - XCV800

$системная тактовая частота ПЛИС Virtex - до 180МГц

$пиковая производительность модуля (XCV800-6):

-до 21 млрд. МАС на 8-разрядных операндах

-до 5 млрд. МАС на 16-разрядных операндах

$три банка 12нс SRAM 64Кх32

$FLASH-память до 8МБит

$до 110 линий цифрового ввода-вывода

$встроенный программатор ПЛИС из FLASH-памяти модуля

$порт UART RS-232 (контроллер реализуется на ПЛИС как ядро)

$порт JTAG IEEE 1149.1

$возможность использования в качестве субмодуля XDSP-1MP и XDSP-680

42 Web address: http://setltd.com/products/instrumental/standalone/setcore1m

Scan Engineering Telecom

!"(0732) 51-21-99, 72-71-01

E-mail: capt@set.vrn.ru, http://www.setltd.com

Digital Connector

SRAM 2x64Kx16

SRAM |

|

SRAM |

2x64Kx16 |

|

2x64Kx16 |

|

|

|

Xilinx

FPGA

|

|

|

|

|

|

FLASH |

|

UART |

|

Xilinx |

|

||

|

RS-232 |

|

|

Configuration 8Mbit |

||

|

Connector |

|

CPLD |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

||

|

UART |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Digital Connector

Поставляемый модуль конфигурируется в соответствии с опциями поставки:

Плата SETCORE-1M

%CPLD XC95144XL контроллера конфигурации ПЛИС

%FLASH память конфигурации ПЛИС объёмом 8МБит

%микросхема преобразователя уровней RS-232

%кварцевый генератор 50/66/80МГц 100ppm

%линейные стабилизаторы +2.5В и +3.3В (при XCV600, XCV800 не устанавливаются)

%разъём порта RS-232 (тип DB-9)

%штыревые 64-х контактные разъёмы с шагом 2,54 мм штырями вверх

%разъёмы JTAG отладки ПЛИС и загрузки FLASH

%разъём внешнего питания

-50V4 |

Опции поставки: |

объём и градация быстродействия ПЛИС Virtex (50 - 800 тыс. вент.) |

|

-3S |

число установленных банков SRAM 64Kx32 12нс (1 - 3) |

Программное обеспечение

%проект для САПР Foundation (schematic)

%ядро контроллера UART (опционально)

43

Scan Engineering Telecom

!"(0732) 51-21-99, 72-71-01

E-mail: capt@set.vrn.ru, http://www.setltd.com

Модуль цифровой обработки сигналов XDSP-16CP

Модуль XDSP-16CP предназначен для построения многоканальных систем цифрового радиоприёма и локации в промышленном исполнении. Гибкая конфигурация модуля, высокая производительность ПЛИС Xilinx семейства Virtex позволяет эффективно реализовать практически весь спектр алгоритмов обработки цифровых сигналов, начиная от высокоскоростного аналого-цифрового

преобразования и цифровой фильтрации до многоканального спектрального анализа и двумерной обработки изображений.

Модуль имеет высокоскоростные каналы приема и передачи данных в стандарте LVDS. Пиковая пропускная способность 1.82 Гбит/сек по каждому каналу. Протяженность канала связи до 4 м. Модуль XDSP-16CP может работать в составе единой системы обработки сигналов с модулями SETLINK-22TR, SETLINK-22RL.

Возможные области применения:

#многоканальный цифровой радиоприём

#широкополосные системы связи

#сверхвысокопроизводительная цифровая обработка сигналов

#радиолокация, фазированные антенные решётки

#системы цифрового наблюдения и анализа радиосигналов

Особенности:

$ до 2.4 млн. вентилей в пяти ПЛИС Xilinx серии Virtex $ системная тактовая частота ПЛИС Virtex - до 180 МГц

$пиковая производительность модуля (три XCV800-8):

до 160 млрд. МАС на 8-разрядных операндах до 30 млрд. МАС на 16-разрядных операндах до 3.5 млрд. МАС на 32-разрядных операндах

$16 независимых каналов АЦП 8 бит 100 МГц

$ канал передачи данных в стандарте LVDS – 28 бит 66 МГц $ канал приема данных в стандарте LVDS – 28 бит 66 МГц

$частота межкристального обмена ПЛИС - до 180 МГц

$ два банка синхронной двухпортовой памяти SRAM 32Kx32

$FLASH до 32 Мбит

$варианты модуля в коммерческом (0 +70°С) и индустриальном исполнении

(-40 +85°С)

44 Web address: http://setltd.com/products/instrumental/standalone/xdsp16cp

Scan Engineering Telecom

!"(0732) 51-21-99, 72-71-01

E-mail: capt@set.vrn.ru, http://www.setltd.com

ADC 100 MSPS 12 bit

ADC 100 MSPS 12 bit

16 Channel

ADC 100 MSPS 12 bit

LVDS SERDES

Receiver 28 bit + Clock

Comparator

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Xilinx |

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

Xilinx |

|

|

|

|

|

Xilinx |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LVDS SERDES |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Transmitter |

|||||||||||||||

|

|

|

|

|

|

|

|

|

FPGA |

|

|

|

|

|

||||||||||||||||||||

|

|

|

CPLD |

|

|

|

|

|

FPGA |

|

|

|

|

|

|

|

|

28 bit + Clock |

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

Xilinx |

|

|

|

|

|

Dual Port |

|

|

Xilinx |

|

|

|

|

Dual Port |

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

RAM |

|

|

|

|

|

|

|

|

RAM |

|

|

|

||||||||||||||

|

|

|

CPLD |

|

|

|

|

|

IDT |

|

|

FPGA |

|

|

|

|

IDT |

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Xilinx |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

FLASH |

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CPLD |

|

|

|

|

|

|

up to 32Mbit |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

Clock |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

Поставляемые конфигурации:

Поставляется одна базовая конфигурация модуля, конфигурируемая по желанию Заказчика по типу ПЛИС и количеству каналов АЦП:

%три ПЛИС типа FPGA XCV300-4PQ240C

%три ПЛИС типа CPLD XC95288XL

%16 независимых каналов АЦП AD9288 – 8 бит 100 МГц

%компаратор сигнала синхронизации

%ECL вход сигнала синхронизации

%2 банка синхронной двухпортовой памяти SRAM 32Kx32

%FLASH 32МБит

%LVDS передатчик - 28 бит x 66 МГц

%LVDS приемник - 28 бит x 66 МГц

%соединительные кабели

Программное обеспечение комплекта поставки:

%проект тестирования для САПР Foundation (schematic)

45

Scan Engineering Telecom

!"(0732) 51-21-99, 72-71-01

E-mail: capt@set.vrn.ru, http://www.setltd.com

Программное обеспечение проектирования ПЛИС модулей

В комплект поставки модулей входит тестовый проект-иллюстрация для ПЛИС под САПР Xilinx ISE (VHDL), позволяющий разработчику в кратчайшие сроки освоить проектирование своих изделий на базе модулей.

Все составные части проекта описаны в виде отдельных компонентов, например, контроллера памяти, узла работы с АЦП, с ЦПОС и т.д. в соответствующих VHDL-файлах, объединённых на верхнем уровне иерархии.

Верхний уровень иерархии проекта наряду с объединением отдельных компонентов, наглядно иллюстрирует все внешние межсоединения ПЛИС с элементами модуля.

В состав проекта также входят необходимые командные VHDL-файлы (tectbench) для моделирования работы всех составных узлов проекта.

Файлы ограничений User Constraints File проекта закрепляют выводы ПЛИС

инакладывают необходимые временные ограничения.

Винструкциях по эксплуатации каждого модуля приводится описание всех компонентов проекта, файлов моделирования и UCF, описывается порядок работы с проектом, опции синтеза, трассировки и моделирования, а также порядок загрузки ПЛИС в различных режимах конфигурации.

Пример проекта ПЛИС модуля XDSP-3PC в среде Xilinx ISE

46

Scan Engineering Telecom

!"(0732) 51-21-99, 72-71-01

E-mail: capt@set.vrn.ru, http://www.setltd.com

Программное обеспечение проектирования ЦПОС модулей

Для освоения цифрового сигнального процессора, установленного на ряде модулей, в комплект поставки включается тестовый проект на Си++ для среды TI Code Composer Studio, иллюстрирующий порядок обмена ЦПОС с ПЛИС и тестирование собственной памяти.

В инструкциях по эксплуатации каждого модуля приводится порядок загрузки ЦПОС посредством ПЛИС модуля.

Пример проекта ЦПОС модуля XDSP-3PC в среде TI Code Composer Studio

47

Scan Engineering Telecom

!"(0732) 51-21-99, 72-71-01

E-mail: capt@set.vrn.ru, http://www.setltd.com

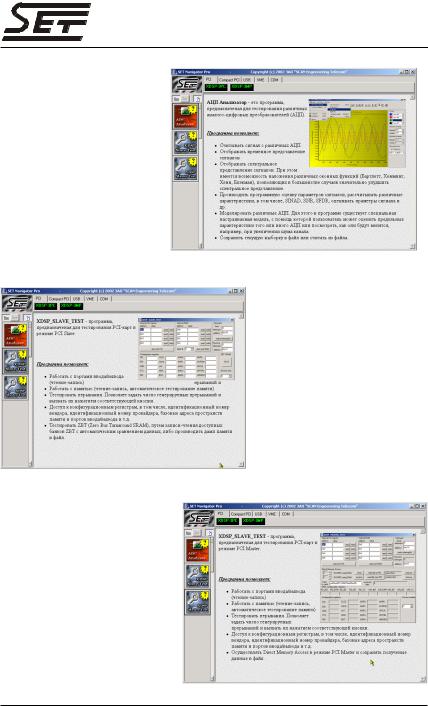

Программное обеспечение тестирования модулей

В комплекте с модулями поставляется ряд программ тестирования ресурсов модулей: работы с шинными контроллерами модулей, АЦП/ЦАП, ОЗУ.

Все программы тестирования объединены интегрированной информацион-

ной среде SETNavigatorPRO.

Пример окна

SetNavigatorPro для модуля XDSP-3PC

48

Scan Engineering Telecom

!"(0732) 51-21-99, 72-71-01

E-mail: capt@set.vrn.ru, http://www.setltd.com

Программа работы с АЦП/ЦАП

SETADC_Analyzer

Программа работы с

PCI Slave,

ОЗУ, регистрами, прерыванием

XDSP_Slave_Test

Программа работы с

PCI Master, DMA XDSP_Master_Test

49

Scan Engineering Telecom

!"(0732) 51-21-99, 72-71-01

E-mail: capt@set.vrn.ru, http://www.setltd.com

Средства отладки ПЛИС Xilinx

Конфигурацию и отладку ПЛИС модулей можно производить с помощью трёх видов кабелей: в параллельный порт - SET-JTAG-3/5V (аналог Parallel Download Cable III) и Parallel Download Cable IV, в USB и RS-232 - Xilinx MultiLinx Cable.

Все кабели поддерживаются программой iMPACT Xilinx, а также программой внутрисхемного анализа ChipScope ILA Xilinx.

SET-JTAG-3/5V

предназначен для конфигурации ПЛИС

FPGA и CPLD, ISP PROM посредством канала JTAG IEEE1149.1, а также FPGA

в режиме Slave Serial через порт LPT. Совместим с приборами Xilinx с питанием блоков ввода-вывода 3.3В и 5В.

Xilinx Parallel Cable IV

предназначен для конфигурации ПЛИС

FPGA и CPLD, ISP PROM посредством канала JTAG IEEE1149.1, а также FPGA

в режиме Slave Serial через порт LPT. Совместим с приборами Xilinx с питанием блоков ввода-вывода 1.5, 1.8, 2.5, 3.3В и 5В.

Обеспечивает скорость передачи дан-

ных до 4МБит/сек (LPT IEEE1284 ECP).

Xilinx MultiLinx Cable

предназначен для конфигурации ПЛИС

FPGA и CPLD, ISP PROM посредством канала JTAG IEEE1149.1, а также FPGA в режимах Slave Serial и Select MAP

посредством USB и RS-232. Совместим с приборами Xilinx с питанием блоков ввода-вывода 2.5, 3.3В и

5В.

Обеспечивает скорость передачи данных до 12МБит/сек (USB).

50