- •Особенности

- •Обзор семейства

- •Функциональный блок

- •Макроячейка

- •Распределитель термов

- •Блок ввода-вывода

- •Банки ввода-вывода

- •Возможность закрепления контактов

- •Программирование в системе

- •Защита проекта от копирования

- •Режим пониженного потребления энергии

- •Модель задержек распространения сигналов

- •Характеристики при включении питания

- •Программное обеспечение проектирования

- •Характеристики семейства XC9500XV по постоянному току

- •Микросхема XC9536XV

- •Описание

- •Потребление тока

- •Динамические параметры микросхем XC9536XV

- •Параметры временной модели

- •Корпуса

- •Обозначение микросхем XC9536XV

- •Микросхема XC9572XV

- •Описание

- •Потребление тока

- •Динамические параметры микросхем XC9572XV

- •Параметры временной модели

- •Корпуса

- •Обозначение микросхем XC9572XV

- •Микросхема XC95144XV

- •Описание

- •Потребление тока

- •Динамические параметры микросхем XC95144XV

- •Параметры временной модели

- •Корпуса

- •Обозначение микросхем XC95144XV

- •Микросхема XC95288XV

- •Описание

- •Потребление тока

- •Динамические параметры микросхем XC95288XV

- •Параметры временной модели

- •Корпуса

- •Обозначение микросхем XC95288XV

- •СОДЕРЖАНИЕ

R

Микросхема XC95144XV

Описание

МС XC95144XV – высокопроизводительная CPLD семейства XC9500XV. Состоит из 8-ми 54V18 функциональных блоков (144 МЯ), ёмкостью 3 200 логических вентилей и минимальной задержкой распространения сигнала контакт-контакт 4 нс.

Потребление тока

Потребление тока микросхемой может быть значительно снижено переводом некоторых или всех МЯ из высокоскоростного режима в режим низкого потребления. Не использованные макроячейки отключаются для снижения потребления тока.

Потребление тока конкретным проектом может быть подсчитано при помощи формулы:

ICC(мА)= MCHP (0.5) + MCLP (0.3) + MC (0.0045) f

Где

MCHP – Количество макроячеек в высокопроизводительном режиме

MCLP - Количество макроячеек в режиме малого потребления

Семейство XC9500XV

MC – Общее количество задействованных макроячеек

f – частота (МГц)

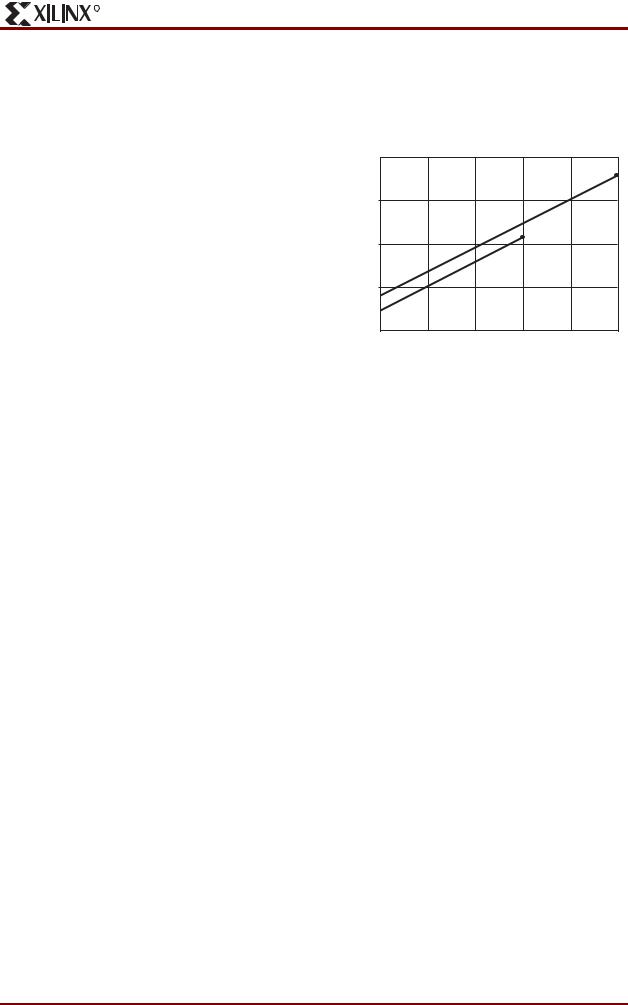

На Рис. 22 показано типичное потребление для XC95144XV в обоих режимах.

(ìÀ)

CC I

200

150

100

50

режим Высокоскоростной потребления малого Режим

200 ÌÃö

120 ÌÃö

0 |

40 |

80 |

120 |

160 |

200 |

Частота (МГц)

Рис. 22. Типичное потребление тока микросхе-

мой XC95144XV

Динамические параметры микросхем XC95144XV

В Табл. 17 приведены динамические параметры микросхем XC95144XV в зависимости от дифференциации кристаллов по быстродействию. Временные параметры даны в нс., а частоты в МГц.

Табл. 17. Динамические параметры микросхем XC95144XV

|

|

XC95144XV- |

XC95144XV- |

XC95144XV- |

||||

Обозначение |

Параметр |

4 |

5 |

7 |

||||

Мин. |

Макс. |

Мин. |

Макс. |

Мин. |

Макс. |

|||

|

|

|||||||

|

|

|

|

|

|

|

|

|

tPD |

Задержка вход МС – комбинаторная логика – вы- |

|

4.0 |

|

5.0 |

|

7.5 |

|

ход МС |

|

|

|

|||||

tSU |

Время установки глобального тактового сигнала |

3.1 |

|

3.7 |

|

4.8 |

|

|

tH |

Время удержания данных после глобального так- |

0.0 |

|

0.0 |

|

0.0 |

|

|

тового сигнала |

|

|

|

|||||

tCO |

Задержка глобального тактового сигнала до вы- |

|

2.0 |

|

2.5 |

|

4.5 |

|

хода |

|

|

|

|||||

tSYSTEM |

Системная частота, задействованы все ФБ |

|

250.0 |

|

222.2 |

|

125.0 |

|

tPSU |

Время установки тактового сигнала PTC |

0.5 |

|

0.7 |

|

1.6 |

|

|

tPH |

Время удержания данных после тактового сигна- |

1.8 |

|

2.0 |

|

3.2 |

|

|

ла PTC |

|

|

|

|||||

|

|

|

|

|

|

|

||

tPCO |

Задержка тактового сигнала PTC до выхода |

|

4.6 |

|

5.5 |

|

7.7 |

|

tOE |

Задержка сигнала разрешения по цепи GTS |

|

2.5 |

|

3.0 |

|

5.0 |

|

tOD |

Задержка сигнала запрещения по цепи GTS |

|

2.5 |

|

3.0 |

|

5.0 |

|

tPOE |

Задержка сигнала разрешения по цепи PTOE |

|

5.5 |

|

7.0 |

|

9.5 |

|

tPOD |

Задержка сигнала запрещения по цепи PTOE |

|

5.5 |

|

7.0 |

|

9.5 |

|

tAO |

Задержка глобального сброса/установки |

|

7.7 |

|

10.0 |

|

12.0 |

|

tPAO |

Задержка сигнала по цепи PTS |

|

8.5 |

|

10.5 |

|

12.6 |

|

tWLH |

Длительность ЕДИНИЦЫ или НУЛЯ глобального |

2.0 |

|

2.2 |

|

4.0 |

|

|

тактового сигнала |

|

|

|

|||||

|

|

|

|

|

|

|

||

tPLH |

Длительность ЕДИНИЦЫ или НУЛЯ тактового |

5.0 |

|

5.0 |

|

6.5 |

|

|

сигнала PTC |

|

|

|

|||||

|

|

|

|

|

|

|

||

15 августа 2001 г. Краткое техническое описание |

21 |

Семейство XC9500XV

Параметры временной модели

R

В Табл. 18 приведены параметры временной модели микросхем XC95144XV в зависимости от дифференциации кристаллов по быстродействию. Параметры даны в нс.

Табл. 18. Параметры временной модели микросхем XC95144XV

|

|

XC95144XV- |

XC95144XV- |

XC95144XV- |

||||

Обозначение |

Параметр |

4 |

|

5 |

7 |

|||

Мин. |

|

Макс. |

Мин. |

Макс. |

Мин. |

Макс. |

||

|

|

|

||||||

|

|

|

|

|

|

|

|

|

tIN |

Задержка на входном буфере |

|

|

1.2 |

|

1.5 |

|

2.3 |

tGCK |

Задержка на глобальном тактовом буфере |

|

|

0.2 |

|

0.3 |

|

1.5 |

tGSR |

Задержка на буфере глобального сброса/установки |

|

|

1.2 |

|

2.0 |

|

3.1 |

tGTS |

Задержка на глобальном буфере управления треть- |

|

|

2.5 |

|

3.0 |

|

5.0 |

им состоянием |

|

|

|

|

||||

tOUT |

Задержка на выходном буфере |

|

|

1.6 |

|

2.0 |

|

2.5 |

tEN |

Задержка разрешения/запрещения выхода выходно- |

|

|

0.0 |

|

0.0 |

|

0.0 |

го буфера |

|

|

|

|

||||

tPTCK |

Задержка PTC |

|

|

1.6 |

|

1.8 |

|

2.4 |

tPTSR |

Задержка PTS |

|

|

0.8 |

|

1.0 |

|

1.4 |

tPTTS |

Задержка PTOE |

|

|

4.3 |

|

5.5 |

|

7.2 |

tPDI |

Задержка на комбинаторной логике |

|

|

0.4 |

|

0.5 |

|

1.3 |

tSUI |

Предустановка данных на входе регистра |

1.3 |

|

|

1.5 |

|

2.6 |

|

tHI |

Удержание данных на входе регистра |

1.0 |

|

|

1.2 |

|

2.2 |

|

tECSU |

Предустановка сигнала CE (разрешение тактирова- |

1.3 |

|

|

1.5 |

|

2.6 |

|

ния) |

|

|

|

|

||||

tECHO |

Удержание сигнала CE |

1.0 |

|

|

1.2 |

|

2.2 |

|

tCOI |

Время срабатывания регистра |

|

|

0.2 |

|

0.2 |

|

0.5 |

tAOI |

Время асинхронного сброса/установки регистра |

|

|

4.9 |

|

6.0 |

|

6.4 |

tRAI |

Задержка срабатывания триггера по тактовому вхо- |

4.0 |

|

|

5.0 |

|

7.5 |

|

ду после асинхронного сброса/установки регистра |

|

|

|

|

||||

tLOGI |

Задержка на внутренней логике МЯ |

|

|

0.8 |

|

1.0 |

|

1.4 |

tLOGILP |

Задержка на внутренней логике МЯ в режиме мало- |

|

|

3.8 |

|

5.0 |

|

6.4 |

го потребления |

|

|

|

|

||||

tF |

Задержка по обратной связи от ПМ |

|

|

1.7 |

|

1.8 |

|

3.5 |

tPTA |

Дополнительная задержка при использовании рас- |

|

|

0.6 |

|

0.7 |

|

0.8 |

пределителя термов |

|

|

|

|

||||

tSLEW |

Дополнительная программируемая задержка БВВ |

|

|

2.5 |

|

3.0 |

|

4.0 |

Корпуса

Микросхема XC95144XV может поставляться в трех корпусах: TQFP-100, TQFP-144 и CSP-144. В корпусах TQFP-100, TQFP-144 и CSP-144 микро-

схема XC95144XV совместима по выводам с XC95144. В Табл. 19 представлены контакты спе-

циального назначения для конкретного корпуса, все не указанные контакты являются пользовательскими и доступны для программирования. Контакты GCK, GTS и GSR могут быть запрограммированы и как обычные, не глобальные.

22 |

15 августа 2001 г. Краткое техническое описание |

R |

Семейство XC9500XV |

|

|

Табл. 19. Контакты специального назначения |

|

Назначение кон- |

TQFP-100 |

TQFP-144 |

CSP-144 |

||

такта |

|

|

|

|

|

GCK1 |

22 |

|

30 |

K2 |

|

GCK2 |

23 |

|

32 |

L1 |

|

GCK3 |

27 |

|

38 |

N2 |

|

GTS1 |

3 |

|

5 |

D4 |

|

GTS2 |

4 |

|

6 |

D3 |

|

GTS3 |

1 |

|

2 |

B1 |

|

GTS4 |

2 |

|

3 |

C2 |

|

GSR |

99 |

|

143 |

A2 |

|

TCK |

48 |

|

67 |

L10 |

|

TDI |

45 |

|

63 |

L9 |

|

TDO |

83 |

|

122 |

C8 |

|

TMS |

47 |

|

65 |

N10 |

|

VCCINT 2.5 В |

5, 57, |

98 |

8, 42, 84, 141 |

B3, D1, J13, L4 |

|

VCCIO1 |

26, 38, 51 |

37, 55, 73 |

L7, N1, N13 |

||

VCCIO2 |

88 |

|

1, 109, 127 |

A1, A13, C7 |

|

GND |

21, 31, 44, 62, 69, |

18, 29, 36, 47, 62, 72, 89, 90, |

B2, B8, B12, C10, E11, G1, G12, |

||

75, 84, |

100 |

99, 108, 114, 123, 144 |

G13, K1, M2, M5, M9, M12 |

||

|

|||||

Не присоединены |

- |

|

- |

- |

|

Обозначение микросхем XC95144XV

На Рис. 23 представлен способ обозначения МС XC95144XV в зависимости от быстродействия, типа корпуса и рекомендуемого температурного диапазона.

XC95144XV -7 TQ100C

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Температурный диапазон |

||

|

Тип микросхемы |

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

Быстродействие |

|

|

|

|

|

|

|

|

|

|

Число контактов |

||||

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Тип корпуса |

Градация по быстродействию |

Корпуса |

|

|

|

||||||||||||

|

|

|

|

|||||||||||||

-7 |

7 нс задержка контакт-контакт |

|

|

|

TQ100 100-Pin Thin Quad Flat Pack (TQFP) |

|||||||||||

-5 |

5 нс задержка контакт-контакт |

|

|

|

TQ144 144-Pin Thin Quad Flat Pack (TQFP) |

|||||||||||

-4 |

4 нс задержка контакт-контакт |

|

|

|

CS144 144-Ball Chip Scale Package (CSP) |

|||||||||||

Температурный диапазон

C - Коммерческий (0°С ... 70°С)

I - Промышленный (-40°С ... +85°С)

Рис. 23. Обозначение микросхем XC95144XV

В Табл. 20 представлены все варианты выпускаемых в настоящее время МС XC95144XV. В скобках даны планируемые к выпуску микросхемы.

Табл. 20. Варианты выпускаемых в настоящее время МС XC95144XV

|

|

TQ100 |

TQ144 |

CS144 |

XC95144XV |

-4 |

(C) |

(C) |

- |

-5 |

(C) |

(C) |

(C) |

|

|

-7 |

C, I |

C, I |

C |

15 августа 2001 г. Краткое техническое описание |

23 |