- •Особенности

- •Обзор семейства

- •Функциональный блок

- •Макроячейка

- •Распределитель термов

- •Блок ввода-вывода

- •Банки ввода-вывода

- •Возможность закрепления контактов

- •Программирование в системе

- •Защита проекта от копирования

- •Режим пониженного потребления энергии

- •Модель задержек распространения сигналов

- •Характеристики при включении питания

- •Программное обеспечение проектирования

- •Характеристики семейства XC9500XV по постоянному току

- •Микросхема XC9536XV

- •Описание

- •Потребление тока

- •Динамические параметры микросхем XC9536XV

- •Параметры временной модели

- •Корпуса

- •Обозначение микросхем XC9536XV

- •Микросхема XC9572XV

- •Описание

- •Потребление тока

- •Динамические параметры микросхем XC9572XV

- •Параметры временной модели

- •Корпуса

- •Обозначение микросхем XC9572XV

- •Микросхема XC95144XV

- •Описание

- •Потребление тока

- •Динамические параметры микросхем XC95144XV

- •Параметры временной модели

- •Корпуса

- •Обозначение микросхем XC95144XV

- •Микросхема XC95288XV

- •Описание

- •Потребление тока

- •Динамические параметры микросхем XC95288XV

- •Параметры временной модели

- •Корпуса

- •Обозначение микросхем XC95288XV

- •СОДЕРЖАНИЕ

R

Семейство XC9500XV

VÂÛÕ

VCCIO |

|

Стандартный |

|

|

|

||

режим |

|

||

|

|

|

Медленный |

|

|

tSLEW |

режим |

1.2 Â

T

0

(a)

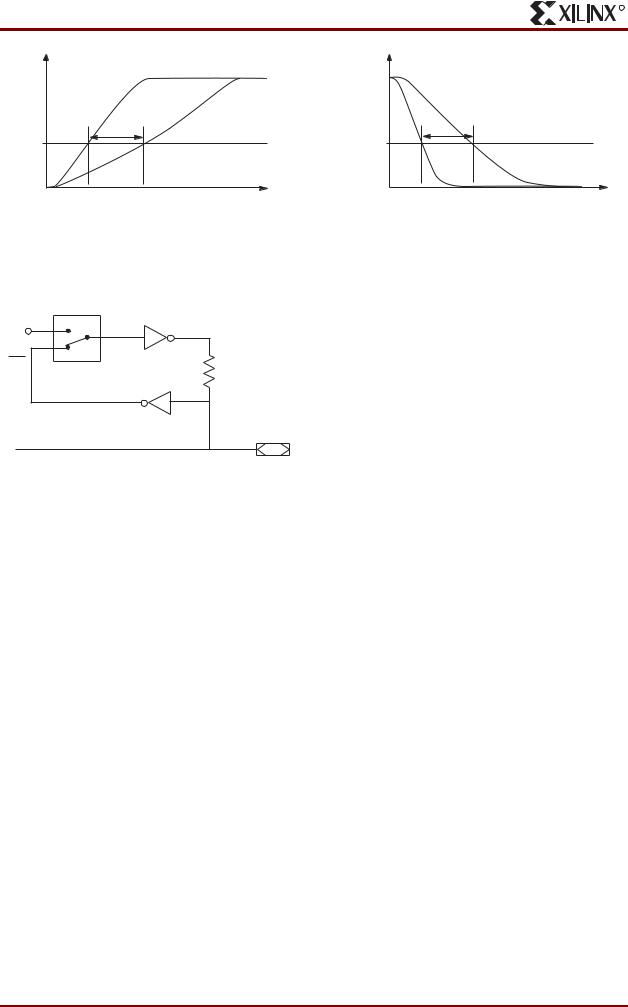

Рис. 12. Выходные характеристики БВВ

В рабочем реæèме подключ¸н к PIN

0

PIN |

RBH |

|

I/O

Рис.13. Схема цепи удержания последнего состояния

Блоки ввода-вывода МС семейства XC9500XV совместимы по входу с 3.3 В логикой, несмотря на то что напряжение питания ядра кристалла составляет 3.3 В. Такое свойство БВВ позволяет подавать 3.3 вольтовые КМОП/ТТЛ сигналы непосредственно на входы МС XC9500XV не опасаясь повреждения БВВ. Входные сигналы и напряжения питания могут подаваться в любой последовательности, что делает возможным использование МС семейства XC9500XV в устройствах с «горячей» заменой.

Банки ввода-вывода

В микросхемах XC95288XV и XC9144XV блоки ввода вывода разбиты на банки (4 и 2 соответственно). Каждый банк имеет раздельное питание выходных каскадов VCCIO что, например, позволяет

выходным сигналам одного банка обеспечивать на выходе 2.5 В совместимость, а другого 3.3 В или 1.8 В. Также возможна подача на все банки одного и того же напряжения VCCIO.

Возможность закрепления контактов

Микросхемы семейства XC9500XV обладают архитектурными особенностями, позволяющими вно-

VÂÛÕ

Медленный

режим

tSLEW

1.2 Â

Стандартный

режим

T

0

(b)

сить изменения в схему, сохраняя при этом назначение выводов. Это дает разработчику уверенность в том, что назначение как входных, так и выходных контактов останется неизменным при любых непредвиденных изменениях схемы, и производить разработку печатной платы. При необходимости внесения изменений в схему, требующих более высокой логической емкости по сравнению с имеющейся в первоначально выбранной МС, есть возможность загрузки схемы в большую, совместимую по контактам МС, без изменения прежних назначений сигналов на выводы.

Программирование в системе

Микросхемы семейства XC9500XV программируются в системе через стандартный четырехконтактный JTAG-интерфейс, как показано на Рис. 14. Программирование в системе позволяет быстро и эффективно вносить изменения в проект, при этом исключается необходимость извлекать микросхему из разрабатываемого устройства. Программное обеспечение фирмы Xilinx создает конфигурационную последовательность, которая может быть загружена в микросхему либо с помощью загрузочного кабеля, либо из системы проектирования, поддерживающей JTAG-протокол, либо с помощью JTAG-cовместимого тестера электронных устройств, либо через простой микропроцессорный интерфейс, эмулирующий последовательность ко-

манд JTAG.

Микросхемы семейства XC9500XV также могут быть запрограммированы специализированным программатором Xilinx (HW130), либо универсальными программаторами других фирм.

Минимальное число циклов программирования - 10000. Время хранения записанной конфигурации не менее 20-ти лет.

10 |

15 августа 2001 г. Краткое техническое описание |

R |

Семейство XC9500XV |

|

VCC

D

N

G

(a)

Рис. 14. Программирование в системе

Протокол периферийного ска-

нирования IEEE Std. 1149.1

МС семейства XC9500XV полностью поддерживают протокол периферийного сканирования IEEE Std. 1149.1 (JTAG). При этом поддерживаются ко-

манды EXTEST, SAMPLE/PRELOAD, BYPASS, USERCODE, INTEST, IDCODE и HIGHZ. Для опе-

раций программирования в системе добавлены ко-

манды: ISPEN, FERASE, FPGM, FVFY и ISPEX, ко-

торые являются полностью совместимыми со стандартом 1149.1 расширениями набора команд.

Контакты TMS и TCK имеют pull-up резисторы в соответствии со стандартом IEEE Std. 1149.1.

Файлы BSDL (Boundary Scan Description Language)

для МС семейства XC9500XV включены в программное обеспечение проектирования и также доступны на FTP-сайте компании Xilinx.

Защита проекта от копирования

В МС семейства XC9500XV используются передовые методы, которые обеспечивают полную защиту схемы от несанкционированного чтения или случайного стирания (перепрограммирования). В Табл. 3 представлены четыре варианта установки кодов защиты.

Защита по чтению (код секретности) устанавливается пользователем для исключения возможности чтения или копирования схемы. Код секретности может быть отменен только в случае полного стирания МС. Код защиты по записи обеспечивает дополнительную защиту от случайного стирания МС или перепрограммирования пользователем. Установленная однажды, защита от записи может быть отменена при возникновении необходимости перепрограммирования микросхемы пользователем.

(b)

Табл. 3. Варианты установки кодов защиты

Защита от чтения Защита от чтения |

|

не установлена |

установлена |

Защита от записи Чтение разрешено Чтение запрещено не установлена Запись разрешена Запись разрешена

Защита от записи Чтение разрешено Чтение запрещено установлена Запись запрещена Запись запрещена

Режим пониженного потребления энергии

Все МС семейства XC9500XV обеспечивают возможность установки режима пониженного потребления энергии не только для всей схемы, но и для выбранных пользователем отдельных макроячеек.

При проектировании устройства необходимо помнить, что режим пониженного потребления приводит к появлению дополнительных задержек в работе макроячеек (tLP). Таким образом, можно устано-

вить режим пониженного потребления для частей схемы, не требующих повышенного быстродействия, а для критичных к задержкам макроячейкам оставить стандартный режим энергопотребления. Это позволит значительно снизить потребление энергии МС в целом.

Модель задержек распространения сигналов

Единообразие архитектуры МС семейства XC9500XV позволяет принять простую модель задержек распространения сигналов для всего кристалла. Базовая модель, показанная на Рис. 15 применима для макроячейки, использующей только прямые термы, находящейся в стандартном режиме энергопотребления и со стандартными установками скорости нарастания фронтов. В Табл. 4 показано как воздействует на временные параметры использование распределителя термов, режима

15 августа 2001 г. Краткое техническое описание |

11 |

Семейство XC9500XV |

R |

|

пониженного энергопотребления, а также измене- |

прямые термы, то коэффициент охвата логики 0. |

||||||||||||||||

ние скорости нарастания фронтов. |

На рисунке 6 коэффициент охвата логики 1, а на |

||||||||||||||||

Задержка на распределителе термов зависит от |

рисунке 7 – 2. |

|

|

|

|

|

|||||||||||

Детальная модель может быть получена из полной |

|||||||||||||||||

коэффициента охвата логики функцией макроячей- |

|||||||||||||||||

ки. Коэффициент охвата логики определяется как |

модели, показанной на Рис. 16. Значения парамет- |

||||||||||||||||

количество дополнительных распределителей |

ров и пояснения даны в описаниях конкретной мик- |

||||||||||||||||

термов минус один. Если используются только пря- |

росхем. |

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

tSU |

|

|

|

|

|

|

|||

|

|

|

|

Комбинаторная |

|

|

|

Комбинаторная |

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

D/T Q |

|

|

|||

|

|

|

|

логика |

|

|

|

|

|

|

логика |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tCO |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Задержка распространения = t |

PD |

Время установки = t SU |

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

(a) |

|

|

Задержка тактового сигнала до выхода = t CO |

||||||||||

(b)

tPSU

Комбинаторная |

D/T |

Q |

|

|

|

логика |

|

|

|

||

|

|

|

|

|

|

Òåðì |

|

|

Комбинаторная |

|

|

|

|

|

D/T |

Q |

|

|

|

tPCO |

логика |

||

|

|

|

|

Время установки = t PSU |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Задержка тактового сигнала до выхода = t PCO |

Период внутреннего системного тактового сигнала = tSYSTEM |

|||||

|

||||||

(c) |

|

|

(d) |

|||

Рис. 15. Базовая временная модель |

|

|

|

||

|

Обратная связь |

|

|

||

|

|

|

tF |

|

|

|

|

|

tLF |

|

|

|

tLOGILP |

S*tPTA |

tPDI |

tSLEW |

|

tIN |

tLOGI |

|

|

||

D/T |

Q |

tOUT |

|||

|

|

||||

|

|

tSUI tCOI |

|

||

|

tPTCK |

tHI |

|

||

|

|

tAOI |

|

||

|

|

|

tEN |

||

tGCK |

tPTSR |

> |

tRAI |

||

|

|

SR |

|

||

tGSR |

|

|

|

|

|

|

tPTTS |

|

|

|

|

tGTS |

|

|

|

|

|

Рис. 16. Детальная временная модель

12 15 августа 2001 г. Краткое техническое описание

R |

Семейство XC9500XV |

|

|

Табл. 4. Параметры временной модели |

|

|

|

Распределитель тер- |

Макроячейка в режи- |

Задержка на- |

|

Описание |

Параметр |

мов задействован |

ме малого потребле- |

растания |

|

|

|

|

ния |

фронта |

|

Задержка распространения |

tPD |

+tPTA*S |

+tLP |

+tSLEW |

|

Время установки глобального |

tSU |

+tPTA*S |

+tLP |

- |

|

тактового сигнала |

|||||

|

|

|

|

||

Задержка глобального такто- |

tCO |

- |

- |

+tSLEW |

|

вого сигнала выхода |

|||||

|

|

|

|

||

Время установки PTC |

tPSU |

+tPTA*S |

+tLP |

- |

|

Задержка тактового сигнала |

tPCO |

|

|

+tSLEW |

|

до выхода с использованием |

- |

- |

|||

термов |

|

|

|

|

|

Внутренний системный пери- |

tSYSTEM |

+tPTA*S |

+tLP |

- |

|

од |

|||||

|

|

|

|

Характеристики при включении питания

Во время включения питания МС семейства XC9500XV используют внутреннюю схему, которая удерживает МС в состоянии ожидания до тех пор, пока напряжение питания VCCINT не достигнет безо-

пасного значения (приблизительно 1.9 В). В это время все контакты микросхемы, включая JTAG, не доступны для каких-либо действий и подтянуты к высокому уровню (см. Табл. 5). По достижении безопасного значения напряжения, инициализируются пользовательские регистры и МС немедленно доступна для работы (см. Рис. 17). Время инициализации ~300мкс.

Если МС не запрограммирована, то все контакты микросхемы, за исключением JTAG, не доступны для каких-либо действий и подтянуты к высокому уровню.

Табл. 5. Характеристики при включении питания

Если МС запрограммирована, то все выходы и входы находятся в состояниях соответствующих конфигурации, а JTAG-контакты доступны для операций программирования в системе и периферийного сканирования.

VCCINT

1.9 Â

0 Â |

Состояние |

|

Состояние |

|

Рабочее состояние |

||

|

ожидания |

||

|

|

ожидания |

|

|

|

|

Инициализация регистров

Рис. 17. Поведение МС во время включения питания

Цепи МС |

Состояние ожи- |

Не запрограммирован- |

Рабочее состояние |

|

дания |

ная МС |

|||

|

|

|||

Bus-hold |

Pull-up |

Pull-up |

Удержание последнего состоя- |

|

ния |

||||

|

|

|

||

Выходы |

не активно |

не активно |

как запрограммировано |

|

Входы и тактовые цепи |

не активно |

не активно |

как запрограммировано |

|

ФБ |

не активно |

не активно |

как запрограммировано |

|

JTAG-контроллер |

не активно |

активно |

активно |

Программное обеспечение проектирования

Разработка проекта поддерживается универсаль-

ным пакетом ПО Xilinx Foundation Series, поддер-

живающего все ПЛИС Xilinx, а также специализированным бесплатным ПО WebPack, доступным через Интернет (http://www.xilinx.com).

15 августа 2001 г. Краткое техническое описание |

13 |