- •Особенности

- •Обзор семейства

- •Функциональный блок

- •Макроячейка

- •Распределитель термов

- •Блок ввода-вывода

- •Банки ввода-вывода

- •Возможность закрепления контактов

- •Программирование в системе

- •Защита проекта от копирования

- •Режим пониженного потребления энергии

- •Модель задержек распространения сигналов

- •Характеристики при включении питания

- •Программное обеспечение проектирования

- •Характеристики семейства XC9500XV по постоянному току

- •Микросхема XC9536XV

- •Описание

- •Потребление тока

- •Динамические параметры микросхем XC9536XV

- •Параметры временной модели

- •Корпуса

- •Обозначение микросхем XC9536XV

- •Микросхема XC9572XV

- •Описание

- •Потребление тока

- •Динамические параметры микросхем XC9572XV

- •Параметры временной модели

- •Корпуса

- •Обозначение микросхем XC9572XV

- •Микросхема XC95144XV

- •Описание

- •Потребление тока

- •Динамические параметры микросхем XC95144XV

- •Параметры временной модели

- •Корпуса

- •Обозначение микросхем XC95144XV

- •Микросхема XC95288XV

- •Описание

- •Потребление тока

- •Динамические параметры микросхем XC95288XV

- •Параметры временной модели

- •Корпуса

- •Обозначение микросхем XC95288XV

- •СОДЕРЖАНИЕ

R

Перепрограммируемые в системе ПЛИС CPLD семейства XC9500XV

15 августа 2001 г. Краткое техническое описание

Особенности

•Оптимизированное для работы в высокопроизводительных системах с напряжением питания 2.5 В семейство ПЛИС CPLD

-Задержка от входа до выхода по всем выводам до 3.5 нс

•Расширенная возможность защиты схемы от копирования

•Полная поддержка периферийного сканирования в соответствии со стандартом IEEE Std 1149.1 (JTAG)

•Возможность параллельного программирования нескольких МС семейства XC9500XV

- |

Внутренняя системная частота до 275 МГц |

• |

Совместимость по выводам с семейством |

|

- |

Корпуса малого размера VQFP, TQFP и |

|||

|

XC9500XL в одинаковых корпусах |

|||

|

CSP |

• Поддержка функции «горячей замены» |

||

|

|

|||

-Совместимость с 3.3 В, 2.5 В и 1.8 В сигна-

лами |

Обзор семейства |

|

- Потребление тока в 1,5-2 раза меньше чем |

||

Семейство XC9500XV имеет структуру, аналогич- |

||

в семействе XC9500XL |

||

- Производятся по технологии 0.35 мкм |

ную структуре семейства XC9500. Микросхемы это- |

|

го типа могут быть использованы для создания не- |

||

КМОП FastFLASHTM |

стандартных АЛУ, дешифраторов, мультиплексо- |

|

• Содержит четыре МС, различающихся по сте- |

ров и т.д., т.е. таких устройств, где требуется логи- |

|

ческие функции многих переменных и небольшое |

||

пени интеграции |

||

количество триггеров. МС семейства XC9500XV |

||

|

-От 36 до 288 макроячеек, или от 800 до 6 могут использоваться в крупносерийной аппарату-

|

400 вентилей |

|

ре, а также в системах, где требуется перепро- |

|

• |

Возможность перепрограммирования в систе- |

граммирование “на ходу”. |

||

Напряжение питания ядра микросхемы 2.5 В. Каж- |

||||

|

ме |

|

||

|

- Не менее 10 000 циклов запись/стирание |

дый пользовательский блок ввода-вывода совмес- |

||

|

тим по входу с 3.3 В, 2.5 В и 1.8 В логическими сиг- |

|||

|

|

|

||

|

- Программирование/стирание в |

полном |

налами и может выдавать 3.3 В, 2.5 В и 1.8 В логи- |

|

|

коммерческом и промышленном диапазоне |

ческие сигналы. Семейство XC9500XV спроектиро- |

||

|

напряжения питания и температур |

|

вано специально для работы в системах совместно |

|

|

- Гарантированный срок сохранения конфи- |

с ПЛИС семейств Virtex, Virtex-E, Spartan-II и Spar- |

||

|

tan-XL, и позволяет оптимально распределить бы- |

|||

|

гурации 20 лет |

|

струю интерфейсную логику и логику общего на- |

|

• Расширенные возможности закрепления выво- |

значения в данных системах. |

|||

|

||||

|

дов перед трассировкой |

|

Для программирования МС семейства XC9500XV |

|

• |

Наличие гибкого функционального |

блока |

не требуется программатор – перепрограммирова- |

|

ние осуществляется сигналами от элементов с на- |

||||

|

54V18 |

|

||

|

|

пряжением питания 2.5 В через специальные вы- |

||

|

|

|

||

|

- Любая из 18 макроячеек функционального |

воды МС (JTAG-порт) в той же системе, где и при- |

||

|

блока может выполнять логическую функ- |

меняется данная ПЛИС. Минимальное число цик- |

||

|

цию 54 переменных от 1 до 90 термов |

лов перепрограммирования МС превышает 10 000. |

||

|

- Глобальные и программируемые тактовые |

Записанная конфигурация может сохраняться бо- |

||

|

лее 20-ти лет. |

|||

|

сигналы, сигнал разрешение выхода, сиг- |

|||

|

В состав семейства XC9500XV входят четыре МС, |

|||

|

налы установки и сброса триггера |

|

||

• Программируемый режим пониженной потреб- |

емкостью от 36 до 288 макроячеек (от 800 до 6 400 |

|||

вентилей, соответственно) в различных корпусах. |

||||

|

ляемой мощности в каждой макроячейке |

|||

|

Все МС семейства XC9500XV совместимы по кон- |

|||

• Управление задержкой сигнала по любому из |

тактам, что обеспечивает возможность легкого пе- |

|||

рехода от одной МС к другой в том же корпусе. |

||||

|

выходов |

|

||

|

|

Также все МС семейства XC9500XV совместимы по |

||

• |

Возможность назначения пользователем “об- |

|||

контактам с МС семейства XC9500. В Табл. 1 пред- |

||||

|

щего” вывода |

|

ставлены основные параметры МС семейства |

|

|

|

|

XC9500XV, а в Табл. 2 все доступные корпуса с |

|

• Наличие в каждом программируемом БВВ схе- |

указанием количества пользовательских контактов. |

|

мы удержания последнего состояния |

||

|

15 августа 2001 г. Краткое техническое описание |

1 |

Семейство XC9500XV |

R |

|

Табл. 1. МС семейства XC9500XV |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

XC9536XV |

XC9572XV |

XC95144XV |

XC95288XV |

|||

Число макроячеек |

|

|

|

36 |

72 |

144 |

288 |

||||

Число вентилей |

|

|

|

800 |

1 600 |

3 200 |

6 400 |

||||

Число триггеров |

|

|

|

36 |

72 |

144 |

288 |

||||

Задержка вход МС – комбинаторная логика – вы- |

|

3.5 |

4 |

4 |

5 |

||||||

ход МС, tPD[нс] |

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|||

Время установки глобального тактового сигнала, |

|

2.8 |

3.1 |

3.1 |

3.7 |

||||||

tSU[нс] |

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|||

Задержка глобального тактового сигнала до вы- |

|

1.8 |

2.0 |

2.0 |

2.5 |

||||||

хода, tCO[нс] |

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|||

fSYSTEM[МГц] |

|

|

|

275 |

250 |

250 |

222 |

||||

Количество банков блоков ввода вывода |

|

|

1 |

1 |

2 |

4 |

|||||

Примечание: fSYSTEM=внутренняя частота для проектов, использующих несколько функциональ- |

|||||||||||

ных блоков |

|

|

|

|

|

|

|

|

|

||

Табл. 2. Доступные корпуса и количество пользовательских контактов (не учитывая JTAG-контактов) |

|||||||||||

|

|

|

|

|

|

|

|

|

|||

|

|

|

XC9536XV |

XC9572XV |

XC95144XV |

XC95288XV |

|

|

|||

|

PLCC-44 |

|

34 |

34 |

|

|

|

|

|

|

|

|

VQFP-44 |

|

34 |

34 |

|

|

|

|

|

|

|

|

CSP-48 |

|

36 |

38 |

|

|

|

|

|

|

|

|

TQFP-100 |

|

|

72 |

|

81 |

|

|

|

|

|

|

TQFP-144 |

|

|

|

|

117 |

|

117 |

|

|

|

|

CSP-144 |

|

|

|

|

117 |

|

|

|

|

|

|

PQFP-208 |

|

|

|

|

|

|

168 |

|

|

|

|

FBGA-256 |

|

|

|

|

|

|

192 |

|

|

|

|

CSP-280 |

|

|

|

|

|

|

192 |

|

|

|

Описание архитектуры семей-

ства XC9500XV

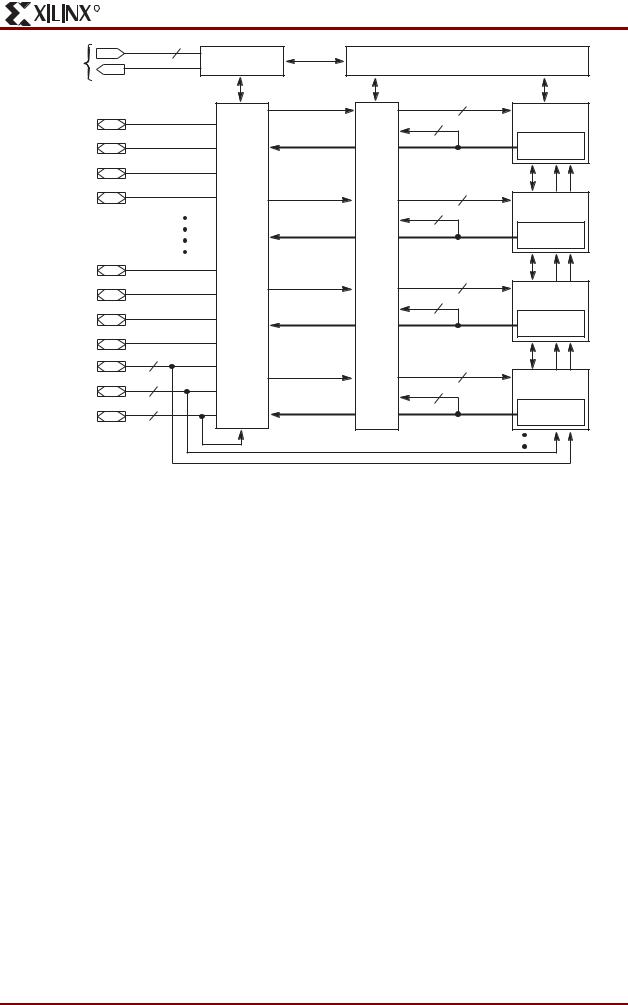

Каждая МС семейства XC9500XV представляет собой подсистему, состоящую из множества функциональных блоков (ФБ) и блоков ввода-вывода (БВВ), соединенных переключающей матрицей

(ПМ) (Рис. 1).

БВВ обеспечивают буферизацию всех входов и выходов МС. Каждый ФБ содержит 18 макроячеек со структурой 54V1 и позволяет получить 18 логических функций практически от любой комбинации из 54 переменных.

ПМ обеспечивает подачу любых выходных сигналов ФБ и входных сигналов на входы ФБ. До 18 выходных сигналов каждого ФБ (в зависимости от количества выводов в корпусе) и соответствующие сигналы разрешения выхода поступают непосредственно на блоки ввода-вывода.

Все выводы ПЛИС семейства XC9500XV можно подразделить на 3 группы:

1.Выводы JTAG-порта, через которые производится периферийное сканирование и программирование

2.Логические выводы, которые могут выполнять функцию входа, выхода или совмещенного входа-выхода (I/O)

3.Управляющие выводы, на которые подаются глобальные управляющие сигналы синхронизации (GCK), установки/сброса (GSR) и управления третьим состоянием (GTS). Управляющие выводы могут также выполнять функции логических выводов.

Также имеются выводы “земли” и питания, причем раздельно питаются блоки ввода-вывода (от напряжения питания VCCIO) и все остальные (от на-

пряжения питания VCCINT).

2 |

15 августа 2001 г. Краткое техническое описание |

R |

Семейство XC9500XV |

|

JTAG |

3 |

JTAG |

Контроллер программирования |

|

|||

Ïîðò |

|

Контроллер |

в системе |

|

|

54 |

I/O |

18 |

ÔÁ 1 |

|

||

I/O |

|

Ìß 1...18 |

I/O |

|

|

I/O |

|

54 |

|

ÔÁ 2 |

|

|

18 |

|

|

|

|

ÁÂÂ |

ÏÌ |

Ìß 1...18 |

|

||

I/O |

|

54 |

|

|

|

I/O |

18 |

ÔÁ 3 |

|

|

|

I/O |

|

Ìß 1...18 |

|

|

|

I/O |

|

|

3 |

|

|

I/O/GCK |

|

54 |

1 |

18 |

ÔÁ N |

I/O/GSR |

|

|

2 èëè 4 |

|

Ìß 1...18 |

I/O/GTS |

|

|

|

|

|

Рис. 1. Архитектура МС семейства XC9500XV |

|

|

Функциональный блок

Функциональный блок (Рис. 2) состоит из 18-ти независимых макроячеек (МЯ), каждая из которых обеспечивает выполнение комбинаторной и/или регистровой функции. Кроме этого, на ФБ приходят сигналы разрешения выхода, установки/сброса и глобальной синхронизации. Каждый ФБ формирует 18 выходных сигналов, которые поступают на ПМ, а также передаются в БВВ.

Логика внутри ФБ представляет собой матрицу логических произведений (термов). 54 входа обеспе-

чивают использование 108-ми прямых и инверсных сигналов в матрице логических произведений для формирования до 90 термов. Любое подмножество этих термов может быть доступно каждой МЯ через схему распределения термов.

Каждый ФБ имеет внутренние цепи обратной связи, что позволяет любому количеству выходных сигналов ФБ поступать в свою собственную программируемую матрицу И, не выходя за пределы ФБ.

15 августа 2001 г. Краткое техническое описание |

3 |

Семейство XC9500XV |

|

|

|

|

R |

|

|

|

|

|

|

||

|

|

|

Ìß 1 |

|

|

|

|

Матрица |

|

термов |

|

|

|

|

логических |

|

|

|

|

|

|

произведений |

|

|

|

||

|

Распределитель |

|

|

|

||

|

|

|

18 |

Ê ÏÌ |

||

|

|

|

|

|

||

54 |

|

|

|

|

|

|

Îò ÏÌ |

|

|

18 |

OUT |

||

|

|

|

||||

|

|

|

18 |

|

Ê ÁÂÂ |

|

|

|

|

PTOE |

|||

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

Ìß 18 |

|

|

|

|

|

|

1 |

3 |

|

|

|

|

|

Глобальный |

Глобальные |

|

|

|

|

|

сброс/установка |

сигналы |

|

|

|

|

|

|

тактирования |

|

|

Рис. 2. Схема функционального блока МС семейства XC9500XV |

|

|

||||

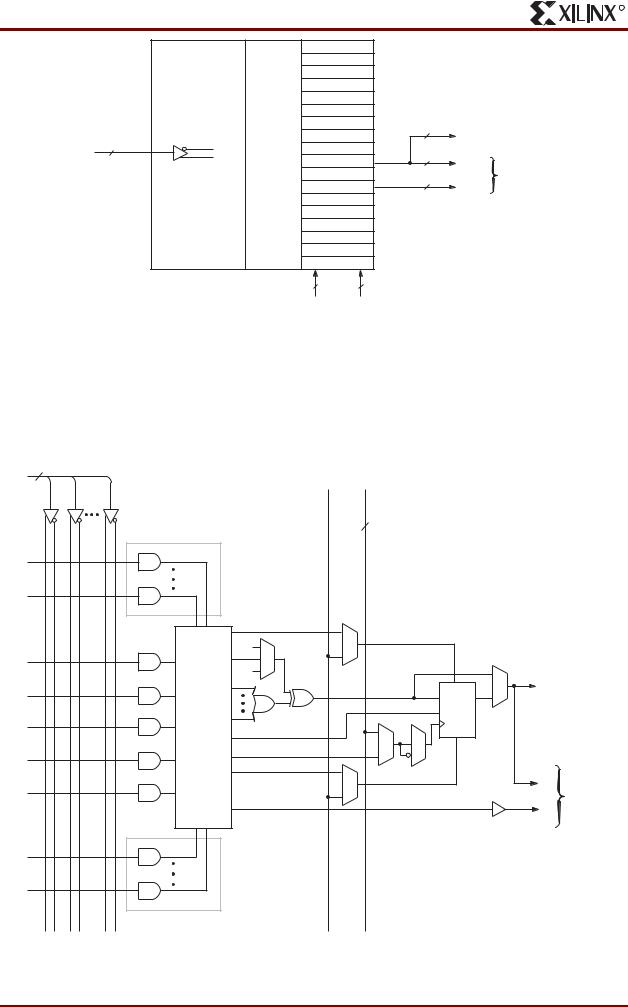

Макроячейка |

|

|

|

так и регистровую функции. Структура макроячейки |

||

Любая макроячейка в МС семейства XC9500XV |

совместно с программируемой матрицей логиче- |

|||||

ских произведений (элементов И, или “термов”), |

||||||

может выполнять как логическую комбинаторную, |

принадлежащим всему ФБ, представлена на Рис. 3. |

|||||

54 |

|

|

|

|

|

|

|

|

|

Глобальный |

Глобальные сигналы |

||

|

|

|

Сброс/Установка |

тактирования |

|

|

|

|

|

|

3 |

|

|

|

|

Дополнительные |

|

|

|

|

|

|

входы от других |

|

|

|

|

|

|

макроячеек |

|

|

|

|

|

|

|

PTS |

|

|

|

|

|

|

1 |

|

|

|

|

термов |

|

0 |

|

|

|

|

|

|

|

S |

Ê ÏÌ |

|

|

|

|

|

D/T |

Q |

|

|

Распределитель |

|

|

|

EC |

|

|

|

PTCE |

|

R |

|

|

|

|

PTC |

|

|

|

|

|

|

PTR |

|

|

OUT |

|

|

|

|

|

|

||

|

|

|

|

|

Ê ÁÂÂ |

|

|

|

|

PTOE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PTOE |

|

|

Дополнительные |

|

|

|

|

|

|

входы от других |

|

|

|

|

|

|

макроячеек |

|

|

|

|

Рис. 3. Макроячейка МС семейства XC9500XV |

|

|

|

|||

4 |

15 августа 2001 г. Краткое техническое описание |