- •САПР Xilinx Foundation Series

- •ВХОД В СИСТЕМУ

- •Открытие нового проекта

- •ВВОД И РЕДАКТИРОВАНИЕ СХЕМЫ

- •Как задать размер листа и присвоить ему имя

- •ОСНОВНЫЕ ОПЕРАЦИИ

- •Выбор элемента

- •Перемещение элемента или фрагмента схемы

- •Удаление элемента

- •Присвоение имени элементу

- •Рисование цепи

- •Перемещение цепи

- •Удаление цепи

- •Присвоение имени цепи

- •Переименование цепи

- •Удаление имени цепи

- •Задание констант 0 и 1

- •ШИННЫЕ СОЕДИНЕНИЯ

- •Пример простого шинного соединения

- •Шинные контакты элемента

- •Правила соединений

- •Простые и сложные шины

- •Примеры шинных соединений

- •Редактирование изображения шины

- •Контроль соединений

- •Сохранение схемы

- •ФОРМИРОВАНИЕ СОБСТВЕННОЙ БИБЛИОТЕКИ МОДЕЛЕЙ ЭЛЕМЕНТОВ

- •СОЗДАНИЕ МАКРОЭЛЕМЕНТА НА ОСНОВЕ БАЗОВЫХ ЭЛЕМЕНТОВ

- •Создание макроэлемента

- •Выбор макроэлемента из библиотеки

- •Редактирование УГО макроэлемента

- •ВВОД И ОТЛАДКА МАКРОЭЛЕМЕНТА НА VHDL

- •Ввод описания макроэлемента

- •Ввод описания архитектуры объекта с использованием Language Assistant

- •Сохранение документа

- •Проверка синтаксиса

- •Редактирование текста описания

- •Синтез макроэлемента

- •Создание VHDL-макроса

- •Выбор макроса из библиотеки

- •Редактирование УГО макроэлемента

- •Коррекция VHDL-описания макроэлемента

- •Автоматическое создание модели памяти

- •Редактирование начального состояния памяти

- •ФУНКЦИОНАЛЬНОЕ МОДЕЛИРОВАНИЕ СХЕМЫ

- •Окно моделирования схемы

- •Выбор контрольных точек схемы

- •Удаление контрольных точек из окна моделирования

- •Изменение порядка имен в окне моделирования

- •Задание входных воздействий

- •Задание синхросигналов

- •Как отсоединить генератор от внешнего входа схемы

- •Задание входных воздействий в окне моделирования

- •Выполнение моделирования схемы

- •Сохранение результатов моделирования

- •Моделирование макроэлемента

- •РЕАЛИЗАЦИЯ ПРОЕКТА НА ПЛИС

- •ПОДГОТОВКА СХЕМЫ ДЛЯ РАЗМЕЩЕНИЯ ЕЁ НА ПЛИС

- •Универсальный лабораторный стенд

- •Макроэлементы органов управления стенда

- •Подключение макроэлементов стенда к проекту

- •РАЗМЕЩЕНИЕ СХЕМЫ НА КРИСТАЛЛЕ

- •ВРЕМЕННОЕ МОДЕЛИРОВАНИЕ СХЕМЫ

- •Измерение задержек на временной диаграмме

- •ЗАГРУЗКА ПРОЕКТА В ПЛИС

- •ПРОСМОТР РЕЗУЛЬТАТОВ РАЗМЕЩЕНИЯ СХЕМЫ

- •ВВЕДЕНИЕ В ЯЗЫК VHDL

- •ВЫБРАННЫЕ МЕСТА ИЗ ОПИСАНИЯ ЯЗЫКА VHDL

- •Структура описания объекта проекта

- •Интерфейс объекта проекта

- •Синтаксис

- •Тип сигнала

- •О правилах записи программы

- •Описание архитектуры объекта

- •Синтаксис

- •Параллельные операторы

- •Стили описаний архитектур

- •Элементы потокового проектирования

- •Элементы поведенческого проектирования

- •VHDL-стандарты IEEE

- •Пакеты std_logic_arith, std_logic_signed u std_logic_unsigned

- •Библиотеки и пакеты

- •Логические элементы

- •Триггеры

- •Мультиплексоры

- •Дешифратор

- •Сумматоры

- •Счетчики

- •Регистры

- •Исходные данные

- •Составление программной модели АЛУ

- •СПИСОК ЛИТЕРАТУРЫ

Примечание. Как видно из рис. П.1.23 и П.1.25, графическое обозначение и наименование выводов триггеров FTCLE и FTCLEX полностью совпадают. Однако рассмотрение способов их реализации позволяет выявить различие при выполнении микрооперации загрузки (см. рис. П.1.24 и П.1.26).

Если активен сигнал на входе L, то по фронту тактового сигнала триггер принимает состояние, определяемое входом D. Однако для триггера FTCLE такая загрузка возможна при отсутствии активного сигнала на входе разрешения CE (такое разрешение формируется элементом OR2 при наличии активного уровня на входе L), а для триггера FTCLEX загрузка возможна только при наличии активного уровня на входе СЕ (см. табл. П.1.9 и П.1.10).

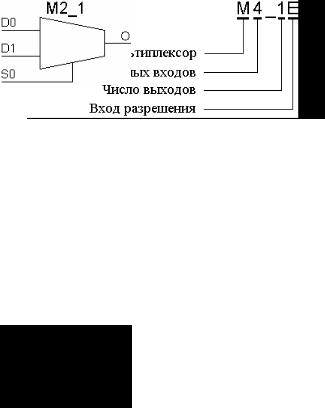

Мультиплексоры

Пример соглашения для обозначения мультиплексоров в библиотеке элементов приведен на рис. П.1.27.

Рис. П.1.27. Обозначение мультиплексоров

Мультиплексор 2-1 (M2_1)

Мультиплексор выбирает один информационный вход из двух источников (D1 или D0) в зависимости от состояния управляющего входа S0. Выход (O) принимает состояние выбранного входа данных. При S0 = 0 на выходе появляется состояние входа D0, при

S0 = 1 – D1.

Условное графическое обозначение мультиплексора приведено на рис. П.1.28, а его таблица истинности представлена табл. П.1.11.

Рис. П.1.28. Условное графическое обозначение мультиплексора M2_1

154

|

|

|

|

|

Таблица П.1.11 |

|

|

Таблица истинности мультиплексора M2_1 |

|

|

|||

|

|

|

|

|

Выход |

|

|

|

Входы |

|

|

|

|

S0 |

|

D1 |

D0 |

|

O |

|

1 |

|

1 |

X |

|

1 |

|

1 |

|

0 |

X |

|

0 |

|

0 |

|

X |

1 |

|

1 |

|

0 |

|

X |

0 |

|

0 |

|

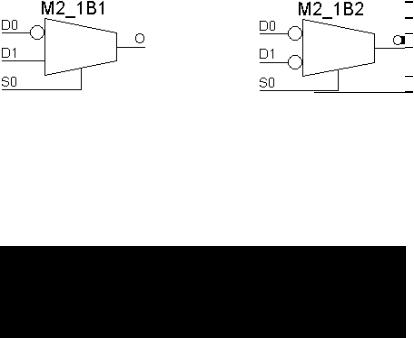

Мультиплексоры 2-1 с инверсными входами (M2_1B1 и M2_1B2)

Условные графические обозначения мультиплексоров с инверсными входами приведены на рис. П.1.29. Данные мультиплексоры отличаются от предыдущего наличием одного или двух инверсных входов, что отражено на их условном графическом обозначении

(см. рис. П.1.29).

Рис. П.1.29. Условное графическое обозначение мультиплексоров с инверсными входами

Мультиплексор 2-1 с входом разрешения (M2_1E)

Условное графическое обозначение мультиплексора M2_1Е приведено на рис. П.1.30.

Вход Е разрешает работу мультиплексора. Когда разрешающий вход E = 1, то мультиплексор M2_1E выбирает один из информационных входов (D1 или D0) в зависимости от состояния управляющего входа S0. При Е = 0 состояние выхода равно 0.

Таблица истинности мультиплексора M2_1Е представлена табл. П.1.12.

155

|

|

|

|

|

Рис. П.1.30. Условное графическое |

||

|

|

|

|

|

обозначение мультиплексора M2_1Е |

||

|

|

|

|

|

|

|

Таблица П.1.12 |

|

|

|

|

|

|

|

|

|

|

Таблица истинности мультиплексора M2_1Е |

|

||||

|

|

|

|

|

|

|

|

|

|

|

Входы |

|

|

Выход |

|

|

E |

S0 |

|

D1 |

|

D0 |

O |

|

0 |

X |

|

X |

|

X |

0 |

|

1 |

0 |

|

X |

|

1 |

1 |

|

1 |

0 |

|

X |

|

0 |

0 |

|

1 |

1 |

|

1 |

|

X |

1 |

|

1 |

1 |

|

0 |

|

X |

0 |

Мультиплексор 4-1 с входом разрешения (M4_1E)

Условное графическое обозначение мультиплексора M4_1Е приведено на рис. П.1.31.

Рис. П.1.31. Условное графическое обозначение мультиплексора M4_1Е

Вход Е разрешает работу мультиплексора. Когда разрешающий вход E = 1, то мультиплексор M4_1E выбирает один из четырех информационных входов (D3, D2, D1 или D0) в зависимости от со-

156

стояния управляющих (адресных) входов S1 и S0. При Е = 0 состояние выхода равно 0.

Таблица истинности мультиплексора M4_1Е представлена табл. П.1.13.

Таблица П.1.13

Таблица истинности мультиплексора M4_1Е

|

|

|

Входы |

|

|

|

Выход |

E |

S1 |

S0 |

D0 |

D1 |

D2 |

D3 |

O |

0 |

X |

X |

X |

X |

X |

X |

0 |

1 |

0 |

0 |

D0 |

X |

X |

X |

D0 |

1 |

0 |

1 |

X |

D1 |

X |

X |

D1 |

1 |

1 |

0 |

X |

X |

D2 |

X |

D2 |

1 |

1 |

1 |

X |

X |

X |

D3 |

D3 |

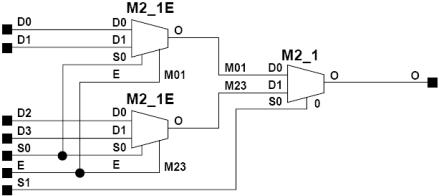

Структура мультиплексора M4_1Е приведена на рис. П.1.32.

Рис. П.1.32. Внутренняя структура мультиплексора M4_1Е

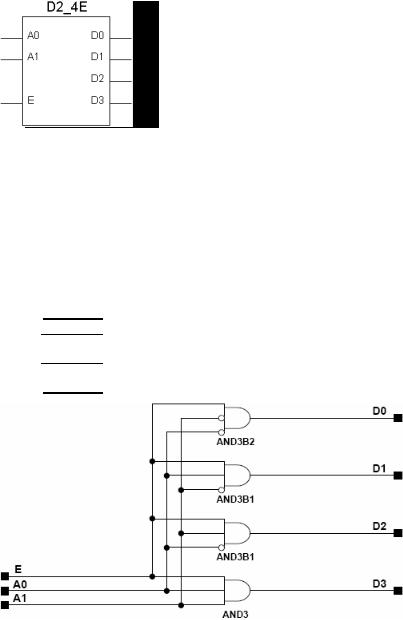

Дешифратор

Дешифратор 2-4 с входом разрешения (D2_4E)

Условное графическое обозначение дешифратора D2_4E приведено на рис. П.1.33.

157

Рис. П.1.33. Условное графическое обозначение дешифратора D2_4E

Дешифратор преобразует двухразрядный двоичный код, поступающий на входы А0, А1, в четырехразрядный унитарный код на выходах D0 ÷ D3, при наличии сигнала высокого уровня на входе разрешения Е (табл. П.1.14).

Дешифратор D2_4E является макроэлементом, его структура приведена на рис. П.1.34.

|

|

|

|

|

|

|

|

|

Таблица П.1.14 |

|

|

|

|

Таблица истинности дешифратора D2_4E |

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

Входы |

|

|

Выходы |

|

|

|||

E |

|

A1 |

|

A0 |

D0 |

D1 |

|

D2 |

|

D3 |

0 |

|

X |

|

X |

0 |

0 |

|

0 |

|

0 |

1 |

0 |

|

0 |

1 |

0 |

|

0 |

|

0 |

|

1 |

0 |

|

1 |

0 |

1 |

|

0 |

|

0 |

|

1 |

1 |

|

0 |

0 |

0 |

|

1 |

|

0 |

|

1 |

|

1 |

|

1 |

0 |

0 |

|

0 |

|

1 |

Рис. П.1.34. Внутренняя структура дешифратора D2_4E

158