Терехин. Учебное пособие

.pdf

Существенным недостатком предлагаемой Simulink схемы SIFU Synchronized 6*Pulse Generator является одновременный запуск интегра торов Integrator1 и Integrator2 в начальный момент времени и одновре менное формирование сигнала управления по нескольким каналам (см. временную диаграмму на рис. 1.99).

Рис. 1.99. Временная диаграмма расположения импульсов управления при заданном угле управления 30

Анализ показывает, что в начальный момент включения схемы SIFU формируются импульсы управления по всем каналам одновременно. Это обстоятельство приводит к аварийному режиму работы преобразователя.

Теоретически режим упорядочивания моментов включения инте граторов (процесс синхронизации) длится один период питающего на пряжения 0,02 с. Практически введение блокировки формирования импульсов по входу Block на время 0,01 с исключает аварийный режим.

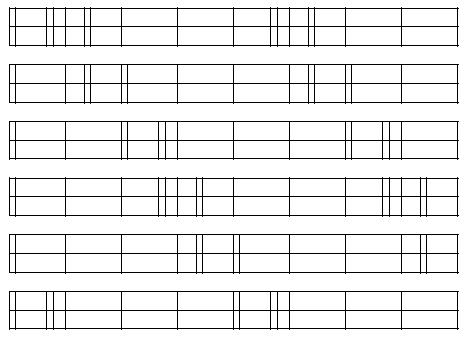

На рис. 1.100 представлена схема модели нереверсивного трёхфазно го мостового тиристорного преобразователя с модернизированной SIFU. Предлагаемая схема повторяет схему на рис. 1.91 за исключением моде ли SIFU, схема которой переработана и предлагается к применению (рис. 1.101). Временная диаграмма работы отдельных наиболее важных элементов показана на рис. 1.102.

Запуск интеграторов Integrator1 осуществляется импульсами пере хода синусоидальных синхронизирующих напряжений через нуль в по ложительном направлении путём записи единицы в триггеры Flip*

101

Flop1. Именно с этого момента начинается рост напряжения интеграто ров шести каналов. Данный факт наглядно подтверждается второй ди аграммой на рис. 1.102. Через 5/6 периода питающего напряжения, че рез селектор триггеры Flip*Flop1 сбрасываются на нуль, рост напряже ний на интеграторах прекращается. Однако это обстоятельство не вно сит ограничений на формирование импульсных сигналов необходимой фазы, так как ограничение интеграторов наступает в зоне углов, значи тельно превышающих максимальный угол π.

|

|

g |

+ |

+ |

i |

|

|

|

|

|

|||

A |

A |

A |

- |

|

||

|

|

|

||||

|

In |

|

|

|||

B |

B |

B |

|

Series RLC Branch |

||

|

|

|||||

C |

C |

C |

- |

|

|

|

|

|

|

|

+ |

v |

|

|

|

Universal Bridge |

|

|||

|

|

|

- |

|

||

|

|

|

|

|

Un |

|

|

|

|

|

|

InMean |

Scope |

+ |

|

Uy |

|

|

|

|

v |

AB |

|

|

InMean |

|

|

- |

|

BC |

pulses |

|

|

|

|

|

|

|

|

||

+ |

v |

CA |

|

|

|

|

- |

|

Block |

|

|

|

|

|

|

|

|

|

|

|

SIFU LM

|

|

|

|

40 |

|

|

1 |

|

|

|

|

|

+ |

v |

|

|

|

|

s |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

- |

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

Scope1 |

|

|

|

|

Constant |

Integrator |

|

|

|

|||||

|

|

|

||||||||||

|

|

|

|

|

|

|

||||||

Рис. 1.100. Схема модели нереверсивного трёхфазного мостового тиристорного преобразователя с модернизированной SIFU (Fig 1_100)

Следует отметить, что триггерами Flip*Flop1 можно и не управлять по входу R, так как очередным сигналом с блока Hit Grossing интегратор перезапустится.

Рабочий сигнал управления тиристором в этой схеме формируется триггерами Flip*Flop2, в которые записываются единицы по моменту равенства напряжений интегратора Integrator1 и напряжения, пропор ционального заданному углу управления. После записи единицы в со ответствующий триггер Flip*Flop2 запускается интегратор Integrator2, задающий длительность управляющего сигнала на включение тиристо ра. Триггеры Flip*Flop2 сбрасываются на нуль сигналами схем сравне ния Relational Operator2. Рост напряжений интеграторов ограничивает ся. Однако очередным сигналом схемы сравнения Relational Operator1 интеграторы Integrator2 перезапускаются, а задающее напряжение обес печивают триггеры Flip*Flop2 после записи единицы.

102

1 |

7 |

alpha |

|

-K- |

>= |

RAMP>alpha |

|

|

|||||

|

|

|

||||

Uy |

k alpha |

|

Saturation |

Talpha3 |

Relational |

|

|

|

Operator1 |

||||

|

|

|

|

|

||

|

|

S |

|

|

|

|

|

|

|

|

g1 |

|

|

|

Q |

double |

-K- |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

g2 |

|

||||

|

|

R |

|

|

|

|

|

|

|

|

|

|

|

Selector1 |

Flip-Flop1 |

|

|

freq |

|

|

|

|

|

g3 |

|

|

|

|

|

|

|

|

|

|

|

|||

4 |

-1 |

|

Integrator1 |

|

|

|

|

OR |

g4 |

|

||

|

|

|

|

|

g5 |

|

||||||

CA |

Gain |

|

|

1 |

|

|

boolean |

|

|

|

||

|

|

|

|

|

|

Logical |

g6 |

|

||||

|

|

|

|

s |

|

RAMP |

|

|

|

|

||

2 |

-1 |

|

|

|

|

|

|

|

Operator1 |

|

|

|

|

|

|

|

|

|

|

|

Scope |

|

|||

AB |

Mux |

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

Selector |

|

|

||

Gain1 |

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

s |

|

|

> |

boolean |

|

|

|

||

|

|

Hit |

|

|

|

|

|

|

|

|||

3 |

-1 |

|

|

|

|

|

|

|

|

|

|

|

Crossing |

Integrator2 |

Relational |

|

|

Double_Pulse |

double |

1 |

|||||

BC |

|

|

|

|

|

Operator2 |

|

|

||||

Gain2 |

|

|

|

|

|

AND |

|

|

pulses |

|||

|

|

|

|

|

|

|

|

|

|

|||

103 |

Mux |

|

pwidth |

|

-K- |

|

|

NOT |

|

|

Double Pulse |

|

|

|

Pwidth |

|

Twidth1 |

|

Logical |

Logical |

|

|

|

||

|

|

|

|

|

|

|

|

Operator3 |

|

|

|

|

|

|

|

|

|

|

|

|

Operator |

|

|

|

|

|

boolean |

|

5 |

|

|

boolean |

|

S |

|

|

||

|

|

|

|

|

|

|

|

|||||

|

|

|

Block |

|

|

|

|

|

boolean |

Q |

|

|

|

|

|

|

|

|

|

|

|

R |

|

|

|

|

|

|

|

|

|

|

|

|

|

Flip-Flop |

|

|

|

|

|

|

START_PULSE |

AND |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

NOT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Logical |

|

Logical |

|

|

|

|

|

|

|

|

|

|

Operator2 |

S |

Operator5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q |

double |

-K- |

|

|

|

|

|

|

|

|

|

|

R |

|

|

|

|

|

|

|

|

|

|

|

|

Flip-Flop2 |

|

freq1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 1.101. Модернизированная схема модели системы импульсно*фазового управления SIFU LM |

|

||||||||||

Рис. 1.102. Временная диаграмма работы SIFU LM

На рис. 1.103 представлены результаты моделирования процесса включения преобразователя при минимальном угле управления на ак тивно индуктивную нагрузку. Напряжение управления преобразовате лем ±10 В.

Важно отметить, что задержка в управлении обусловлена дискрет ностью управления преобразователем и не является следствием блоки ровки по входу Block.

Известно, что синхронные импульсно фазовые устройства реали зуются по принципу вертикального управления с линейным и косинус оидальным опорными напряжениями. SIFU с линейным опорным на пряжением были рассмотрены выше. В составе библиотеки SimPower* Systems SIFU с косинусоидальным опорным напряжением нет. Прове дём разработку этого вопроса и рассмотрим один из возможных спосо бов реализации такого типа SIFU (SIFU А).

На рис. 1.104 представлена схема модели тиристорного преобразо вателя с косинусоидальным опорным напряжением. Синхронизирую щие и опорные напряжения вырабатываются с помощью дополнитель ного трёхфазного источника с амплитудным напряжением 10 В (напри мер, вторичная обмотка силового трансформатора).

104

Рис. 1.103. Запуск преобразователя при напряжении управления +10 В

Основные параметры SIFU A вводятся через диалоговое окно (рис. 1.105), открываемое двойным щелчком правой кнопки мыши по изображению блока SIFU A.

Через окно вводится частота синхронизирующего напряжения, длительность импульсов управления и начальный угол управления пре образователем в градусах. Для управления мостовым тиристорным пре образователем необходимо кнопку Double pulsing включить.

На рис. 1.106 показана схема модели разработанной системы им пульсно фазового управления с косинусоидальным опорным напряже нием SIFU A.

Проследим процесс формирования импульсного сигнала только по первому каналу на временной диаграмме (рис. 1.107).

105

0 |

|

|

|

|

|

|

|

|

Multimeter |

|

|

g |

|

|

|

|

|

|

|

|

|

i |

|

|

|

|

|

|

|

+ |

+ |

|

|

|

|

A |

|

A |

- |

|

|

|

||

|

A |

|

|

|

|

|||

|

In |

|

|

|

|

|||

B |

|

B |

B |

|

|

|

|

|

|

|

|

|

|

|

|||

C |

|

C |

- |

|

|

|

|

|

|

C |

|

+ |

|

|

|||

|

|

|

Universal Bridge B |

|

v |

Scope2 |

||

|

|

|

|

- |

|

|||

|

|

|

|

|

|

Un |

|

|

|

150 |

1 |

|

|

|

|

|

Uy |

|

s |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

Integrator |

|

|

|

|

|

Block |

|

|

|

Step |

|

|

|

|

UB |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Pulses |

|

|

|

|

|

|

|

|

UC |

|

|

|

|

|

|

|

|

UA |

|

|

|

|

|

|

|

|

UO |

SIFU A

Step1 Sine Wave

Рис. 1.104. Нереверсивный тиристорный преобразователь с SIFU косинусоидального типа SIFU A (Fig 1_104)

Рис. 1.105. Окно ввода параметров

106

|

1 |

+ |

v |

-1 |

|

|

|

|

|

|

|

|

|

UB |

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

-1/100 |

|

boolean |

|

|

|

|

|

2 |

+ |

v |

-1 |

Derivative |

|

|

|

|

|

|

|

|

UC |

- |

|

|

|

>= |

|

|

|

|

Double_Pulse |

|

|

|

|

pwidth |

1/360 |

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

Pwidth |

|

Relational |

|

>= |

|

|

|

|

|

|

|

|

|

Operator1 |

|

|

|

|

|

||

du/d |

3 |

+ |

|

|

1 |

|

AND |

|

|

Double Pulse |

||

v |

-1 |

|

|

|

|

|||||||

|

|

Relational |

|

|

||||||||

UA |

- |

s |

|

|

|

|

|

OR |

||||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

107 |

|

|

|

|

Integrator1 |

|

|

Operator |

Logical |

U |

U(E) |

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

double |

Operator |

|

|

Logical |

|

4 |

|

|

|

|

|

|

|

Selector |

|||

|

|

|

|

|

|

|

|

|

Operator2 |

|||

|

UO |

|

|

10*cos(alpha*pi/180) |

|

|

Hit |

|

|

|

|

|

|

|

|

|

|

Crossing |

|

|

|

|

|

||

|

1 |

|

|

|

boolean |

NOT |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Uy |

|

|

U alpha |

S |

|

|

Logical |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

||

|

2 |

|

|

|

Q |

double |

freq |

Operator1 |

|

|

|

|

|

|

|

|

R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Block |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6 Flip-Flop |

|

|

|

|

|

|

|

|

|

|

|

|

6.123e-016 |

|

|

|

|

|

|

|

|

|

|

|

|

Display |

|

|

|

|

|

|

|

double |

1 |

|

Pulses |

Scope1

Рис. 1.106. Схема модели системы импульсно*фазового управления с косинусоидальным опорным напряжением SIFU A

t

Ub , Uy

10 |

0 |

- 10 |

Hit Grossing

1

0. 5

0

Log Signal Derivative

1 |

|

0. 5 |

|

0 |

|

pwidth |

1 Integrator |

, |

1 |

0.02 |

|

0. 01 |

|

0 |

|

1 Flip - Flop

1

0.5

0

1 g

1

0.5

0 |

0 |

0.005 |

0.01 |

0.015 |

0.02 |

0.025 |

0.03 |

0.035 |

0.04 |

0.045 |

0.05 |

Рис. 1.107. Временная диаграмма формирования сигнала управления по первому каналу

Синхронизирующие и одновременно опорные напряжения с выхода мультиплексорной шины поступают на схемы сравнения Relational Operator с напряжением управления Uy и на схему выделения отрицательного перепада опорного напряжения (Derivative с усилителем, инвертирующим знак произ водной). После выполнения равенства опорного напряжения управляющему на выходе схемы сравнения Relational Operator формируется логический сиг нал единичного уровня и подаётся на второй вход логической схемы AND. В этот же интервал времени формируется логический сигнал единичного уров ня, подтверждающий, что сравнение произошло на участке отрицательного перепада опорного напряжения. Этот логический сигнал подаётся на четвёр тый вход схемы AND. По положительному перепаду сигнала на выходе схемы сравнения Relational Operator сбрасывается на нуль интегратор Integrator1. В триггер Flip*Flop по входу S записывается единица. На вход интегратора посту пает задающее напряжение, и начинается процесс формирования заданной длительности pwidth импульса управления включением тиристора. По дости жении текущего значения выходного напряжения интегратора, равного на пряжению, заданного pwidth, сигналом с выхода Relational Operator1 по входу R триггер Flip*Flop возвращается в нулевое состояние.Выход триггера Flip*Flop коммутирует первый вход логической схемы AND и, по существу, определяет появление выходного сигнала SIFU А по соответствующему каналу, фаза ко торого (угол управления) определяется напряжением управления и уставкой начального угла. Схема подключения осциллографа показана на рис. 1.108.

108

du/d

109

|

|

|

|

|

|

|

|

|

|

|

|

Scope1 |

|

1 |

+ |

v |

-1 |

|

|

|

|

|

|

|

|

|

|

UB |

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

-1/100 |

|

boolean |

|

|

|

|

|

|

2 |

+ |

v |

-1 |

Derivative |

|

|

|

|

|

|

|

|

|

UC |

- |

|

|

|

>= |

|

|

|

|

Double_Pulse |

double |

1 |

|

|

|

pwidth |

1/360 |

|

|

|

|

||||||

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

Pulses |

||

|

|

|

Pwidth |

|

Relational |

|

|

|

|

|

|

|

|

|

|

|

|

|

>= |

|

|

|

|

|

|

||

|

|

|

|

Operator1 |

|

|

|

|

|

|

|

||

3 |

+ |

|

|

1 |

|

AND |

|

|

|

Double Pulse |

|

||

v |

-1 |

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|||||||

UA |

- |

s |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

Relational |

|

|

|

OR |

|

|

|||

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

Operator |

|

|

|

|

|

|

|

|

|

|

Integrator1 |

|

|

Logical |

U |

U(E) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

double |

Operator |

|

|

Logical |

|

|

4 |

|

|

|

|

|

|

|

Selector |

|

|

|||

|

|

|

|

|

|

|

|

Operator2 |

|

|

|||

UO |

|

|

10*cos(alpha*pi/180) |

|

|

Hit |

|

|

|

|

|

|

|

|

|

|

|

Crossing |

|

|

|

|

|

|

|

||

1 |

|

|

|

boolean |

NOT |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Uy |

|

|

U alpha |

S |

|

|

Logical |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

||

2 |

|

|

|

Q |

double |

freq |

Operator1 |

|

|

|

|

|

|

|

|

|

R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Block |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6 Flip-Flop |

|

|

|

|

|

|

|

|

|

6.123e-016

Display

Рис. 1.108. Схема подключения осциллографа для построения временной диаграммы работы первого канала SIFU A

t

Рис. 1.109. Ток и напряжение тиристорного преобразователя при линейно нарастающем напряжении управления (α0 = 90 )

На рис. 1.109 показаны результаты моделирования работы тири сторного преобразователя, управляемого SIFU А с косинусоидальным опорным напряжением при подаче на вход линейно нарастающего на пряжения управления.

Анализ полученного результата моделирования позволяет утвер ждать, что коэффициент усиления тиристорного преобразователя при рассматриваемом способе управления является постоянной величиной.

1.3.3. Нереверсивный нулевой трёхфазный тиристорный преобразователь

На рис. 1.110 представлена нулевая схема тиристорного преобразо вателя. Для упрощения схемы преобразователь собран из отдельных ти ристоров. Так как предполагается использовать имеющуюся в составе Si* mulink SIFU, то производится разводка импульсов управления. На входе Block введена блокировка формирования импульсов управления на 0,01 с.

В диалоговом окне установки параметров SIFU необходимо вы ключить кнопку в строке Double pulsing. На входе alpha_deg SIFU дей ствует линейно нарастающий сигнал от 120 до 0 , что позволяет убе диться в работоспособности преобразователя.

110