- •Учебное пособие по дисциплине: «Прикладная электроника» Северск, сгти - 2003

- •Предисловие

- •1 Импульсная и цифровая техника

- •1.1 Общие сведения

- •1.2 Ключевой режим работы биполярных транзисторов

- •1.3 Импульсный режим работы операционных усилителей. Компараторы. Триггер Шмитта

- •1.4 Позиционные системы счисления

- •1.5 Функции алгебры логики и их основные свойства

- •1.5.1 Основные определения

- •1.6 Элементарные функции алгебры логики

- •1.7 Аналитическая запись функций алгебры логики

- •1.8 Аксиомы, основные теоремы и тождества алгебры логики

- •1.9 Минимизация функций алгебры логики

- •1.9.1 Основные определения

- •1.9.2 Постановка задачи минимизации в классе днф

- •1.9.3 Аналитическая минимизация

- •4.9.4 Метод неопределенных коэффициентов и минимизирующих карт

- •1.9.5 Метод минимизирующих карт

- •1.9.6 Карты Карно

- •2 Цифровые интегральные схемы

- •2.1 Логические элементы

- •2.1.1 Логический элемент не

- •2.1.2 Логический элемент или

- •2.1.3 Логический элемент и

- •2.1.4 Логический элемент или - не

- •2.1.5 Логический элемент и - не

- •2.2 Классификация

- •2.3 Основные характеристики и параметры лэ

- •2.3.1 Сравнение обобщенных параметров цифровых микросхем

- •2.3.2 Типовые корпуса микросхем

- •2.4 Элементы с памятью (триггеры, счетчики)

- •2.4.1 Триггеры сR,Sуправлением

- •2.4.2 Триггеры с синхронным управлением

- •2.4.3 Триггеры сJk-управлением

- •2.4.4 Триггеры сD-управлением

- •2.4.5 Разное

- •3 Вопросы анализа и синтеза невременных схем

- •3.1 Логические сети

- •3.2 Теорема анализа и эквивалентные схемы

- •3.3 Синтез логических схем с одним выходом

- •3.4 Синтез логических схем со многими выходами

- •3.5 Синтез схем по неполностью определенным собственным функциям

- •3.6 Пример синтеза устройства - преобразователя кодов

- •4 Синтез и анализ схем, работа которых зависит от времени

- •4.1 Временные булевы функции. Основные определения

- •4.2 Основные свойства временных булевых функций

- •4.3 Синтез и анализ схем с помощью временных булевых функций

- •5 Схемотехника элементов интегрального исполнения

- •5.1 Схемотехника элементов серий ттл

- •5.1.1 Основные принципы построения схем

- •5.1.2 Основные параметры и характеристики серий ттл

- •5.1.3 Функциональный состав ттл ис и ттлш ис

- •5.2 Схемотехника элементов серий кмоп

- •5.2.1 Инвертор на комплиментарной моп-паре

- •5.2.2 Основные логические элементы и-не, или-не,z

- •5.2.3 Функциональный состав кмоп ис

- •5.2.4 Основные характеристики ис к564

- •5.2.4.1 Энергетические характеристики

- •5.2.4.2 Передаточные характеристики

- •5.2.4.3 Помехоустойчивость

- •5.2.4.4 Быстродействие

- •5.2.4.5 Напряжение питания

- •5.2.4.6 Входные характеристики

- •5.2.4.7 Нагрузочная способность

- •5.2.4.8 Надежность ис к564

- •5.2.5 Основные характеристики ис cерии кр1554

- •5.2.5.1 Технические характеристики

- •5.2.5.3 Предельные электрические режимы эксплуатации микросхем серии кр1554

- •5.2.5.4 Функциональный состав микросхем серии кр1554

5.2.2 Основные логические элементы и-не, или-не,z

В основе_всех_цифровых микросхем КМОП находятся три логических элемента: И-НЕ, ИЛИ-НЕ и коммутационный ключ (КК). С помощью КК реализуются выходы с третьим состоянием очень большого выходного импедансаZ (практически разомкнуто). Полевые транзисторы можно соединять последовательно («столбиком»), поэтому элементы И-НЕ, ИЛИ-НЕ строятcя по разным схемам и в отличие от ТТЛ здесь не надо переименовывать логические уровни. Для КМОП принято, чтобы 1 отображалась высоким уровнем, а 0 - низким.

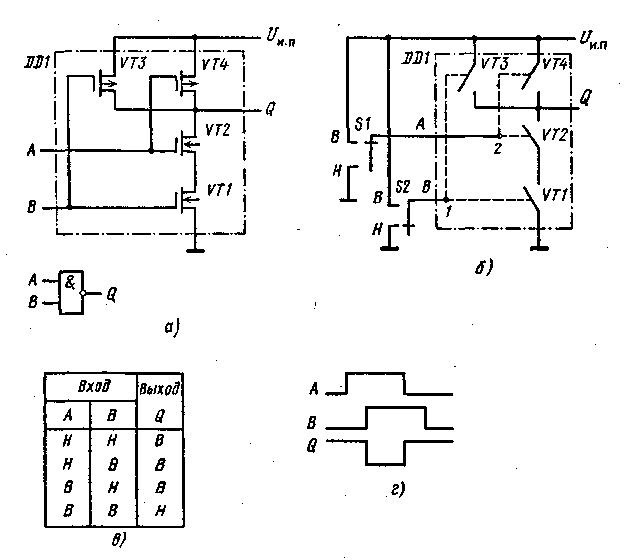

а - схема; б - эквивалентная схема управления; в - таблица электрических состояний схемы; г – диаграмма входных b выходных импульсов

Рис. 5.12 - Двухвходовой элемент И-НЕ

На рис. 5.12, а показана принципиальная схема двухвходового элемента И-НЕ. Это один канал из микросхемы К176ЛА7. На рис. 5.12, б эта схема изображена в виде эквивалента с подключенными управляющими переключателями S1 и S2. Здесь транзисторы VT1—VT4 заменены однополюсными тумблерами.

Если последовательно перебрать все комбинации напряжений высоких и низких уровней, поступающих на входы А и В от S1 и S2, и рассмотреть уровни на выходе Q, получим таблицу состояния схемы И-НЕ (рис. 5.12, в). Если от S1 и S2 на входы А и В подать напряжения высокого уровня (В), п-каналы транзисторов VT1 и VT2 будут замкнуты, а каналы VT3 и VT4 разомкнуты. На выходе Q окажется напряжение низкого уровня (Н). Если на вход А или В поступает хотя бы один низкий уровень, один из каналов VT3 или VT4 оказывается замкнутым и на выходе Q появляется напряжение высокого уровня. В результате вертикальная колонка данных на выходе Q (рис. 5.12, в) соответствует функции И-НЕ.

Если на входы А и В подать два положительных импульса (см. рис. 5.12, г) сигнал на выходе Q будет соответствовать площади их совпадения (но с инверсией!).

Таблица 5.5 - Микросхемы КМОП И-НЕ

В табл. 5.5 перечислены микросхемы КМОП с логикой И-НЕ, входящие в серии К176 и К561, а также указаны их зарубежные аналоги из серий CD4000A и CD4000B.

а - схема; б — эквивалентная схема управления; в — таблица электрических состояний; е — диаграмма входных и выходных импульсов

Рис. 5.13 - Двухвходовый элемент ИЛИ-НЕ

Устройство базового элемента ИЛИ-НЕ (рис. 5.13, а) — это один канал микросхемы К176ЛЕ5, как бы обратное по сравнению с элементом И-НЕ, здесь параллельно соединены n-канальные и последовательно р-канальные транзисторы. На рис. 5.13, б дана эквивалентная схема, где транзисторы заменены ключами. Только совпадение низких входных уровней на входах А и В даст высокий уровень на выходе Q, так как в этот момент замыкаются оба верхних р-канальных транзистора VT1 и VT2. Присутствие хотя бы одного высокого уровня В на входах А, В означает замыкание одного из параллельных п-канальных транзисторов VT3, VT4.

Состояние выхода Q в зависимости от уровней, последовательно поступающих от переключателей S1 и S2, показаны на рис. 5.13, в. Этот столбик данных соответствует функции ИЛИ-НЕ. На рис. 5.13, г помещена осциллограмма отклика на выходе ИЛИ-НЕ. Здесь длительность (инвертированного!) сигнала на выходе Q соответствует времени обоих входных сигналов. Сводка микросхем ИЛИ-НЕ приведена в табл. 5.6.

Таблица 5.6 - Микросхемы КМОП ИЛИ-НЕ (ЛЕ) и инверторы (ЛН)

Чтобы построить логический элемент с тремя состояниями, последовательно с выходом инвертора надо добавить последовательный двухполярный полевой ключ коммутации КК.

На рис. 5.14, а за инверторомDD1 следует пара разнополярных полевых транзисторовVT1 иVT2. Показаны управляющие затворами потенциалы с противоположными фазами Ф1 и Ф2:р-каналVT2 замкнется при низком уровне импульса Ф2,п-канал — при высоком уровне Ф1. На периодt1ключ коммутации КК разомкнут, поскольку на затворыVT1 иVT2 поданы закрывающие уровни. На времяt2КК замыкается, так как сразу оба транзистораVT1 иVT2 получат открывающие сигналы Ф1 = В и Ф2 = Н.

Эквиваленты схемы (рис. 5.14, а) показаны

на рис. 5.14,б, в. Здесь в дополнение

к предыдущей схеме имеется инверторDD1, формирующий две фазы

сигнала управления Ф1 и Ф2=![]() .

Канал данных разомкнется в случае,

показанном на рис. 5.14,б, когда от

переключателяS1 подается

напряжение низкого уровня. Выходная

цепь схемы станет высокоомной, с очень

большим сопротивлениемZ.

Сигналы от входа в выходной провод

пройти не могут. Выходы после ключа

коммутации КК можно непосредственно

присоединять к общей шине данных. На

схеме (рис. 5.14,в) показана фазировка

управляющих сигналов, при которой КК

замкнут и выход данным разрешается.

.

Канал данных разомкнется в случае,

показанном на рис. 5.14,б, когда от

переключателяS1 подается

напряжение низкого уровня. Выходная

цепь схемы станет высокоомной, с очень

большим сопротивлениемZ.

Сигналы от входа в выходной провод

пройти не могут. Выходы после ключа

коммутации КК можно непосредственно

присоединять к общей шине данных. На

схеме (рис. 5.14,в) показана фазировка

управляющих сигналов, при которой КК

замкнут и выход данным разрешается.

а — ключ коммутации; б — размыкание выхода (Z-состояние);в — разрешение выходу

Рис. 5.14. Элемент с третьим Z-состоянием

Используя инверторы с третьим состоянием Z, когда их выходы требуется соединить, важно, как и для микросхем ТТЛ, соблюдать правило: сигналы разрешения должны быть сформированы так, чтобы для соседних каналов они не перекрывались (по-другому, должен быть защитный интервал — пауза).