- •А. М. Ланских электронные устройства

- •Глава 1.Электронные ключевые элементы и устройства 6

- •Глава 1.Электронные ключевые элементы и устройства

- •1.1. Основные понятия

- •1.2. Ключи на биполярных транзисторах

- •1.3. Ключевые каскады на полевых транзисторах.

- •Сравнение схем ключей на биполярных и полевых транзисторах

- •Глава 2. Цифровые ключи на биполярных и полевых транзисторах.

- •Глава 3. Аналоговые ключи и переключатели

- •3.1. Аналоговые ключи

- •3.2. Схемы управления аналоговыми ключами

- •3.3. Аналоговые коммутаторы

- •Аналоговый коммутатор с памятью

- •Глава 4. Источники вторичного электропитания

- •4.1. Классификация источников вторичного электропитания

- •4.2. Параметрические стабилизаторы

- •4.3. Компенсационные стабилизаторы

- •4.4. Стабилизаторы постоянного тока

- •4.5. Импульсные стабилизаторы напряжения

- •Глава 5. Логические элементы

- •5.1. Общие сведения

- •5.2. Основные характеристики и параметры логических элементов

- •5.3. Схемотехника базовых логических элементов

- •5.3.1. Диодно-транзисторная логика

- •5.3.2. Транзисторно-транзисторная логика

- •5.3.3. Транзисторно-транзисторная логика с диодами Шоттки

- •5.3.4. Эмиттерно-связанная логика

- •5.3.5. Интегральная инжекционная логика

- •5.3.6. Базовые логические элементы на униполярных транзисторах

- •5.3.7. Сравнительная таблица основных параметров логических элементов

- •5.3.8. Согласование в логических схемах

- •Глава 6. Генераторы импульсов

- •6.1. Классификация генераторов импульсов

- •6.2. Генераторы линейно изменяющегося напряжения

- •6.3. Генераторы прямоугольных импульсов

- •Глава 7. Триггерные устройства

- •7.1. Общие сведения

- •7.2. Транзисторные симметричные триггеры

- •7.3 Триггеры на основе логических интегральных микросхем

- •7.4 Несимметричные триггеры

- •Электронные устройства

Сравнение схем ключей на биполярных и полевых транзисторах

Сравнивая ключи на биполярных и полевых транзисторах в статических состояниях, можно сказать, что ключи на полевых транзисторах выигрывают по остаточным параметрам: току утечки в разомкнутом состоянии и остаточному напряжению в замкнутом состоянии, что позволяет использовать их для замыкания микровольтных цепей.

Сравнивая динамические параметры ключей на биполярных и полевых транзисторах можно сделать вывод о том, что биполярные ключевые элементы являются более быстродействующими. Частотный диапазон полевых транзисторов и наличие эквивалентных емкостей не позволяют обеспечить быстрые процессы переключения. Однако для насыщенного ключа на биполярном транзисторе характерно большое время рассасывания, что требует применения различных методов повышения быстродействия за счет использования ненасыщенного режима ключевого транзистора. Такими методами являются применение дополнительного источника в базовой цепи и использование форсирующего конденсатора. Однако эти методы не могут быть применены при интегральном исполнении ключевых элементов.

По основным характеристикам (выходным и характеристикам передачи) несколько лучше ключевой элемент на биполярном транзисторе, поскольку у биполярного транзистора выше коэффициент передачи. По управляющей (входной) цепи лучше ключи на полевых транзисторах, которые обладают очень большим входным сопротивлением.

Глава 2. Цифровые ключи на биполярных и полевых транзисторах.

В цифровой технике широко распространены логические элементы на основе ключей, у которых управляющие и коммутируемые сигналы имеют форму двоичных импульсов. В установившемся режиме сигналы на входе и выходе цифровых ключей принимают лишь два дискретных значения, условно обозначаемых логическим «0» и логической «1». Если в ключе логическому «0» соответствует низкий уровень напряжения, логической «1» – высокий уровень напряжения, то такой элемент относят к положительной логике.

Качество цифрового ключа определяется следующими основными параметрами: падением напряжения на ключе в замкнутом состоянии, током утечки через ключ в разомкнутом состоянии, скоростью переключения ключа из одного состояния в другое, мощностью, потребляемой цепью управления ключа.

Цифровой ключ должен обеспечивать:

– формирование хорошо различимых и стабильных уровней напряжения, соответствующих логическому «0» и логической «1»;

– коэффициент

усиления по напряжению

![]() ;

;

– инверсию входного сигнала, так как все функционально полные системы логических функций содержат логическую операцию отрицания (инверсии);

– высокое быстродействие.

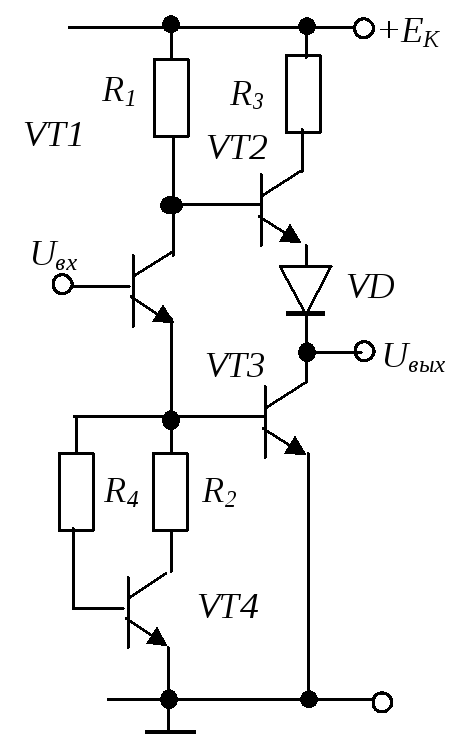

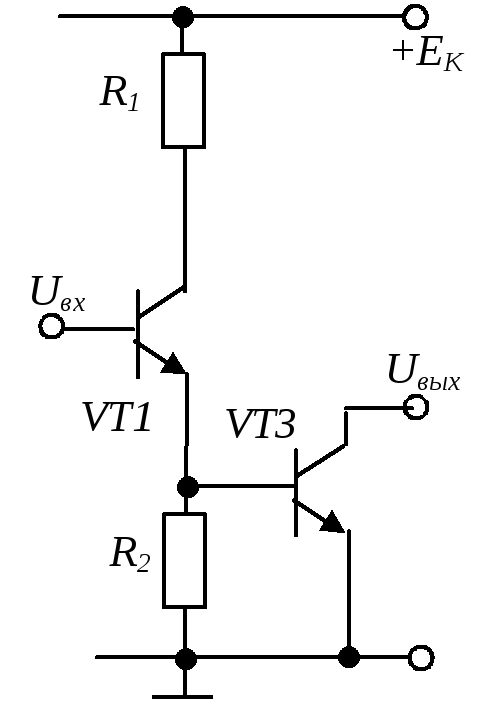

Базовая схема ключа на биполярном транзисторе (рис. 1.4), включенном по схеме с общим эмиттером, удовлетворяет этим требованиям, но не обеспечивает высокого быстродействия. Из всех рассмотренных ранее способов повышения быстродействия ключа на биполярном транзисторе наиболее удобным для реализации по интегральной технологии является схема ненасыщенного ключа с нелинейной отрицательной обратной связью, для организации которой используется диод Шоттки (рис. 1.18).

В

преобладающем большинстве выходных

ключевых каскадов цифровых интегральных

микросхем вместо сопротивления

![]() используется транзистор (динамическая

нагрузка).

используется транзистор (динамическая

нагрузка).

|

Схема

простейшего оконечного ключевого

каскада на транзисторах VT2

и VT3

приведена на рис. 2.1. Каскад на

транзисторе VT1

является предварительным усилителем.

Он осуществляет усиление входных

сигналов и управление выходным

каскадом. При

|

|

|

Рис. 2.1 |

Транзистор

VT2

при этом заперт. Если бы между коллектором

VT3

и эмиттером VT2

не был включен диод VD,

а указанные электроды транзисторов

были соединены непосредственно, то

напряжение на эмиттере VT2

также было бы равно напряжению

![]() насыщенного транзистораVT3.

В этом случае напряжение

насыщенного транзистораVT3.

В этом случае напряжение

![]() транзистораVT2

оказалось бы хоть и близким к напряжению

отсечки, но положительным, что не

обеспечивало бы надежного запирания

транзистора VT2.

Диод VD,

имеющий крутую прямую ветвь ВАХ, при

напряжении между анодом и катодом,

большем напряжения отсечки, даже при

малом значении анодного тока, равном

эмиттерному току запертого транзистора

VT2,

обеспечивает дополнительное смещение

напряжения на эмиттере VT2

в положительную область и надежное

запирание VT2.

Такие диоды называют смещающими.

Использование смещающих диодов – один

из типовых приемов интегральной

технологии, позволяющих обеспечить

надежное запирание выключенных

транзисторов.

транзистораVT2

оказалось бы хоть и близким к напряжению

отсечки, но положительным, что не

обеспечивало бы надежного запирания

транзистора VT2.

Диод VD,

имеющий крутую прямую ветвь ВАХ, при

напряжении между анодом и катодом,

большем напряжения отсечки, даже при

малом значении анодного тока, равном

эмиттерному току запертого транзистора

VT2,

обеспечивает дополнительное смещение

напряжения на эмиттере VT2

в положительную область и надежное

запирание VT2.

Такие диоды называют смещающими.

Использование смещающих диодов – один

из типовых приемов интегральной

технологии, позволяющих обеспечить

надежное запирание выключенных

транзисторов.

Наличие запертого транзистора VT2 в коллекторной цепи насыщенного транзистора VT3 практически исключает потребление тока выходной цепью в состоянии покоя. Коллекторный ток транзистора VT3 может существенно отличаться от нуля только в том случае, когда между выходом схемы и плюсом источника питания включена, например, активная нагрузка. В этом случае коллекторный ток транзистора VT3 равен току нагрузки. Отсутствие собственного потребления тока делает каскад экономичным.

При

![]() транзисторыVT1

и VT3

заперты и находятся в режиме отсечки.

Запертый транзистор VT3

эквивалентен высокоомному резистору

в цепи эмиттера VT2.

Транзистор VT2

в данном состоянии схемы открыт, поскольку

его база через резистор

транзисторыVT1

и VT3

заперты и находятся в режиме отсечки.

Запертый транзистор VT3

эквивалентен высокоомному резистору

в цепи эмиттера VT2.

Транзистор VT2

в данном состоянии схемы открыт, поскольку

его база через резистор

![]() связана с плюсом источника питания.

Каскад на транзистореVT2

работает в режиме эмиттерного повторителя,

создавая на выходе высокий уровень

напряжения, соответствующий уровню

логической «1». Потребление тока в

выходной цепи ненагруженного каскада

благодаря закрытому транзистору VT3

по-прежнему очень мало. Ток эмиттера

транзистора VT2

существенно отличается от нуля только

при наличии нагрузки, включенной между

выходом схемы и корпусом. При наличии

такой нагрузки ток эмиттера транзистора

VT2

равен току нагрузки.

связана с плюсом источника питания.

Каскад на транзистореVT2

работает в режиме эмиттерного повторителя,

создавая на выходе высокий уровень

напряжения, соответствующий уровню

логической «1». Потребление тока в

выходной цепи ненагруженного каскада

благодаря закрытому транзистору VT3

по-прежнему очень мало. Ток эмиттера

транзистора VT2

существенно отличается от нуля только

при наличии нагрузки, включенной между

выходом схемы и корпусом. При наличии

такой нагрузки ток эмиттера транзистора

VT2

равен току нагрузки.

Таким образом, рассмотренная схема имеет:

а) малое потребление тока в ненагруженном состоянии. В каждом из статических состояний схемы один из транзисторов выходного каскада (VT2 или VT3) заперт и ток выходной цепи очень мал;

б) малое выходное сопротивление схемы. В случае логического «0» на выходе малое выходное сопротивление схемы обеспечивается за счет насыщенного транзистора VT3, выходное сопротивление которого является выходным сопротивлением схемы. При наличии логической «1» на выходе малое выходное сопротивление схемы обеспечивается эмиттерным повторителем на транзисторе VT2.

Статические свойства схемы наглядно отражаются ее передаточной характеристикой – зависимостью напряжения на выходе от напряжения на входе. Кусочно-линейная аппроксимация передаточной характеристики рассмотренной схемы (рис. 2.1) приведена на рис. 2.2.

|

|

На

передаточной характеристике можно

выделить следующие характерные

области. При

|

|

Рис. 2.2 |

При

![]() транзисторVT1

открывается и переходит в активный

режим. Коэффициент усиления каскада на

транзисторе VT1

равен

транзисторVT1

открывается и переходит в активный

режим. Коэффициент усиления каскада на

транзисторе VT1

равен

![]() .

Эмиттерный повторитель на транзистореVT2

имеет коэффициент передачи по напряжению

.

Эмиттерный повторитель на транзистореVT2

имеет коэффициент передачи по напряжению

![]() .

Отсюда общий коэффициент усиления в

областиII

равен

.

Отсюда общий коэффициент усиления в

областиII

равен

![]() .

Приращение входного напряжения вызывает

примерно такое же уменьшение выходного

напряжения. При

.

Приращение входного напряжения вызывает

примерно такое же уменьшение выходного

напряжения. При![]() напряжение на эмиттереVT1

повысится настолько, что включится

транзистор VT3,

а транзистор VT2

начнет запираться. В области III

коэффициент усиления схемы

напряжение на эмиттереVT1

повысится настолько, что включится

транзистор VT3,

а транзистор VT2

начнет запираться. В области III

коэффициент усиления схемы

![]() и выходной сигнал при увеличении входного

очень быстро уменьшается. Процесс

переключения завершается насыщением

транзистораVT3.

При дальнейшем увеличении входного

напряжения насыщенный режим работы

транзистора VT3

сохраняется (область IV).

и выходной сигнал при увеличении входного

очень быстро уменьшается. Процесс

переключения завершается насыщением

транзистораVT3.

При дальнейшем увеличении входного

напряжения насыщенный режим работы

транзистора VT3

сохраняется (область IV).

Улучшение

передаточной характеристики каскада

за счет исключения области II

(жирная штриховая линия на рис. 2.2.)

достигается путем замены резистора

![]() транзисторомVT4

так, как это показано на рис. 2.3.

транзисторомVT4

так, как это показано на рис. 2.3.

|

|

Необходимо отметить, что во время переключения (области II и III) ток в цепи питания возрастает и в несколько раз превышает ток, потребляемый в статических режимах. Поэтому при увеличении частоты переключения мощность, потребляемая схемой, растет. В качестве особенности рассматриваемых схем следует указать на недопустимость соединения выходов нескольких схем. Если произвести такое соединение, то в состоянии, когда одна из схем имеет на выходе высокий потенциал, а другая – низкий потенциал, через |

|

Рис. 2.3 |

последовательно соединенные транзистор VT2 одной схемы и транзистор VT3 другой схемы потечет значительный сквозной ток. При этом резко возрастает потребляемая мощность и возможен выход схем из строя, так как транзисторы обычно не рассчитаны на длительное протекание больших токов. Поэтому при проектировании цифровых устройств следует исключать возможность объединения выходов таких элементов.

Однако во многих цифровых устройствах, где несколько узлов или блоков работает на общую магистраль, такое объединение выходов является необходимым. В этом случае используются схемы, которые кроме двух обычных состояний выхода (логического «0» и логической «1») имеют третье, «отключенное» (высокоомное, высокоимпедансное) состояние. Для этого в схему подключается дополнительный управляющий сигнал EZ, который при закрытом транзисторе VT3 одновременно закрывает и транзистор VT2 (рис. 2.4). Условно-графическое обозначение таких схем приведено на рис. 2.5.

|

|

|

Однако и в этом случае при объединении нескольких выходов следует учитывать существенное ограничение: в любой момент времени к общей выходной цепи должен быть подключен выход только одной схемы, а выходы всех остальных схем должны |

|

Рис. 2.4 |

Рис. 2.5 |

находиться в отключенном состоянии. Это достигается соответствующей организацией подачи сигналов на входы EZ каждой из схем.

Если из рассматриваемого выходного каскада (рис. 2.1) исключить транзистор VT2, то получится каскад с открытым коллектором (рис. 2.6).

|

Условно-графическое обозначение таких схем приведено на рис. 2.7, где указано также, что выходы таких каскадов можно подключать к общей нагрузке. При наличии Епит2 и Rк схема обеспечивает существенно |

|

|

|

Рис. 2.6 |

Рис. 2.7 |

большую выходную мощность, чем исходная схема (рис. 2.1) и больший коэффициент полезного действия.

Если в качестве базовой схемы ключа на полевом транзисторе рассматривать схему, приведенную на рис. 1.24, то для реализации цифровых ключей на полевых транзисторах в основном используются две ее разновидности. В обеих разновидностях вместо Rc используется полевой транзистор.

В первой разновидности, называемой МОП-ключом, используется дополнительный транзистор того же типа (с тем же типом канала), что и основной транзистор (рис. 2.8).

|

|

Эта схема может работать в режиме нелинейной нагрузки, квазилинейной нагрузки и токостабилизирующей нагрузки. Однако все эти режимы не являются ключевыми. Это означает, что схема постоянно потребляет энергию от источника питания Ес. Смещение на затвор дополнительного транзистора может подаваться как от |

|

Рис. 2.8 |

источника питания Ес, так и от дополнительного внешнего источника Есм. В последнем случае схема имеет несколько лучшие показатели по быстродействию.

|

Во второй разновидности, называемой КМОП-ключом, используется комплементарный (с другим типом канала) к основному дополнительный транзистор VT2 (рис. 2.9). Преимуществом этой схемы по сравнению с предыдущей является отсутствие потребления энергии от источника питания в статических состояниях ключа. |

|

|

Рис. 2.9 |

Однако во время переключения, как и в биполярных схемах, оба транзистора открыты и потребляют существенную мощность от источника питания за счет сквозного тока. При увеличении частоты переключения мощность, потребляемая схемой, растет.

Для повышения быстродействия коммутации используются схемы, в которых транзисторы работают в активном (ненасыщенном) режиме. Такие схемы называются переключателями тока и предназначены для переключения тока из одной цепи в другую.

|

Схема переключателя (рис. 2.10), представляющая собой дифференциальный каскад с несимметричным входом и несимметричным выходом, состоит из двух идентичных усилителей на транзисторах VT1 и VT2, связанных эмиттерами. |

|

|

Рис. 2.10 |

При

изменении напряжения

![]() ток

ток![]() в эмиттерной цепи переключается из цепи

транзистораVT1

в цепь транзистора VT2,

или наоборот. На базу VT2

подается стабильное опорное напряжение

в эмиттерной цепи переключается из цепи

транзистораVT1

в цепь транзистора VT2,

или наоборот. На базу VT2

подается стабильное опорное напряжение

![]() .

Напряжение на эмиттере

.

Напряжение на эмиттере![]() приблизительно повторяет большее из

двух напряжений:

приблизительно повторяет большее из

двух напряжений:![]() и

и![]() .

.

При

![]() токи и напряжения в плечах схемы

соответственно одинаковы:

токи и напряжения в плечах схемы

соответственно одинаковы:![]() ;

;![]() ;

;![]() ,

где

,

где![]() (десятые доли вольта) – напряжение

(десятые доли вольта) – напряжение![]() на открытом эмиттерном переходе.

на открытом эмиттерном переходе.

Предположим,

что

![]() начинает возрастать от значения

начинает возрастать от значения![]() .

При этом напряжение

.

При этом напряжение![]() тоже увеличивается, а так как

тоже увеличивается, а так как![]() ,

то

,

то![]() уменьшается, т. е. транзисторVT2

начинает запираться. Если считать, что

он запрется при

уменьшается, т. е. транзисторVT2

начинает запираться. Если считать, что

он запрется при

![]() ,

то это произойдет, когда

,

то это произойдет, когда![]() ,

т. е. при

,

т. е. при![]() .

После запирания транзистораVT2

ток

.

После запирания транзистораVT2

ток

![]() переключится в цепь транзистораVT1.

переключится в цепь транзистораVT1.

Если

![]() начинает уменьшаться от уровня

начинает уменьшаться от уровня![]() ,

то напряжение

,

то напряжение![]() тоже уменьшается, так как потенциал

эмиттеров

тоже уменьшается, так как потенциал

эмиттеров![]() задается большим сейчас стабильным

напряжением

задается большим сейчас стабильным

напряжением![]() .

Когда

.

Когда![]() окажется равным

окажется равным![]() ,

т. е. при

,

т. е. при![]() ,

транзисторVT1

запрется и весь эмиттерный ток переключится

в цепь транзистора VT2.

,

транзисторVT1

запрется и весь эмиттерный ток переключится

в цепь транзистора VT2.

Заметим,

что после изменения

![]() транзисторы в процессе переключения

управляются со стороны эмиттеров, т. е.

работают как каскады с общей базой.

Элементы схемы переключателя выбираются

с таким расчетом, чтобы исключить

насыщение транзисторов. Однако в данном

случае коллекторные токи транзисторов

оказываются достаточно стабильными и

в активном режиме. Это объясняется

стабильностью тока эмиттеров

транзисторы в процессе переключения

управляются со стороны эмиттеров, т. е.

работают как каскады с общей базой.

Элементы схемы переключателя выбираются

с таким расчетом, чтобы исключить

насыщение транзисторов. Однако в данном

случае коллекторные токи транзисторов

оказываются достаточно стабильными и

в активном режиме. Это объясняется

стабильностью тока эмиттеров![]() ,

с которым коллекторный ток

,

с которым коллекторный ток![]() каждого транзистора связан коэффициентом

каждого транзистора связан коэффициентом![]() .

Значения коэффициента

.

Значения коэффициента![]() колеблются в десятки раз меньше, чем

значения коэффициента

колеблются в десятки раз меньше, чем

значения коэффициента![]() в схеме с общим эмиттером. Так как

транзисторы работают по схеме с общей

базой, их постоянная времени

в схеме с общим эмиттером. Так как

транзисторы работают по схеме с общей

базой, их постоянная времени![]() ,

а из-за отсутствия насыщения исключается

задержка включения транзистора. В

результате быстродействие переключателя

тока оказывается значительно выше, чем

у ключа с общим эмиттером.

,

а из-за отсутствия насыщения исключается

задержка включения транзистора. В

результате быстродействие переключателя

тока оказывается значительно выше, чем

у ключа с общим эмиттером.

Схема

имеет два выхода, один из которых

![]() – инверсный, а второй

– инверсный, а второй![]() – прямой. Для согласования выходов

переключателя с входами последующих

устройств на выходах рассмотренной

схемы (рис. 2.10) обычно устанавливаются

эмиттерные повторители (VT3

на рис. 2.11).

– прямой. Для согласования выходов

переключателя с входами последующих

устройств на выходах рассмотренной

схемы (рис. 2.10) обычно устанавливаются

эмиттерные повторители (VT3

на рис. 2.11).

|

|

|

|

|

Рис. 2.11 |

Рис. 2.12 |

Рис. 2.13 |

В

этом случае скорость переключения тока

определяется не только параметрами

транзисторов переключателя, но и

величиной сопротивления

![]() .

Этим же сопротивлением определяется и

максимальный выходной ток. При реализации

переключателя тока в интегральном

исполнении сопротивление

.

Этим же сопротивлением определяется и

максимальный выходной ток. При реализации

переключателя тока в интегральном

исполнении сопротивление![]() отсутствует внутри микросхемы (рис. 2.12)

и включается в виде навесного элемента.

При этом величина

отсутствует внутри микросхемы (рис. 2.12)

и включается в виде навесного элемента.

При этом величина![]() выбирается пользователем из условий

обеспечения требуемого выходного тока.

Такой выходной каскад называется выходом

с открытым эмиттером. Эти особенности

выходных каскадов отображаются на УГО

микросхемы так, как показано на рис. 2.13.

выбирается пользователем из условий

обеспечения требуемого выходного тока.

Такой выходной каскад называется выходом

с открытым эмиттером. Эти особенности

выходных каскадов отображаются на УГО

микросхемы так, как показано на рис. 2.13.