- •А. М. Ланских электронные устройства

- •Глава 1.Электронные ключевые элементы и устройства 6

- •Глава 1.Электронные ключевые элементы и устройства

- •1.1. Основные понятия

- •1.2. Ключи на биполярных транзисторах

- •1.3. Ключевые каскады на полевых транзисторах.

- •Сравнение схем ключей на биполярных и полевых транзисторах

- •Глава 2. Цифровые ключи на биполярных и полевых транзисторах.

- •Глава 3. Аналоговые ключи и переключатели

- •3.1. Аналоговые ключи

- •3.2. Схемы управления аналоговыми ключами

- •3.3. Аналоговые коммутаторы

- •Аналоговый коммутатор с памятью

- •Глава 4. Источники вторичного электропитания

- •4.1. Классификация источников вторичного электропитания

- •4.2. Параметрические стабилизаторы

- •4.3. Компенсационные стабилизаторы

- •4.4. Стабилизаторы постоянного тока

- •4.5. Импульсные стабилизаторы напряжения

- •Глава 5. Логические элементы

- •5.1. Общие сведения

- •5.2. Основные характеристики и параметры логических элементов

- •5.3. Схемотехника базовых логических элементов

- •5.3.1. Диодно-транзисторная логика

- •5.3.2. Транзисторно-транзисторная логика

- •5.3.3. Транзисторно-транзисторная логика с диодами Шоттки

- •5.3.4. Эмиттерно-связанная логика

- •5.3.5. Интегральная инжекционная логика

- •5.3.6. Базовые логические элементы на униполярных транзисторах

- •5.3.7. Сравнительная таблица основных параметров логических элементов

- •5.3.8. Согласование в логических схемах

- •Глава 6. Генераторы импульсов

- •6.1. Классификация генераторов импульсов

- •6.2. Генераторы линейно изменяющегося напряжения

- •6.3. Генераторы прямоугольных импульсов

- •Глава 7. Триггерные устройства

- •7.1. Общие сведения

- •7.2. Транзисторные симметричные триггеры

- •7.3 Триггеры на основе логических интегральных микросхем

- •7.4 Несимметричные триггеры

- •Электронные устройства

1.3. Ключевые каскады на полевых транзисторах.

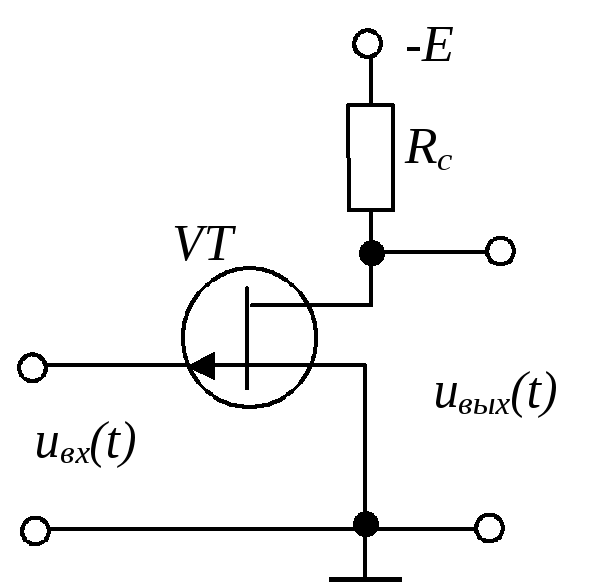

Простейший ключевой каскад на полевом транзисторе с p-каналом и управляющим pn-переходом показан на рис. 1.19.

|

|

|

|

Рис. 1.19 |

Рис. 1.20 |

Будем

считать, что каскад управляется от

источника с очень малым выходным

сопротивлением, т. е. от генератора

напряжения

![]() .

При

.

При

![]() ,

где

,

где![]() –

напряжение запирания транзистора,

полевой

транзистор заперт. При этом можно

считать, что

–

напряжение запирания транзистора,

полевой

транзистор заперт. При этом можно

считать, что

![]() .

При

.

При

![]() (в частности,

при

(в частности,

при

![]() )

транзистор включен. Положение рабочей

точки на стоковой характеристике

отмечено на рис. 1.20; предполагается,

что сопротивление нагрузки в цепи стока

)

транзистор включен. Положение рабочей

точки на стоковой характеристике

отмечено на рис. 1.20; предполагается,

что сопротивление нагрузки в цепи стока![]() ,

т. е. рабочая точка попадает на крутой

участок ВАХ. Остаточное напряжение в

этом случае минимально:

,

т. е. рабочая точка попадает на крутой

участок ВАХ. Остаточное напряжение в

этом случае минимально:![]() ,

где

,

где![]() .

.

Паразитные емкости транзистора и нагрузки обусловливают конечные значения длительности фронта и среза выходного сигнала.

Рассмотрим воздействие на вход каскада переднего фронта входного сигнала, который будем считать идеально крутым (рис. 1.21).

Допущение

о нулевом выходном сопротивлении и

бесконечной мощности источника входных

импульсов

![]() позволяет сделать вывод о

позволяет сделать вывод о

|

том,

что, несмотря на наличие емкости

|

|

|

Рис. 1.21 |

Динамическая эквивалентная схема каскада при отпирании транзистора приведена на рис. 1.22.

|

|

Затвор

и исток по переменной составляющей

сигнала замкнуты через нулевое

выходное сопротивление источника

|

|

Рис. 1.22 |

Емкости

![]() и

и![]() соответствуют

емкости монтажа и нагрузки в выходной

цепи. Между истоком и стоком транзистора

включен конденсатор

соответствуют

емкости монтажа и нагрузки в выходной

цепи. Между истоком и стоком транзистора

включен конденсатор

![]() и скачок напряжения на выходе

и скачок напряжения на выходе![]() .

Так как обычно

.

Так как обычно![]() ,

то

,

то![]() .

После скачка выходного напряжения,

связанного с перераспределением

напряжений на паразитных емкостях при

воздействии скачка входного сигнала,

начинается процесс изменения выходного

напряжения от

.

После скачка выходного напряжения,

связанного с перераспределением

напряжений на паразитных емкостях при

воздействии скачка входного сигнала,

начинается процесс изменения выходного

напряжения от![]() до

до![]() .

С учетом динамической эквивалентной

схемы (рис. 1.22), этот процесс имеет

постоянную времени

.

С учетом динамической эквивалентной

схемы (рис. 1.22), этот процесс имеет

постоянную времени![]() ,

где

,

где![]() .

Длительность фронта выходного сигнала

.

Длительность фронта выходного сигнала![]() .

.

После

завершения формирования фронта импульса

на выходе схемы установится напряжение

![]() .

Положительный перепадвходного

сигнала

.

Положительный перепадвходного

сигнала

![]() от нулевого уровня до уровня

от нулевого уровня до уровня

![]() вызывает запирание транзистора. После

скачка выходного напряжения

вызывает запирание транзистора. После

скачка выходного напряжения

![]() ,

связанного с перераспределением

напряжений на паразитных емкостях

схемы, начинается заряд паразитной

емкости

,

связанного с перераспределением

напряжений на паразитных емкостях

схемы, начинается заряд паразитной

емкости

![]() от источника

от источника

![]() через

через

![]() .

.

|

Динамическая

эквивалентная схема выходной цепи

каскада при запертом транзисторе

показана на рис. 1.23. С учетом указанной

эквивалентной схемы каскада постоянная

времени цепи заряда паразитной емкости

|

|

|

Рис. 1.23 |

длительность

среза импульса

![]() ,

откуда видно, что

,

откуда видно, что

![]() .

.

|

Ключевой

каскад на МДП-транзисторе (рис. 1.24)

работает аналогично. При небольшом

отрицательном напряжении

Для уменьшения мощности, рассеиваемой |

Рис. 1.24 |

|

|

на

ключевом транзисторе, и ускорения

разряда паразитных емкостей вместо

линейного резистора

![]() часто используют

полевой транзистор (динамическую

нагрузку), имеющий проводимость канала,

отличную от проводимости ключевого

транзистора.

часто используют

полевой транзистор (динамическую

нагрузку), имеющий проводимость канала,

отличную от проводимости ключевого

транзистора.

|

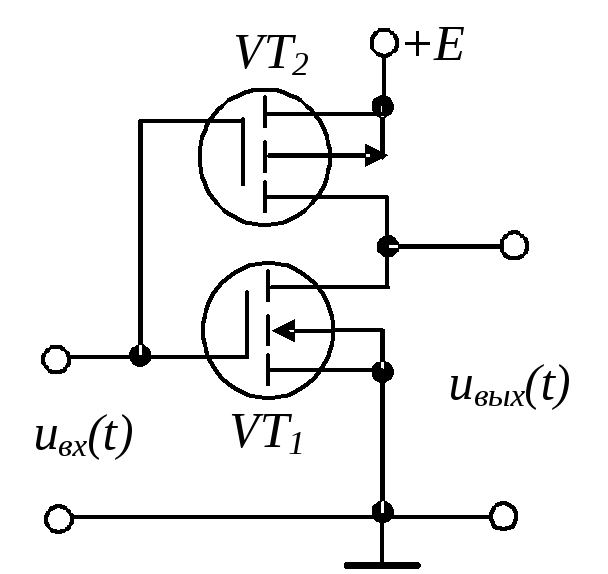

Пример такой схемы на МДП-транзисторах с индуцированными каналами показан на рис. 1.25. Ключевой транзистор VT1 имеет канал n-типа, нагрузочный транзистор VT2 – канал р-типа. Следует, однако, отметить, что деление транзисторов на ключевой и нагрузочный условно, поскольку при работе |

|

|

Рис. 1.25 |

ключевого

каскада переключаются оба транзистора.

Обозначим через

![]() напряжение

запирания транзистора VT1,

через

напряжение

запирания транзистора VT1,

через

![]() –

напряжение запирания транзистора VT2.

Тогда при

–

напряжение запирания транзистора VT2.

Тогда при

![]() транзистор

VT1

заперт, а

транзистор VT2

открыт, так как для него напряжение

затвор –

исток

транзистор

VT1

заперт, а

транзистор VT2

открыт, так как для него напряжение

затвор –

исток

![]() .

При этом обеспечивается соотношение

.

При этом обеспечивается соотношение![]() .

Сквозной ток через каналы транзисторов

равен нулю, так как в этой цепи включен

транзисторVT1,

проводимость

канала которого равна нулю. Потребление

мощности ненагруженной схемой в

статическом режиме равно нулю.

.

Сквозной ток через каналы транзисторов

равен нулю, так как в этой цепи включен

транзисторVT1,

проводимость

канала которого равна нулю. Потребление

мощности ненагруженной схемой в

статическом режиме равно нулю.

При

![]() транзисторVT1

открыт, а

транзистор VT2

заперт, сквозной

ток через каналы транзисторов снова

отсутствует и ненагруженная схема

мощности практически не потребляет. В

течение длительности фронта выходного

импульса может оказаться, что проводят

оба транзистора и через каналы пройдет

импульс сквозного тока. Этот ток

появляется при

транзисторVT1

открыт, а

транзистор VT2

заперт, сквозной

ток через каналы транзисторов снова

отсутствует и ненагруженная схема

мощности практически не потребляет. В

течение длительности фронта выходного

импульса может оказаться, что проводят

оба транзистора и через каналы пройдет

импульс сквозного тока. Этот ток

появляется при

![]() .

За счет импульсов сквозного тока мощность

рассеяния каскада при большой частоте

переключений может увеличиться. Для

исключения импульсов сквозного тока

напряжение питания следует выбирать

из условия

.

За счет импульсов сквозного тока мощность

рассеяния каскада при большой частоте

переключений может увеличиться. Для

исключения импульсов сквозного тока

напряжение питания следует выбирать

из условия![]() .

.

Если указанное условие обеспечено, то стоковый ток транзисторов идет практически только на перезаряд паразитных емкостей в выходной цепи. Паразитная емкость заряжается током стока включенного транзистора VT2, а разряжается током стока включенного транзистора VT1. В обоих случаях в цепи перезаряда имеется канал транзистора, включенного с малым сопротивлением.

Коэффициент

использования питающего напряжения

![]() .

Действительно, при открытом транзистореVT1

.

Действительно, при открытом транзистореVT1

![]() ,

так как напряжение на выходе получается

за счет деления напряжения

,

так как напряжение на выходе получается

за счет деления напряжения

![]() между

сопротивлениями каналов транзисторов

VT1

и VT2.

Второе из этих сопротивлений очень

велико. При открытом транзисторе VT2

между

сопротивлениями каналов транзисторов

VT1

и VT2.

Второе из этих сопротивлений очень

велико. При открытом транзисторе VT2

![]() ,

так как очень

велико сопротивление канала транзистора

VT1.

Амплитуда

выходного сигнала близка к

,

так как очень

велико сопротивление канала транзистора

VT1.

Амплитуда

выходного сигнала близка к

![]() ,

а

,

а

![]() .

.

Благодаря

высокому значению

![]() ,

малой потребляемой мощности, быстрому

заряду и разряду паразитных емкостей

ключевые схемы на полевых транзисторах

с разной проводимостью каналов нашли

широкое распространение в интегральных

переключающих устройствах.

,

малой потребляемой мощности, быстрому

заряду и разряду паразитных емкостей

ключевые схемы на полевых транзисторах

с разной проводимостью каналов нашли

широкое распространение в интегральных

переключающих устройствах.