- •Глава 7.

- •Операционные устройства вычислительных машин

- •Структуры операционных устройств

- •Операционные устройства с жесткой структурой

- •Операционные устройства с магистральной структурой

- •Классификация операционных устройств с магистральной структурой

- •Организация узла рон магистрального операционного устройства

- •Организация операционного блока магистрального операционного устройства

- •Базис целочисленных операционных устройств

- •Сложение и вычитание

- •Целочисленное умножение

- •2N битов. Таким образом, алгоритм умножения предполагает последовательное

- •Алгоритм сдвига влево

- •Умножение чисел со знаком

- •Умножение целых чисел и правильных дробей

- •Модифицированный алгоритм Бута

- •Обработка двух разрядов множителя за шаг

- •Аппаратные методы ускорения умножения

- •Матричное умножение чисел без знака

- •1 Полусумматоры называется одноразрядное суммирующее устройство, имеющее дна входа для слагаемыx и два входа и два выхода — выход бита суммы и выход бита переноса.

- •Матричное умножение чисел в дополнительном коде

- •Алгоритм Бо-Вули

- •Алгоритм Пезариса

- •Древовидные умножители

- •Сравнительная оценка схем умножения с матричной и древообразной структурой

- •Конвейеризация параллельных умножителей

- •Рекурсивная декомпозиция операции умножения

- •Целочисленное деление

- •Деление с восстановлением остатка

- •Деление без восстановления остатка

- •Деление чисел со знаком

- •Устройство деления

- •Ускорение целочисленного деления

- •Замена деления умножением на обратную величину

- •XiD). Количество итераций определяется требуемой точностью вычисления X/d. Реализация метода для n-разрядных чисел требует 2 int(log2n) - 1 операций умножения.

- •Ускорение вычисления частичных остатков

- •Алгоритм srt

- •Деление в избыточных системах счисления

- •Операционные устройства с плавающей запятой

- •Подготовительный этап

- •Заключительный этап

- •Сложение и вычитание

- •Умножение

- •Деление

- •Реализация логических операций

- •Контрольные вопросы

Классификация операционных устройств с магистральной структурой

Магистральные ОПУ классифицируют по виду и количеству магистралей, организации узла РОН, типу ОПБ.

Магистрали ОПУ могут быть однонаправленными и двунаправленными, соответственно обеспечивающими передачу данных в одном или двух различных направлениях. Типичным режимом работы магистрали является разделение времени,

при котором магистраль используется для передачи функционально разнотипных

данных в различные моменты времени.

По функциональному назначению выделяют:

- магистрали «внешних связей, соединяющих ОПУ с памятью и каналами ввода/

вывода ВМ;

- внутренние магистрали ОПУ, отвечающие за связь между узлом РОН и опера-

ционным блоком.

Количество магистралей внешних связей зависит от архитектуры конкретной ВМ и обычно не превышает двух для внешних связей и трех — для внутренних.

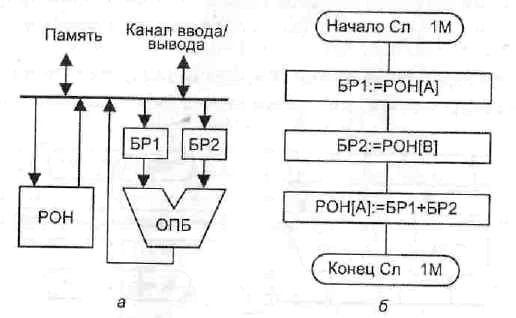

Структура трехмагистрального ОПУ представлена на рис. 7.4, я, а соответствующая ему микропрограмма выполнения операции типа «сложение» — на рис. 7.4, б.

i

Рис. 7.4. Трехмагистральное ОПУ: а — структура; б — микропрограмма сложения

Данный вариант характеризуется наибольшим быстродействием: выборка опе-рандов из РОН, выполнение микрооперации суммирования и запись результата

в РОН — все эти действия производятся за один такт. Основной недостаток трех-

магистральной организации — большая площадь, занимаемая магистралями на кри-

сталле БИС (от 0,16 до 0,22 от площади кристалла).

Двухмагистральная организация при меньшей площади, покрываемой магистралями (от 0,06 до 0,19 от площади кристалла), требует введения как минимум одного буферного регистра (БР), предназначенного для временного хранения одного из операндов (рис. 7.5, а), при этом операция сложения будет выполняться уже за два такта (рис. 7.5, б):

- Такт 1: загрузка БР одним из операндов.

- Такт 2: выполнение микрооперации в ОПБ над содержимым БР и одного из

РOH; запись результата в РОН.

Наконец, организация ОПУ на основе только одной магистрали (рис. 7.6, а)

минимизирует расходы площади (от 0,03 до 0,09 от площади кристалла).

В одномагистральном ОПУ, вместе с тем, возникает необходимость введения не менее двух буферных регистров БР1. БР2. и длительность операции возрастает

до трех тактов (рис. 7.6, б):

Рис, 7.5. Двухмагистральное ОПУ: а — структура; б — микропрограмма сложения

Рис. 7.6. Одномагистральное ОПУ: а — структура; б — микропрограмма сложения

- Такт 1: загрузка БР1 одним из операндов.

- Такт 2: загрузка БР2 вторым операндом.

- Такт З: выполнение микрооперации в ОГЩ над содержимым БР1 и БР2; запись

результата в один из РОН.

Организация узла рон магистрального операционного устройства

Количество регистров в узле РОН магистрального ОПУ обычно превышает тот

минимум, который необходим для реализации универсальной системы операций.

Избыток регистров используется:

- для хранения составных частей адреса (индекса, базы);

- в качестве буферной, сверхоперативной памяти для повышения производительности ВМ за счет уменьшения требуемых пересылок между основной памятью и ОПУ.

Количество регистров колеблется в среднем от 8 до 16, иногда может достигав

32-64. В процессорах с сокращенным набором команд количество РОИ доходит до нескольких сотен. 1

Организация узла РОН может обеспечивать одноканальный или двухканальный доступ как по входу (записи), так и по выходу (считыванию). В первом случае

В входу узла подключается один демультиплексор, а к выходу — один мультиплек-

сор. Во втором случае доступ осуществляется с помощью двух демулътиплексоров

и (или) двух мультиплексоров. Двухканальный доступ повышает быстродействие

0ПУ- так как позволяет обратиться параллельно к двум регистрам.