- •Глава 7.

- •Операционные устройства вычислительных машин

- •Структуры операционных устройств

- •Операционные устройства с жесткой структурой

- •Операционные устройства с магистральной структурой

- •Классификация операционных устройств с магистральной структурой

- •Организация узла рон магистрального операционного устройства

- •Организация операционного блока магистрального операционного устройства

- •Базис целочисленных операционных устройств

- •Сложение и вычитание

- •Целочисленное умножение

- •2N битов. Таким образом, алгоритм умножения предполагает последовательное

- •Алгоритм сдвига влево

- •Умножение чисел со знаком

- •Умножение целых чисел и правильных дробей

- •Модифицированный алгоритм Бута

- •Обработка двух разрядов множителя за шаг

- •Аппаратные методы ускорения умножения

- •Матричное умножение чисел без знака

- •1 Полусумматоры называется одноразрядное суммирующее устройство, имеющее дна входа для слагаемыx и два входа и два выхода — выход бита суммы и выход бита переноса.

- •Матричное умножение чисел в дополнительном коде

- •Алгоритм Бо-Вули

- •Алгоритм Пезариса

- •Древовидные умножители

- •Сравнительная оценка схем умножения с матричной и древообразной структурой

- •Конвейеризация параллельных умножителей

- •Рекурсивная декомпозиция операции умножения

- •Целочисленное деление

- •Деление с восстановлением остатка

- •Деление без восстановления остатка

- •Деление чисел со знаком

- •Устройство деления

- •Ускорение целочисленного деления

- •Замена деления умножением на обратную величину

- •XiD). Количество итераций определяется требуемой точностью вычисления X/d. Реализация метода для n-разрядных чисел требует 2 int(log2n) - 1 операций умножения.

- •Ускорение вычисления частичных остатков

- •Алгоритм srt

- •Деление в избыточных системах счисления

- •Операционные устройства с плавающей запятой

- •Подготовительный этап

- •Заключительный этап

- •Сложение и вычитание

- •Умножение

- •Деление

- •Реализация логических операций

- •Контрольные вопросы

Матричное умножение чисел без знака

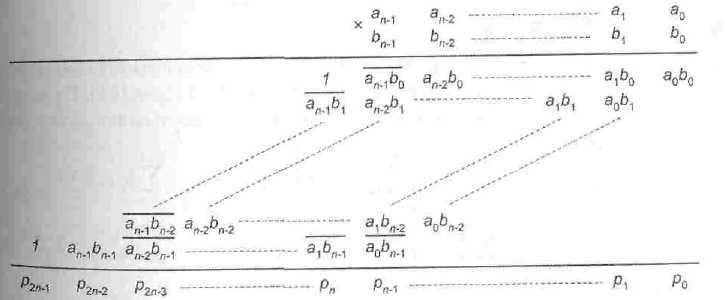

Результат Р перемножения двух n-разрядных двоичных целых чисел А и В без знака можно описать выражением

![]()

Умножение сводится к параллельному формированию битов из п n-разрядных частичных произведений с последующим их суммированием с помощью матрицы сумматоров, структура которой соответствует приведенной матрице умножения. Схема известна как умножитель Брауна. На рис. 7.28 показан такой умножитель для четырехразрядных двоичных чисел, в котором каждому столбцу в матрице умножения соответствует диагональ умножителя. Биты частичных произведений (ЧП) вида aibj формируются с помощью элементов «И». Для суммирования ЧП Применяются два вида одноразрядных сумматоров с сохранением переноса: полусумматоры (ПС)1 и полные сумматоры (СМ).

----------------------------

1 Полусумматоры называется одноразрядное суммирующее устройство, имеющее дна входа для слагаемыx и два входа и два выхода — выход бита суммы и выход бита переноса.

Рис. 7.28. Матричный умножитель Брауна для четырехразрядных чисел без знака

Матричный умножитель п х п содержит пг схем «И», ПС и (п2 - 2п) СМ.Если принять, что для реализации полусумматора требуются два логических элемента, а для полного сумматора — пять, то общее количество логических элементов в умножителе составляет п2 + 2п + 5(п2 - 2л) = 6п2 – 8n.

Быстродействие умножителя определяется наиболее глинным маршрутом распространения сигнала, который в худшем случае (пунктирная линия на рис. 7.28) включает в себя прохождение одной схемы «И», двух ПС и (2п - 4) СМ. Полагая задержки в схеме «И» и полусумматоре равными Л, а в полном сумматоре — 2Д. общую задержку в умножителе можно оценить выражением {4n - 5)Д. Чтобы сократить ее длительность, n-разрядный сумматор с последовательным переносом в нижней строке умножителя можно заменить более быстрым вариантом сумматора. Последнее, однако, не всегда желательно, поскольку это увеличивает число используемых в умножителе логических элементов и ухудшает регулярность схемы.

В общем случае задержка в матричных умножителях пропорциональна их разрядности: 0(п).

Матричное умножение чисел в дополнительном коде

К сожалению, умножитель Брауна годится только для перемножения чисел знака. При обработке знаковых чисел отрицательные представляются дополнительным кодом, а матричные умножителя строятся по схемам, отличным от схемы Брауна. Прежде всего, напомним, что запись двоичного тела в дополнительном коде (с дополнением до 2) имеет вид '£"

![]()

член правого выражения представляет знак числа, а сумма — его модуь.

Исходя из приведенной записи, произведение Р двух n-разрядных двоичных целых чисел А и В в дополнительном коде (значение произведения и сомножителей в дополнительном коде обозначим соответственно V(P), V{A) и V(B)) можно

Матрица умножения чисел со знаком, представленных в дополнительном коде, похожа на матрицу перемножения чисел без знаков (рис. 7.29). Отличие состоит в том, что (2n - 2) частичных произведений инвертированы, а в столбцы п и (2n - 1) добавлены единицы.

Рис. 7.29. Матрица перемножения n-раэрядных чисел а дополнительном кода

Соответствующая схема матричного умножителя для четырёхразрядных чисел показана на рис. 7.30.

Здесь (2n - 2) частичных произведений инвертированы за счет замены элемента «И» на элементы «И-НЕ». Сумматор в младшем разряде нижнего ряда складывает 1 в столбце n с вектором сумм и переносов из предшествующей строки, реализуя при этом следующие выражения:

![]()

Инвертор в нижней строке слева обеспечивает добавление единицы, в столбец (2n-1).

Рис. 7.30. Матричный умножитель для четырехразрядных чисел в дополнительном коде