Книги / Книга Проектирование ВПОВС (часть 2)

.pdf

В связи с этим все множество команд системы тоже организуется с сохранением этой иерархии. Все команды асинхронной интегродифферен-

цирующей системы разбиты на четыре группы (уровни) {A1, А2, A3, A4}.

Подмножество команд A1 включает в себя команды, требующие для своего наполнения только один операционный узел процессорного элемента. К

этой группе относятся арифметические и логические команды, команды переходов, команды переходов и синхронизации вычислительного процесса

(опрос и установка семафоров, передача данных) и т. д. В дальнейшем команды, относящиеся к множеству команд A1, будем называть операциями.

Подмножество команд А2 включает в себя команды, требующие для своего выполнения все операционные узлы процессорного элемента. К ним относятся команды обобщенного интегрирования, интегрирования,

дифференцирования, а также команды вычисления элементарных функций.

Высокая скорость исполнения этих команд достигается за счет совмещения работы операционных узлов ПЭ. В дальнейшем команды условия А2 будем называть макрооперации. Подмножество команд A3 включает в себя команды,

требующие для своего исполнения части или всех ПЭ процессорного модуля.

Это команда типа перемножения и сложения матриц, формирования матриц поворота вектора, матричное интегрирование, Лапласиан, ротор, волновое уравнение, уравнение теплопроводности и некоторые другие математические операции и уравнения математической физики. Кроме того, для организации микропрограммного управления часто повторяющихся последовательностей команд (процедур) используется оперативное запоминающее устройство микрокоманд. Загрузка его происходит одновременно с загрузкой программ.

Подготовка микропрограммы макрооперации осуществляется автоматически специальной программой, входящей в состав программы транслятора.

Макрооперация оформляется как обычная процедура на языке Ассемблер. В

качестве кода операции используется имя процедуры. Примером такой процедуры может служить процедура численного интегрирования системы третьего или шестого порядка -,,С_ИНТЕГР(6)», где С – символ, указывающий

342

на то, что процедура оформляется или оформлена в виде микропрограммы. В

дальнейшем процедуры, оформленные в виде микропрограммы, будем называть М-процедурами.

Группа команд А4 включает в себя команды, которые требуют для своего выполнения все множество узловых процессоров. Как правило, в эту группу входят команды интегрирования уравнений или систем уравнений математической физики. Команда из группы А4 относится к уровню задач,

поэтому она поступает не из памяти программ узловых процессоров, а по шине занесения начальных данных и программ всех узловых процессоров одновременно и записывается во все ПЭ узловых процессоров. Механизм работы с памятью программ ЦУУ узловых процессоров блокируется. Число микропрограмм, относящихся к одной команде, зависит от числа формул численного интегрирования, закладываемых для решения данной задачи.

Общая схема решения базируется на обобщенной системе Шеннона в сочетании с методом сканирования по пространству. Система уравнений узловой точки распределяется по ПЭ, микропрограммы устройства управления которых ориентированы на реализацию своего уравнения. Распределение осуществляется заранее и поэтому, если команда из А4 появляется в теле более общей программы, то происходит прерывание во всех узловых процессорах,

где эта команда появилась. Обслуживается прерывание стандартным образом.

Содержимое всех регистров ПЭ запоминается в системной области памяти,

начальный адрес которой хранится в специальном регистре индексного арифметического устройства (ИАУ). Число уровней прерывания равно 1, т. е.

любое прерывание маскирует все остальные, включая и прерывание от схем контроля. При возникновении сигнала неисправности, решение прекращается без его анализа. Синхронизация работы ПЭ и УП осуществляется в асинхронных системах с помощью известного [187] метода семафоров. В

каждый регистр связи вводится специальный блок – блок оповещения.

Назначение блока заключается в управлении записью и считыванием информации, а также организации сообщений в устройство управления о

343

возможности работы с данным регистром связи. Как предлагается в работе

[187], каждый блок оповещения содержит два семафорных примитива V и Р.

Состояние V = 0 указывает, что изменение состояния регистра связи запрещено, состояние V= 1 допускает изменение состояния. Семафор Р управляет режимом считывание Р = 1 и записью Р = 0. Управление семафорами Р осуществляется как со стороны внешних абонентов, так и со стороны внутреннего УУ. Внутренние обращения стремятся уменьшить

состояние семафора Р, т.е. перед каждым обращением осуществляется

операция Р:= Р – 1. Если P > 0, то операция обращения разрешена, если |

P 0 |

|

– запрещена, устройство управления блокируется. Перед записью информации

: |

P P |

внешним источником осуществляется операция P =P+1. Если |

max , то |

запись запрещается и ПЭ, осуществляющий запись, блокируется. Указанные операции осуществляются в том случае, когда V=1. Нетрудно увидеть, что состояние примитивов V = 0 , P = 0 делает ПЭ нерабочим. Действительно, при обращении внутреннее устройство блокируется по P = 0, а внешнее не имеет права изменять состояние Р, так как V = 0. В результате блокировка УУ не снимается и ПЭ отключается.

Состояние V = 0, p = 1 означает, что считывание информации допускается, а запись внешним источником запрещена. Семафор V всегда однобитовый, а величина p зависит от количества ячеек памяти (регистров),

отводимых одному направлению. В этом случае p суть счетчик i и

|

|

i 0, |

1, |

если |

|

P(i) |

если |

i 0, |

0, |

||

|

|

|

где i – значение счетчика, максимальное значение которого равно количеству ячеек памяти.

Механизм семафоров позволяет не только достаточно эффективно осуществлять синхронизацию процессов, но и расширить методы решения задач. Например, с помощью семафоров легко реализуется метод верхней релаксации. В этом методе переменные, вычисляемые в «младших» УП, по

344

отношению к рассматриваемому, берутся из текущего шага, а переменные,

вычисляемые в старших УП, – из предыдущего шага.

Для текущего JK – 20 УП младшим считается УП, у которого при J = j,

K > k или при K = k, J > j. В тех случаях, когда J = j, K < k или K = k, J < j, УП с номером JK является младшим.

Таким образом, установив в приемных регистрах со стороны младших УП значение семафорных примитивов V = 1, p = 0 а со стороны старших ПЭ –

V = 1, p = 1, получим следующий порядок начала работы УП. В начальный момент все УП начинают работу, но, обратившись к регистрам связи, все ПЭ блокируются, кроме элемента с номером II, так как УП с номерами 01 и 10 не существует. В приемные регистры со стороны УП с такими номерами заносятся граничные значения.

После завершения работы УП с номером II он передает информацию в УП с номерами 12 и 21. Указанные УП деблокируются и выполняют шаг интегрирования. После формирования данных и передачи в соответствующие УП начинают работу УП с номерами 11, 13, 22, 31 и т. д. Возможна реализация и метода четных – нечетных ячеек, переменных направлений и т. д.

Рассмотрим организацию выполнения команд группы A3. Для выполнения команд этой группы используются ресурсы только узлового процессора. Появление команды на выходе любой из секций программной памяти узлового процессора блокирует считыванием команд из других секций.

После окончания выполнения в ПЭ текущих команд и записи содержимого регистров общего назначения в системную область памяти (область сохранения) начинается выполнение команды. Каждый ПЭ выполняет свою часть общей микропрограммы команд. Запуск каждого ПЭ осуществляется после окончания выполнения собственной части микропрограммы независимо от того закончили или нет выполнение своей части команд другие ПЭ. Для этого на выходе «ЗП» ПЭ формируется сигнал окончания процесса, который поступает в ЦУУ. По этому сигналу коммутатор возвращается в исходное состояние (выход каждой секции ПП связан со входом своего ПЭ) и команда с

345

выхода соответствующей секции поступает на вход ПЭ. По мере окончания работы ПЭ аналогично происходит их запуск на другие команды. Если при этом вновь встречается команда из группы A3, то запуск новых команд в ПЭ,

окончивших работу, не происходит. Коммутатор переходит в состояние «один вход на все выходы» и ПЭ запускаются на выполнение своих частей микропрограммы. Синхронизация процесса обработки в процессорных элементах осуществляется с помощью синхронизирующих примитивов. При этом для ПЭ, существенно опередившего по времени остальные ПЭ, возможна блокировка по следующим причинам.

–Блокировка по отсутствию данных. Для выполнения операции в рассматриваемом ПЭ необходимы данные, вырабатываемые в других ПЭ. При обращении к PC соответствующие данные отсутствуют и процесс останавливается. Блокировка не устранима, процесс может начаться только при получении данных.

–Блокировка по невозможности записи. Процесс в рассматриваемом ПЭ останавливается в связи с невозможностью передачи данного в другой ПЭ, так как его PC занят неиспользованной предыдущей информацией. Блокировка устранима при буферной памяти связи достаточного объема.

Для разработанных процедур оказывается достаточным объем памяти –

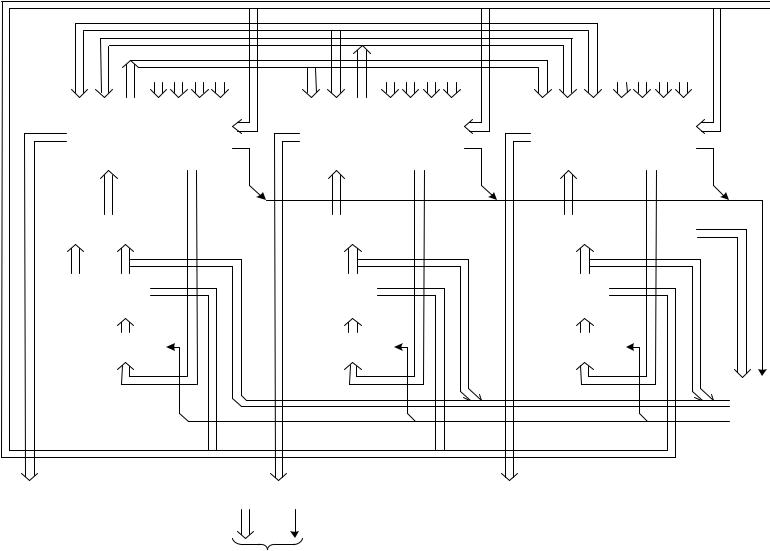

4 слова. Организация выполнения команд группы А2 и A1. Команда множества А1 и А2 выполняются в ПЭ. Отличие выполнения команд группы А2 от команд группы A1 заключается в том, что при выполнении макроопераций участвуют все операционные блоки ПЭ, а команд группы А1 только один операционный блок. Поэтому рассмотрим основные принципы выполнения команд множества А1. Схема ПЭ изображена на рис. 5.33. Он содержит четыре уровня обработки.

На первом уровне происходит формирование адреса команда, на втором – формирование адресов операндов, на третьем и четвертом уровнях организуется работа с памятью, а на пятом – выполнение команд в операционном блоке. Каждый уровень независим и, следовательно, допускается совмещение работы каждого уровня. На рис. 5.34 приведена циклограмма

346

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1.Демидович Б. П., Марон Б. П., Шувалов Э. З. Численные методы анализа.

– М.: Государственное издательство физико-математической литературы,

1962.

2.Шендеров Е. Л. Волновые задачи гидроакустики. – Л.: Судостроение, 1972.

3.Шибанов В. С., Греков В. В. Новые телекоммуникационные технологии. Телекоммуникационные технологии. Вып. 1, 1995.

4.Мартин Дж. Вычислительные сети и распределённая обработка данных. Пер с англ. /Под ред. Штаркмана В. С. – М.: Финансы и статистика. 1985.

5.Максимов М. М. О современных методах решения краевых задач. Электронное моделирование. №2, 1985.

6.Азиз Х., Сеттари Э.. Математическое моделирование пластовых систем

– М.: Недра, 1982.

7.Максимов М. М., Катков А. Ф., Романцев В. П., Щербаков Б. Д. Аналого-

цифровой вычислительный комплекс, ориентированный на решение двухмерных задач разработки нефтяного месторождения. Электронное моделирование. – Т. 2. – № 2. – 1987.

8.Мартин Дж. Системный анализ передачи данных. Т. 2. – М.: Мир, 1975.

9.Компьютеры на СБИС : В 2-х книгах / Пер. с япон. Моотока и др. – М.: Мир, 1988.

10.Василенко В. А. Сплайн-функции: теория, алгоритмы, программы. Новосибирск: Наука, 1983.

11.Эндерле Г. и др. Программные средства машинной графики. Международный стандарт GKS: Пер. с англ. / Г.Эндерле, К.Кэнси, Г.Пфафф. – М.: Радио и связь, 1988.

12.Уилтон Р. Видеосистемы персональных компьютеров IBM PC и PS/2.

Руководство по программированию: Пер. с англ. / Под ред. Григорьева В.Л. – М.: Радио и связь, 1994.

13.Де Бор К. Практическое руководство по сплайнам: Пер. с англ. – М.: Радио и связь, 1985.

350

КОП адреса

КОП адреса  ЗП

ЗП