МИНИСТЕРСТВО ОБРАЗОВАНИЯ И НАУКИ РОССИЙСКОЙ ФЕДЕРАЦИИ

ФГАОУ «ЮЖНЫЙ ФЕДЕРАЛЬНЫЙ УНИВЕРСИТЕТ»

ИНЖЕНЕРНО-ТЕНОЛОГИЧЕСКАЯ АКАДЕМИЯ

ИНСТИТУТ НАНОТЕХНОЛОГИЙ, ЭЛЕКТРОНИКИ И ПРИБОРОСТРОЕНИЯ

КАФЕДРА КОНСТРУИРОВАНИЯ ЭЛЕКТРОННЫХ СРЕДСТВ

Пояснительная записка к курсовому проекту на тему

«Разработка топологии шестиразрядного параллельного регистра»

По курсу «Микроэлектроника»

Выполнил студент гр. ЭПбо4-4

Улибегов П.И.

Проверил: к.т.н., ассистент

Денисенко М.А.

Таганрог 2015

Введение

-

Анализ технического задания

-

Разработка топологии шестиразрядного параллельного регистра

-

Проверка выполнения правил проектирования топологии и требований технического задания

Заключение

Список литературы

Введение

Современный уровень развития электроники характеризуется широким использованием интегральных и микроэлектромеханических устройств для решения различных научных и технических задач.

Интегральная схема (ИС) представляет собой законченное микроэлектронное устройство, состоящее из совокупности микроминиатюрных электрических элементов (транзисторов, резисторов, конденсаторов и т.д.) и межсоединений, изготовленное в едином технологическом цикле на общей несущей конструкции (подложке) и выполнящее определенные функции преобразования информации. Наибольшее распространение в настоящее время получили полупроводниковых ИС, все элементы и межсоединения которых изготавливаются в объеме или на поверхности полупроводникового кристалла. В качестве основного материала для производства подложек современных микросхем используется монокристаллический кремний.

Наиболее перспективной технологией изготовления широкого класса логических ИС, в том числе микропроцессоров и микроконтроллеров, является технология микросхем на основе комплементарных структур «металл-окисел-полупроводник» (КМОП-технология). Основными элементов и высокое быстродействие схем на ее основе.

С точки зрения метода проектирования ИС можно разделить на заказные и полузаказные.

Заказные микросхемы разрабатываются для решения конкретных задач в составе определенных электронных приборов.

Полностью заказные ИС характеризуются специализацией на всех этапах проектирования. Топология элементов данного типа микросхем разрабатываются на уровне отдельных транзисторов. Подобный подход позволяет оптимизировать размеры ИС и их электрические параметры, а также обеспечить высокие надежность и быстродействие.

Заказные микросхемы на основе библиотечных элементов проектируются на заказ на всех этапах, кроме синтеза топологии и структуры элементов. Подобный подход подразумевает использование заранее разработанных и проверенных конструкций компонентов различных уровней конструктивной иерархии из библиотечного набора, хранящегося в базе данных используемой системы автоматизированного проектирование и его стоимости при сохранении высокой специализации ИС.

Полузаказные микросхемы могут быть реализованы на основе базовых матричных кристаллов (БМК) и программируемых логических интегральных схем (ПЛИС). В обоих случаях проектирование ведется на основе заготовок, в которых сформированы элементы различных уровней конструктивной проектируют систему соединений готовых элементов, при реализации характеризуется неоптимальный топологии и структуры разрабатываемого устройства и его низким быстродействием, однако позволяет минимизировать материальные и временные затраты на проектирование.

В данной работе будет рассмотрен процесс разработки топологии шестиразрядного параллельного регистра на основе библиотечных элементов в САПР Microwind. Данная программа представляет собой интегральную среду разработки топологии функциональных блоков ИС и включает кремниевый компилятор языка описания электронной аппаратуры Verilog, подсистему схемотехнического производства САПР Microwind включает библиотеку стандартных цифровых и аналоговых элементов ИС различных уровней конструктивной иерархии, которые могут быть использованы при создании более сложных функциональных блоков.

Использование языков описания аппаратуры Verilog и VHDL позволяет упростить процесс разработки топологии ИС. Компилятор языка Verilog, встроенный в САПР Micriwind, имеет ограниченный набор функций. Его характерной особенностью является отсутствие возможности компилировать проекты, включающие несколько иерархических модулей. Этим обусловлена невозможность полного описания какого-либо интегрального устройства с помощью языка Verilog.

При проектировании конвейерного сумматора целесообразно использовать кремниевый компилятор САПР для описания набора одноразрядного регистра и D-триггеров. Соединения между данными элементами могут быть выполнены вручную с помощью графического редактора топологий программы Microwind. Подобный подход несколько увеличивает трудоемкость разработки топологии ИС, однако позволяет наиболее оптимально использовать площадь подложки и уменьшить связей между элементами.

Таким образом, цель данной работы – разработка топологии шестиразрядного параллельного регистра, удовлетворяющего требованиям технического задания (ТЗ), с использованием программы Microeind. Для этого необходимо решить следующие задачи:

- проанализировать структурную схему разрабатываемого устройства;

- произвести компиляцию элементов узла ИС с помощью средств САПР;

- убедиться в работоспособности каждого из полученных элементов;

- произвести последовательную разработку элементов более высоких уровней конструктивной иерархии путем ручной трассировки меллических соединений между библиотечными элементами;

- выполнить проверку выполнения правил проектирования топологии;

- произвести электрическое моделирование топологии шестиразрядного параллельного регистра;

- сделать вывод о соответствии разработанного функционального узла требованиям ТЗ.

Рассмотри каждый из этапов проектирования топологии шестиразрядного параллельного регистра более подробно.

-

Анализ технического задания

Требования, предъявляемые к конструкции шестиразрядного параллельного регистра в ТЗ, можно представить следующим образом:

- КМОП-технология изготовления ИС;

- минимальный топологический размер – 60 нм;

- отношение ширины к длине канала транзисторов с электронной проводимостью – 4;

- отношение ширины к длине канала транзисторов с дырочной проводимостью – 8;

- максимально допустимая площадь топологии – 120 000 мкм2;

- максимально допустимое количество слоев металлизации – 3.

Структурная схема проектируемого устройства с учетом требуемых разрядностей входных, выходных и внутренних сигналов представлена на рисунке 1.

Рисунок 1 – Структурная схема шестиразрядного параллельного регистра [1]

Конвейерный

схемы представляют собой цифровые

устройства, содержащие определенное

количество отделенных друг от друга

параллельными регистрами последовательных

ступеней, в пределах каждой из которых

обработка данных осуществляется

параллельно. Все регистры конвейера

управляются общими сигналами синхронизации

и сброса. Если конвейерная схема содержит

n

ступеней, каждая из которых характеризуется

одинаковой задержкой

,

то максимальный период тактовых импульсов

без использования конвейера составит

,

то максимальный период тактовых импульсов

без использования конвейера составит

,

а с использованием конвейерной архитектуры

-

,

а с использованием конвейерной архитектуры

-

.

Типичным примером схемы с конвейерной

структурой может служить конвейерный

сумматор.

.

Типичным примером схемы с конвейерной

структурой может служить конвейерный

сумматор.

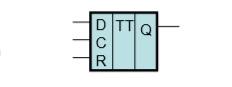

D-триггер представляет собой последовательностное логическое устройство, имеющее один информационный вход D, выход Q, а также входы сброса R (Reset) и синхронизации C (Clock). На рисунке 2 представлено обозначение данного элемента.

Рисунок 2 – Обозначение D-триггера [1]

В таблице 1 представлена таблица истинности D-триггера. При подаче на вход R активного уровня логической единицы на выходе Q устанавливается уровень логического нуля вне зависимости от текущих состояний на входах D и C. Подобное состояние триггера называется начальным. Если на входе R установлен логический ноль, то на выходе Q храниться текущее состояние (‘0’ или ‘1’) до тех пор, пока на вход С не поступит активный фронт импульса. При поступлении активного фронта синхроимпульса и действующем значении на входе D записывается в триггер и поступает на выход Q. В качестве активного фронта могут использоваться передний или задний фронты импульсного сигнала синхронизации.

Таблица 1 – Таблица истинности D-триггера

|

D |

C |

R |

Q |

|

* |

* |

1 |

0 |

|

0 |

Фронт |

0 |

0 |

|

1 |

Фронт |

0 |

1 |

|

* |

0 |

0 |

Qn-1 |

|

* |

1 |

0 |

Qn-1 |

Электрическая принципиальная схема D-триггера на основе КМОП-транзисторов представлена на рисунке 3.

Параллельный регистр представляет собой последовательное устройство, состоящее из определяемого разрядностью количества D-триггеров с параллельно соединенными входами синхронизации С и сброса R. Запись и считывание информации в подобном регистре, происходит одновременно на все входы и со всех выходов. При подаче на вход параллельного регистра многоразрядного двоичного числа происходит его задержка на один такт синхроимпульса С. Данное свойство регистра используется в конвейерном сумматоре для обеспечения одновременного поступления разрядов слагаемых на входы сумматоров и разрядов суммы на выход устройства

.

Рисунок 3 – Электрическая принципиальная схема D-триггера на основе КМОП-транзисторов[1]

Таким образом, основные элементы разрабатываемого шестиразрядного параллельного регистра могут быть сформированы на основе достаточно простых логических блоков.

Выполнение требований ТЗ может быть осуществлено следующим образом.

Для задания минимальных топологических размеров и основных правил проектирования в программе Micriwind необходимо подключить соответствующий файл с помощью команды (File – Select Foundry). КМОП-технологии с минимальным топологическим размером 60 нм соответствует файл cmos012.rul. На каждом из этапов проектирования шестиразрядного параллельного регистра необходимо производить проверку топологии на соответствие установленным требованиям с помощью команды (Analysis – Design Rule Checker). В случае нарушения какого-либо правил программа автоматически укажет место и характер допущенной ошибки.

Значения длины и ширины проводящих каналов МОП-транзисторов могут быть заданы при использовании кремниевого компиляторов программы Microwind в соответствующих пунктах меню параметров компиляции. Проверку соответствия полученных топологий условиям ТЗ можно произвести с помощью функции Measure distance.

Таким образом, использование специализированных функций САПР Microwind позволяет добиться соответствия разрабатываемого шестиразрядного параллельного регистра требованиям ТЗ.