- •Часть 1. Элементы схемотехники.

- •8. Методика синтеза комбинационных схем

- •9. Расчет электронных схем

- •10. Исследования элементов и схем электронных устройств

- •11. Учебное проектирование функциональных узлов и устройств

- •Предисловие

- •1. Пассивные компоненты электронных устройств

- •2. Полупроводниковые диоды

- •3. Биполярные транзисторы

- •4. Полевые транзисторы

- •5. Базовые логические элементы

- •5.2. Основные логические элементы.

- •5.3. Электронные ключи.

- •6. Триггеры

- •8. Методика синтеза комбинационных схем

- •Список литературы

5.3. Электронные ключи.

Общие сведения. Электронный ключ — это устройство, которое может находиться в одном из двух устойчивых состояний: замкнутом или разомкнутом. Переход из одного состояния в другое в идеальном электронном ключе происходит скачком под влиянием управляющего напряжения или тока.

В реальных электронных ключах переход из открытого состояния в закрытое и наоборот происходит не мгновенно, а в течение некоторого времени. Это время определяется инерционностью активного нелинейного элемента и наличием в ключе паразитных емкостей и индуктивностей.

В современной электронной технике наибольшее применение находят транзисторные ключи.

Ключи на биполярных транзисторах. Простейшая схема транзисторного ключа (рис. 5.2, а) подобна схеме транзисторного усилителя, однако она отличается режимом работы транзистора. При работе в ключевом режиме рабочая точка транзистора может находиться только в двух положениях: в области отсечки (транзистор закрыт) и в области насыщения (транзистор открыт и насыщен). Такие ключи называют насыщенными транзисторными ключами. Иногда применяются ключи, в которых рабочая точка при открытом транзисторе находится в активной области (обычно вблизи области насыщения, но не достигает ее). Такие ключи называют ненасыщенными. Чаще применяются транзисторные насыщенные ключи, так как у них в состоянии «Включено» выходное напряжение имеет более низкий уровень и отличается большей стабильностью.

Рис. 5.2. Схемы транзисторного ключа (а) и характеристики (б),иллюстрирующие изменения режима при переходе ключа из закрытого состояния {точка А) в открытое (точка В)

Для

обеспечения режима отсечки на вход

ключа необходимо подать отрицательное

напряжение

![]() (или положительное дляp-n-p-транзистора).

(или положительное дляp-n-p-транзистора).

Для

надежного запирания транзистора

абсолютное значение отрицательного

напряжения

![]() должно быть не менее некоторого значения

порогового напряжения

должно быть не менее некоторого значения

порогового напряжения![]() ,

и условие для обеспечения режима отсечки

имеет вид

,

и условие для обеспечения режима отсечки

имеет вид

![]()

Для

перехода транзистора в режим насыщения

на вход ключа необходимо подать такое

положительное напряжение

![]() ,

при котором в цепи базы создается ток

,

при котором в цепи базы создается ток

![]()

где

![]() — ток базы на границе между активным

режимом и режимом насыщения (точка В на

рис. 5.2, б).

— ток базы на границе между активным

режимом и режимом насыщения (точка В на

рис. 5.2, б).

Ток коллектора в режиме насыщения

![]() .

.

В

режиме насыщения коллекторное напряжение

![]() остается положительным по отношению к

эмиттеру, но имеет очень малое значение

(десятые доли вольта для германиевых

транзисторов и 1...1,5 В для кремниевых).

Поэтому напряжение на коллекторном ЭДП

оказывается отрицательным:

остается положительным по отношению к

эмиттеру, но имеет очень малое значение

(десятые доли вольта для германиевых

транзисторов и 1...1,5 В для кремниевых).

Поэтому напряжение на коллекторном ЭДП

оказывается отрицательным:

![]() ,

,

и он включается в прямом направлении.

Быстродействие электронного ключа зависит от времени включения и выключения.

Время включения определяется временем задержки, обусловленным инерционностью диффузионного движения неосновных носителей заряда в базе БТ, и временем формирования фронта (временем установления) выходного напряжения. Время выключения складывается из времени рассасывания накопленных в базе неосновных носителей заряда и времени формирования среза выходного напряжения.

Увеличению быстродействия транзисторного ключа способствуют применение высокочастотных транзисторов, увеличение отпирающего и обратного токов базы, а также уменьшение тока базы в режиме насыщения.

Для уменьшения тока базы в режиме насыщения применяют ненасыщенные ключи, в которых между базой и коллектором включают диод Шоттки (рис. 5.3). Диод Шоттки имеет напряжение отпирания на 0,1...0,2 В меньше, чем напряжение насыщения коллекторного перехода, поэтому он открывается до наступления режима насыщения, и часть тока базы через открытый диод проходит в коллекторную цепь транзистора, предотвращая тем самым накопление в базе заряда неосновных носителей. Ненасыщенные ключи с диодом Шоттки широко применяются в ИМС. Это связано с тем, что изготовление диодов Шоттки на основе транзисторной структуры с помощью интегральной технологии не требует никаких дополнительных операций и не приводит к увеличению площади кристалла, занимаемой элементами ключа.

Рис. 5.3. Схема ключа с диодом Шоттки

Ключи

на МДП-транзисторах.

В ключах на полевых транзисторах (рис.

5.4) отсутствует такой недостаток, как

накопление и рассасывание неосновных

носителей, поэтому время переключения

определяется зарядкой и перезарядкой

междуэлектродных емкостей. Роль резистора

![]() могут выполнять полевые транзисторы.

Это значительно облегчает технологию

производства интегральных ключей на

полевых транзисторах.

могут выполнять полевые транзисторы.

Это значительно облегчает технологию

производства интегральных ключей на

полевых транзисторах.

Рис. 5.4. Схемы электронных ключей на ПТ с p-n-затвором (а) и МДП-типа (б).

В

ключах на МДП-транзисторах с индуцированным

каналом (рис, 5.5) роль резистора

![]() выполняют транзисторы VТ1,

а роль активного элемента — транзисторы

VТ2.

Транзисторы VТ2

имеют канал p-типа,

а транзисторы VT1

— канал n-типа

(рис. 5.5, а) или n-типа

(рис. 5.5, б). Их передаточные характеристики

показаны на рис. 5.6, а

и 5.6, б

соответственно. Графики напряжений,

поясняющие работу ключей, представлены

на рис. 5.7.

выполняют транзисторы VТ1,

а роль активного элемента — транзисторы

VТ2.

Транзисторы VТ2

имеют канал p-типа,

а транзисторы VT1

— канал n-типа

(рис. 5.5, а) или n-типа

(рис. 5.5, б). Их передаточные характеристики

показаны на рис. 5.6, а

и 5.6, б

соответственно. Графики напряжений,

поясняющие работу ключей, представлены

на рис. 5.7.

Рис. 5.5. Схемы электронных ключей на МДП-транзисторах с индуцированными каналами одинакового (а) и противоположного (б) типов электропроводности

Рис. 5.6. Передаточные характеристики МДП-транзисторов с индуцированными каналами различного типа электропроводности

Рис. 5.7. Графики изменений входного (а) и выходного (б) напряжений электронных ключей на МДП-транзисторах

При

подаче на вход положительного напряжения

![]() транзисторы VТ2,

имеющие канал p-типа,

закрываются. Транзистор

VТ1

первого ключа (рис. 5.5, а) открыт вследствие

поданного на его затвор отрицательного

напряжения смещения

транзисторы VТ2,

имеющие канал p-типа,

закрываются. Транзистор

VТ1

первого ключа (рис. 5.5, а) открыт вследствие

поданного на его затвор отрицательного

напряжения смещения

![]() .

ТранзисторVТ1

второго ключа, имеющий канал n-типа

(рис. 5.5, б), также оказывается открытым,

так как его затвор соединен со входом,

на котором действует положительное

напряжение

.

ТранзисторVТ1

второго ключа, имеющий канал n-типа

(рис. 5.5, б), также оказывается открытым,

так как его затвор соединен со входом,

на котором действует положительное

напряжение

![]() .

Сопротивления открытых транзисторовVT1

малы по сравнению с сопротивлением

закрытых транзисторов VT2,

и

.

Сопротивления открытых транзисторовVT1

малы по сравнению с сопротивлением

закрытых транзисторов VT2,

и

![]() .

.

При

поступлении на вход ключей отрицательного

напряжения

![]() транзисторыVT2

открываются, а транзисторы VT1

закрываются. Почти все напряжение

транзисторыVT2

открываются, а транзисторы VT1

закрываются. Почти все напряжение

![]() падает на большом сопротивлении канала

транзистораVT1,

и

падает на большом сопротивлении канала

транзистораVT1,

и

![]() .

.

5.4. Базовые логические элементы на биполярных структурах. В зависимости от компонентов, которые используются при построении ЛЭ, и способа соединения компонентов в пределах одного ЛЭ различают следующие типы ЛЭ, или типы логик:

диодно-транзисторная логика (ДТЛ);

транзисторно-транзисторная логика (ТТЛ);

эмиттерно-связанная логика (ЭСЛ);

инжекционно-интегральная логика (И2Л, ИИЛ);

логические элементы на МДП-транзисторах (КМДП).

Имеются и иные типы ЛЭ. Одни из них морально устарели и в настоящее время не применяются, другие находятся в стадии разработки.

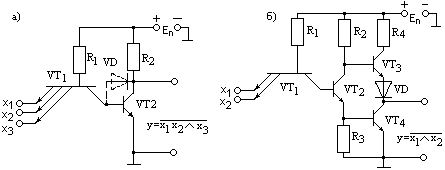

Логические элементы ТТЛ. Транзисторно-транзисторными называются такие логические элементы, во входной цепи которых используется многоэмиттерный транзистор (МЭТ). По принципу построения и работе схемы ТТЛ близки к схемам ДТЛ. Эмиттерные переходы МЭТ выполняют функцию входных диодов, а коллекторный переход — роль смещающего диода. Элементы ТТЛ компактнее, чем элементы ДТЛ, что повышает степень интеграции микросхем ТТЛ. Интегральные схемы на основе ТТЛ по сравнению с микросхемами ДТЛ имеют более высокие быстродействие, помехозащищенность и надежность, большую нагрузочную способность и меньшую потребляемую мощность.

На

рис. 5.8, а

показана схема 3И — НЕ ЛЭ ТТЛ с простым

инвертором. Если на все входы МЭТ поданы

напряжения

![]() ,

соответствующие уровню 1, то все эмиттерные

переходы МЭТVТ1

смещены в обратном направлении, а

коллекторный — в прямом. Коллекторный

ток МЭТ протекает через базу транзистора

VТ2,

который открывается и переходит в режим

насыщения. На выходе ЛЭ устанавливается

напряжение низкого уровня

,

соответствующие уровню 1, то все эмиттерные

переходы МЭТVТ1

смещены в обратном направлении, а

коллекторный — в прямом. Коллекторный

ток МЭТ протекает через базу транзистора

VТ2,

который открывается и переходит в режим

насыщения. На выходе ЛЭ устанавливается

напряжение низкого уровня

![]() .

.

Если

хотя бы на один вход МЭТ подано напряжение

![]() ,

соответствующее уровню 0, то соответствующий

эмиттерный переход МЭТ смещается в

прямом направлении. Эмиттерный ток

этого перехода протекает через резисторR1,

вследствие чего коллекторный ток МЭТ

уменьшается и транзистор VТ2

закрывается. На выходе ЛЭ устанавливается

напряжение высокого уровня

,

соответствующее уровню 0, то соответствующий

эмиттерный переход МЭТ смещается в

прямом направлении. Эмиттерный ток

этого перехода протекает через резисторR1,

вследствие чего коллекторный ток МЭТ

уменьшается и транзистор VТ2

закрывается. На выходе ЛЭ устанавливается

напряжение высокого уровня

![]() .

.

Для повышения быстродействия ЛЭ в него вводят нелинейную обратную связь, осуществляемую с помощью диода Шотки (диод VD на рис. 5.10, а). Диод Шотки VD с транзистором VТ2 в интегральном исполнении составляет единую структуру, которую иногда называют транзистором Шотки.

Рис. 5.8. Схемы логических И — НЕ ТТЛ с простым (а) и сложным (б) инверторами

На рис. 5.8, б показана схема логического элемента 2И — НЕ ТТЛ со сложным инвертором. Работа такого инвертора была рассмотрена раньше.

Особенностью сложного инвертора является инерционность процесса переключения транзисторов VТ2, VТЗ и VТ4. Поэтому быстродействие сложного инвертора хуже, чем простого. Для повышения быстродействия сложного инвертора в него вводят дополнительный транзистор, который подключается параллельно эмиттерному переходу VТ4.

В настоящее время выпускается несколько разновидностей серий микросхем с элементами ТТЛ: стандартные (серии 133; K155), высокого быстродействия (серии 130; K131), микромощные (серия 134), с диодами Шоттки (серии 530; K531) и микромощная с диодами Шоттки (серия K555). Они имеют большой процент выхода, низкую стоимость, обладают широким функциональным набором и удобны для практического использования.

Логические элементы ЭСЛ. Элементную базу эмиттерно-связанной логики составляют устройства на переключателях тока.

Простейшая схема переключателя тока показана на рис. 5.9, а.

Рис. 5.9. Упрощенная схема переключателя тока (а) и графики напряжений (б), поясняющие его работу

Суммарный

ток транзисторов VТ1

и VТ2

задается генератором тока I,

включенным в цепь эмиттеров транзисторов.

Если на вход (базу VТ1)

поступает напряжение низкого уровня

![]() (логический 0), то транзисторVТ1

закрыт и весь ток

(логический 0), то транзисторVТ1

закрыт и весь ток

![]() протекает через транзисторVТ2,

на базу которого подается опорное

напряжение

протекает через транзисторVТ2,

на базу которого подается опорное

напряжение

![]() ,

превышающее нижний уровень напряжения

базыVТ1.

,

превышающее нижний уровень напряжения

базыVТ1.

На

коллекторе закрытого транзистора VТ1

образуется напряжение высокого уровня

(логическая 1), а на коллекторе открытого

транзистора VТ2

— напряжение низкого уровня (логический

0), как показано на рис. 5.9, б.

Если

![]() ,

то транзисторVТ1

откроется. Так как

,

то транзисторVТ1

откроется. Так как

![]() ,

то транзисторVТ2

окажется закрытым и весь ток

,

то транзисторVТ2

окажется закрытым и весь ток

![]() будет протекать через транзисторVТ1.

На коллекторе VТ1

образуется напряжение низкого уровня,

а на коллекторе VТ2

— высокого.

будет протекать через транзисторVТ1.

На коллекторе VТ1

образуется напряжение низкого уровня,

а на коллекторе VТ2

— высокого.

Параметры генератора тока таковы, что транзисторы VТ1 и VТ2 не переходят в режим насыщения. Этим достигается высокое быстродействие элементов ЭСЛ.

Принципиальная схема базового логического элемента ЭСЛ показана на рис. 5.10. Этот ЛЭ одновременно выполняет две логические операции: ИЛИ — НЕ по выходу 1 и ИЛИ по выходу 2.

Рис. 5.10. Схема базового логического элемента ЭСЛ

На транзисторах VT1, VТ2 и VТЗ выполнен токовый переключатель, обеспечивающий получение логических функций ИЛИ — НЕ (на коллекторе VТ2) и ИЛИ (на коллекторе VТЗ). В качестве генератора тока используется высокоомный резистор R5, включенный в объединенную эмиттерную цепь транзисторов VТ1, VТ2 и VТЗ. Источник опорного напряжения выполнен на транзисторе VТ4 и диодах VD1 и VD2. Опорное напряжение, уровень которого находится примерно посередине между уровнями, соответствующими 0 и 1, подается на базу транзистора VТЗ, поэтому транзистор VТЗ будет закрыт, если хотя бы на один из входов подано напряжение более высокого уровня (логическая 1) и открыт, если на всех входах имеется напряжение низкого уровня (логический 0). Логическая информация с коллекторов VТ2 и VТЗ поступает на базы выходных эмиттерных повторителей, выполненных на транзисторах VТ5 и VТ6. Эмиттерные повторители служат для увеличения нагрузочной способности ЛЭ и смещения уровней выходных напряжений для совместимости ЛЭ данной серии по входу и выходу.

Представителями ЛЭ ЭСЛ являются интегральные микросхемы 500-й серии.

Достоинством ЛЭ ЭСЛ является хорошо отлаженная технология их производства, обеспечивающая достаточно высокий процент выхода годных микросхем и их сравнительно низкую стоимость. Элементы ЭСЛ имеют более высокое быстродействие по сравнению с ЛЭ ТТЛ. Благодаря этому они получили широкое распространение в быстродействующей и высокопроизводительной вычислительной технике. Дифференциальные каскады ЛЭ ЭСЛ обеспечивают высокую помехоустойчивость, стабильность динамических параметров при изменении температуры и напряжения источников питания, постоянное, не зависящее от частоты переключения, потребление тока.

Недостатком ЛЭ ЭСЛ является высокая потребляемая мощность.

Логические элементы И2Л. ЛЭ И2Л выполняются в виде цепочки транзисторов с инжекционным питанием. Отличительной особенностью таких транзисторов по сравнению с БТ является наличие дополнительного электрода — инжектора. В этой структуре можно выделить два транзистора: горизонтальный токозадающий и вертикальный переключающий, соединенные так, как показано на рис. 5.11, б. Роль электронного ключа S обычно выполняет структура БТ, включенного с ОЭ и работающего в ключевом режиме.

Рис. 5.11. Принципиальная схема инвертора с инжекционным питанием

Смещение инжекторного перехода в прямом направлении достигается подачей на инжектор p-типа положительного напряжения, равного 1...1,5 В. С помощью электронного ключа S база транзистора VТ2 может подключаться к эмиттеру этого транзистора или к генератору тока (коллектору T1). Если ключ разомкнут (при этом входное напряжение имеет высокий уровень), то почти весь ток генератора поступает в базу транзистора VТ2. Транзистор открыт и насыщен, и его выходное напряжение составляет единицы или десятки милливольт (при условии, что к коллектору подключена нагрузка). При замкнутом ключе S почти весь ток генератора тока течет через ключ и лишь незначительная его часть поступает в базу транзистора VТ2. Транзистор находится в активном режиме вблизи области отсечки. Напряжение коллектора транзистора в этом режиме соответствует высокому уровню — примерно 0,8 В.

Таким образом, транзистор с инжекционным питанием можно рассматривать как инвертор или ЛЭ, выполняющий операцию НЕ.

На рис. 5.12 показана схема ЛЭ ИЛИ — НЕ на два входа. При поступлении логических нулей на оба входа транзисторы VТ1 и VТ2 закрыты и на выходе образуется логическая 1. Если хотя бы на один из входов поступает логическая 1, то соответствующий транзистор открыт и насыщен и на выходе, являющемся объединением всех коллекторов, устанавливается логический 0.

Рис. 5.12. Упрощенная схема ЛЭ 2ИЛИ – НЕ инжекционной логики

Достоинствами ЛЭ И2Л являются высокая степень интеграции, большое быстродействие, способность работать при очень малых токах (единицы наноампер) и малых значениях питающих напряжений.

5.5. Базовые логические элементы на МДП- и КМДП-структурах. Базовым элементом логических ИМС на МДП-транзисторах является инвертор (элемент НЕ). На рис. 5.13 показаны схемы инверторов на МДП-транзисторах с каналом p-типа с одним (а) и двумя (б) источниками питания.

Рис. 5.13. Схемы инверторов на МДП-транзисторах (а, б) и графики входных и выходных напряжений (в)

Транзисторы

VT1

обеих схем имеют более узкие и длинные

каналы по сравнению с транзисторами

VТ2.

Поэтому если оба транзистора VТ1

и VТ2

открыты, то

![]() .

Если

.

Если![]() ,

т.е.

,

т.е.![]() ,

то транзисторыVТ2

оказываются открытыми. Так как при этом

,

то транзисторыVТ2

оказываются открытыми. Так как при этом

![]() ,

то напряжение на выходе близко к нулю

(рис. 5.13, в).

,

то напряжение на выходе близко к нулю

(рис. 5.13, в).

Если

![]() ,

т. е.

,

т. е.![]() ,

то транзисторыVТ2

закрываются, а транзисторы VТ1

находятся на грани запирания. При этом

,

то транзисторыVТ2

закрываются, а транзисторы VТ1

находятся на грани запирания. При этом

![]() и на выходе устанавливается напряжение

с низким отрицательным уровнем,

соответствующим логической 1.

и на выходе устанавливается напряжение

с низким отрицательным уровнем,

соответствующим логической 1.

Включение

в цепь затвора транзистора VT1

дополнительного источника напряжения

![]() повышает помехоустойчивость ЛЭ.

повышает помехоустойчивость ЛЭ.

На рис. 5.14, а показана схема двухвходового ЛЭ ИЛИ — НЕ, выполненного на комплементарных МДП-транзисторах. Параллельно соединенные транзисторы VТЗ и VТ4 с каналом n-типа являются управляющими, а транзисторы VТ1 и VТ2 с каналом p-типа — нагрузочными. Управляющие транзисторы образуют нижнее, а нагрузочные — верхнее плечо делителя, с которого снимается выходное напряжение.

Рис. 5.14. Схемы логических элементов ИЛИ — НЕ (а) и И — НЕ (б) на КМДП-транзисторах

Если

на входах

![]() и

и![]() напряжение низкого уровня:

напряжение низкого уровня:![]() ,

то транзисторыVТЗ

и VТ4

закрыты. Исток транзистора VТ1

с каналом p-типа

подключен к плюсу источника

,

то транзисторыVТЗ

и VТ4

закрыты. Исток транзистора VТ1

с каналом p-типа

подключен к плюсу источника ![]() ,

поэтому напряжение его затвора

,

поэтому напряжение его затвора ![]() и превышает по абсолютному значению

пороговое напряжение. Транзистор VТ1

открыт, сопротивление его канала мало

и напряжение истока транзистора VТ2

близко к напряжению

и превышает по абсолютному значению

пороговое напряжение. Транзистор VТ1

открыт, сопротивление его канала мало

и напряжение истока транзистора VТ2

близко к напряжению ![]() .

Следовательно, транзистор VТ2

также открыт, и сопротивление верхнего

плеча оказывается значительно меньше,

чем сопротивление нижнего плеча. На

выходе устанавливается напряжение

высокого уровня, близкое к напряжению

источника питания.

.

Следовательно, транзистор VТ2

также открыт, и сопротивление верхнего

плеча оказывается значительно меньше,

чем сопротивление нижнего плеча. На

выходе устанавливается напряжение

высокого уровня, близкое к напряжению

источника питания.

Если

хотя бы на один вход

![]() или

или![]() поступает напряжение высокого уровня,

то соответствующий транзистор нижнего

плеча открывается, а верхнего плеча —

закрывается. На выходе образуется

напряжение низкого уровня, близкое к

нулю.

поступает напряжение высокого уровня,

то соответствующий транзистор нижнего

плеча открывается, а верхнего плеча —

закрывается. На выходе образуется

напряжение низкого уровня, близкое к

нулю.

В

логических элементах И — НЕ КМДП-ТЛ

(рис. 5.14, б) управляющие МДП-транзисторы

с каналом n-типа

VТЗ

и VТ4

включены последовательно, а нагрузочные

с каналами p-типа

— параллельно. Сопротивление нижнего

плеча будет мало в том случае, если

открыты оба транзистора VТЗ

и VТ4,

т.е. когда на входах

![]() и

и![]() действуют напряжения, соответствующие

логическим единицам. При этом

действуют напряжения, соответствующие

логическим единицам. При этом![]() и соответствует логическому нулю. Если

на одном из входов будет напряжение

низкого уровня, то один из транзисторовVТ1

или VТ2

открыт, а один из транзисторов VТЗ

или VТ4

закрыт. При этом сопротивление верхнего

плеча значительно меньше, чем сопротивление

нижнего плеча, и уровень выходного

напряжения соответствует логической

единице.

и соответствует логическому нулю. Если

на одном из входов будет напряжение

низкого уровня, то один из транзисторовVТ1

или VТ2

открыт, а один из транзисторов VТЗ

или VТ4

закрыт. При этом сопротивление верхнего

плеча значительно меньше, чем сопротивление

нижнего плеча, и уровень выходного

напряжения соответствует логической

единице.

Логические

элементы КМДП-ТЛ отличаются малым

потреблением мощности (десятки нановатт),

достаточно высоким быстродействием

(до 10 МГц и более), высокими помехоустойчивостью

и коэффициентом использования напряжения

источника питания (![]() ).

Их недостатком является большая сложность

изготовления по сравнению с ЛЭ МДП-ТЛ.

).

Их недостатком является большая сложность

изготовления по сравнению с ЛЭ МДП-ТЛ.