- •Содержание

- •Введение

- •1. Основы цифровой электроники

- •1.1. Простейшие способы получения цифрового сигнала

- •1.2. Простейшие способы контроля цифровых сигналов

- •1.3. Логические переменные, базовые операции между логическими переменными

- •1.4. Числа, используемые в цифровой электронике

- •1.5. Арифметические действия над двоичными числами

- •1.6. Переполнение

- •1.7. Цифровая интегральная схема

- •1.8. Упрощение и минимизация логических функций

- •1.9 Недоопределенная функция

- •1.10. Контрольные вопросы

- •1.11. Индивидуальные задания

- •2. Логические элементы

- •2.1. Базовые логические элементы

- •2.2. Особенности работы логических элементов

- •2.2.1. Совместимость входных и выходных сигналов

- •2.2.2. Нагрузочная способность

- •2.2.3. Квантование (формирование) сигнала

- •2.2.4. Помехоустойчивость

- •2.2.5. Работоспособность в широкой области допусков и параметров

- •2.2.6. Затухание переходных процессов за время одного такта

- •2.3. Основные характеристики логических элементов

- •2.4. Основные параметры логических элементов

- •2.4.1. Динамические параметры

- •2.4.2. Статические параметры логических элементов

- •2.5. Особенности проектирования цифровых приборов

- •2.6. Входы и выходы цифровых микросхем

- •2.6.1. Входы микросхем.

- •2.6.2. Выходы микросхем

- •2.7. Контрольные вопросы

- •2.8. Индивидуальные задания

- •3. Триггеры

- •3.1.Общие сведения

- •3.1.1. Параметры триггера

- •3.2. Принцип работы асинхронного триггера

- •3.2.1. Асинхронный rs триггер

- •3.2.1. Асинхронный jk триггер

- •3.2.3. Асинхронный т триггер

- •3.3.Синхронные триггеры

- •3.3.1. Состязания в асинхронных комбинационных и последовательных схемах

- •3.3.2. Синхронный rs триггер

- •3.3.3. D триггер

- •3.4.Основные схемы включения триггеров

- •3.4.1. Подавление дребезга контактов выключателя при помощи триггера

- •3.4.2. Использование триггера в качестве флага процесса

- •3.4.3. Синхронизация с помощью триггера

- •3.4.4. Построение линий задержки с помощью триггера

- •3.5. Контрольные вопросы

- •3.6. Индивидуальные задания

- •4. Регистры

- •4.1.Общие сведения

- •4.2. Регистры хранения (памяти)

- •4.2.1. Стробируемые регистры

- •4.2.2. Тактируемые регистры

- •4.3. Регистры сдвига

- •4.4. Способы вывода информации из регистра

- •4.5. Контрольные вопросы

- •4.5. Индивидуальные задания

- •5. Счетчики

- •5.1.Общие сведения

- •5.2. Счетчики с последовательным переносом (асинхронные счетчики)

- •5.2.1. Суммирующие счетчики

- •5.2.2. Вычитающие счетчик

- •4.2.3. Увеличение разрядности асинхронных счетчиков

- •5.2.4. Применение асинхронных счетчиков

- •5.3. Счетчики с параллельным переносом (синхронные счетчики)

- •5.3.1. Синхронные счетчики с асинхронным переносом

- •5.3.2. Синхронные счетчики с синхронным переносом

- •5.4. Счетчики с произвольным коэффициентом счета

- •5.5. Контрольные вопросы

- •5.6. Индивидуальные задания

- •6. Шифраторы и дешифраторы

- •6.1.Общие сведения

- •6.2. Дешифраторы

- •6.2.1. Применение дешифраторов

- •6.3. Шифраторы

- •6.4. Контрольные вопросы

- •6.5. Индивидуальные задания

- •7. Мультиплексоры, демультиплексоры

- •7.1.Мультиплексоры

- •7.2. Демультиплексоры

- •7.3. Контрольные вопросы

- •7.4. Индивидуальные задания

- •8. Компараторы

- •8.1 Одноразрядный компаратор

- •8.2 Многоразрядный компаратор

- •8.3. Контрольные вопросы

- •8.4. Индивидуальные задания

- •9. Сумматоры

- •9.1.Общие сведения

- •9.2.Четвертьсумматор

- •9.3.Полусумматор

- •9.4. Полный одноразрядный двоичный сумматор

- •9.5. Многоразрядные сумматоры

- •9.5.1. Последовательный многоразрядный сумматор

- •9.5.2. Параллельный многоразрядный сумматор с последовательным переносом

- •9.5.3. Параллельный многоразрядный сумматор с параллельным переносом

- •9.6. Микросхемы многоразрядных сумматоров

- •9.7. Сумматоры групповой структуры

- •9.9. Контрольные вопросы

- •9.10. Индивидуальные задания

- •10. Преобразователи кодов

- •10.2. Контрольные вопросы

- •11. Одновибраторы и генераторы

- •11.1.Одновибраторы

- •11.2. Генераторы

- •11.3. Контрольные вопросы

- •12. Память

- •12.1 Общие сведения

- •12.2. Типовые структуры и функциональные узлы микросхем памяти

- •12.3. Условные графические обозначения микросхем памяти

- •12.4. Применение пзу

- •12.5. Применение озу

- •12.6 Контрольные вопросы

- •12.7. Индивидуальные задания

- •13. Цифро-аналоговые и аналого-цифровые преобразователи

- •13.1 Цифро-аналоговые преобразователи (цап)

- •13.2 Аналого-цифровые преобразователи (ацп)

- •Контрольные вопросы

- •14. Типовые ситуации при построении узлов и устройств на стандартных интегральных

- •14.1. Режимы неиспользуемых входов в логических элементах

- •14.2. Режимы неиспользуемых логических элементов

- •14.3. Наращивание числа входов логических элементов

- •14.4. Снижение нагрузок на выходах логических элементов

- •14.5. Паразитные связи цифровых элементов по цепям питания

- •14.6. Паразитные связи цифровых элементов по цепям питания

- •14.6.1.Внешние помехи

- •14.6.2.Токовые помехи

- •14.6.3. Перекрестные помехи

- •14.6.4. Искажения сигналов в несогласованных линиях

- •Последовательное согласование волновых сопротивлений

- •14.6.5. Линии передачи сигналов

- •Список литературы

2.6. Входы и выходы цифровых микросхем

Характеристики и параметры входов и выходов цифровых микросхем определяются прежде всего технологией и схемотехникой их внутреннего строения. Для разработчика цифровых устройств любая микросхема представляет собой "черный ящик", внутренности которого знать не обязательно.

При разработке важно только четко представлять себе, как поведет себя та или иная микросхема в данном конкретном включении, будет ли она правильно выполнять требуемую от нее функцию.

Чаще применяются две технологии цифровых микросхем:

ТТЛ (TTL) и ТТЛШ (TTLS) - биполярная транзисторно-транзисторная логика и ТТЛ с диодами Шоттки;

КМОП (CMOS) — комплементарные транзисторы со структурой "металл–окисел–полупроводник".

Различаются они типами используемых транзисторов и схемотехническими решениями внутренних каскадов микросхем.

В статическом режиме или на небольших рабочих частотах микросхемы КМОП потребляют значительно меньший ток от источника питания, чем такие же микросхемы ТТЛ (или ТТЛШ) - правда, только.

На 2.16показаны примеры схем входных и выходных каскадов микросхем, выполненных по этим технологиям.

2.6.1. Входы микросхем.

Разработчику цифрового устройства достаточно считать, что при подаче на вход сигнала логического нуля из этого входа вытекает ток, не превышающий I1min, а при подаче сигнала логической единицы в этот вход втекает ток, не превышающий I1max.

Особым случаем является ситуация, когда какой-нибудь вход не подключен ни к одному из выходов - ни к общему проводу, ни к шине питания (так называемый висящий вход).

Иногда возможности микросхемы используются не полностью, т.е. на некоторые входы не подается сигналов. При этом микросхема может не работать или работать нестабильно, так как ее правильное включение подразумевает наличие на всех входах логических уровней, пусть даже и неизменных.

Поэтому рекомендуется подключать неиспользуемые входы к напряжению питания микросхемы Uсс или к общему проводу (к земле) в зависимости от того, какой логический уровень необходим на этом входе.

|

|

|

|

а) |

в) |

|

Рис. 2.16. Входной и выходной каскады микросхем ТТЛШ (а) и КМОП (в) | |

Для некоторых серий микросхем, выполненных по технологии, неиспользуемые входы надо подключать к напряжению питания не напрямую, а только через резистор определенной величины. При таком включении одного резистора достаточно на 20 входов.

На неподключенных входах микросхем ТТЛ формируется напряжение около 1,5–1,6 В, которое иногда называют висячим потенциалом. Обычно этот уровень воспринимается микросхемой как сигнал логической единицы, но рассчитывать на это не стоит.

Потенциал, образующийся на неподключенных входах микросхем КМОП, может восприниматься микросхемой и как логический нуль, и как логическая единица.

Все входы надо куда-то подключать. Неподключенными допускается оставлять только те входы (ТТЛ, а не КМОП), состояние которых в данном включении микросхемы не имеет значения.

2.6.2. Выходы микросхем

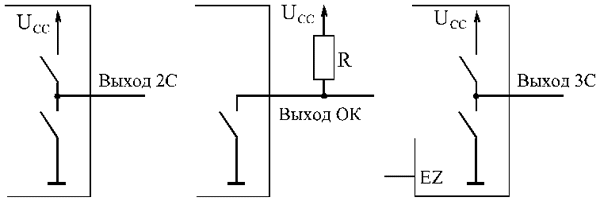

Существуют три разновидности выходных каскадов, существенно различающиеся как по своим характеристикам, так и по областям применения:

стандартный выход или выход с двумя состояниями (обозначается 2С, 2S, ТТЛ, TTL), или иначе логический выход;

выход с открытым коллектором (обозначается ОК, OC);

выход с тремя состояниями или выход с возможностью отключения (обозначается 3С, 3S).

Стандартный (2С) выход

Стандартный выход 2С имеет всего два состояния: логический нуль (U0) и логическая единица (U1), причем оба они активны, то есть выходные токи в обоих этих состояниях (I0min и I0max) могут достигать заметных величин.

Выходное сопротивление логического выхода стремятся сделать малым, способным развивать большие токи для перезарядки емкостных нагрузок и, следовательно, получения высокого быстродействия элемента. Такой тип выхода имеют большинство логических элементов, используемых в комбинационных цепях.

Такой выход можно считать состоящим из двух выключателей, которые замыкаются по очереди (Рис. 2.17.а), причем замкнутому верхнему выключателю соответствует логическая единица на выходе, а замкнутому нижнему - логический нуль.

|

|

|

|

|

а) |

б) |

с) |

|

Рис.2.17. Стандартный выход 2С | ||

Особенность таких выходов состоит в том, что их нельзя соединять параллельно:

во-первых это создает логическую неопределенность, т.к. в точке соединения выхода, формирующего логическую единицу, и выхода, формирующего логический нуль, не будет нормального результата.

Во вторых, при соединении выходов, находящихся в различных логических состояниях возникло бы «противоборство». Вследствие малых величин выходных сопротивлений уравнительный ток при этом может достигать достаточно большой величины, что может вывести из строя элементы выходной цепи.

Схемы логических выходов элементов ТТЛ(Ш) и КМОП подобны двухтактным каскадам – в них оба фронта выходного напряжения формируются с участием активных транзисторов, работающих противофазно, что обеспечивает малые выходные сопротивления при любом направлении переключения выхода (Рис.2.17.б).

Вторая особенность логического выхода двухтактного типа связана с протеканием через транзистор коротких импульсов тока при переключениях из одного логического состояния в другое. Эти токи протекают от источника питания на общую точку «землю».

В статических состояниях таких токов быть не может, т.к. транзисторы Т1 и Т2 работают в противофазе, и один из них всегда заперт.

Однако в переходном процессе из-за некоторой несинхронности переключения транзисторов возникает кратковременная ситуация, в которой проводят оба транзистора, что и порождает короткий импульс сквозного тока значительной величины (Рис.2.17.с.).

Выход с открытым коллектором

Элементы с открытым коллектором имеют выходную цепь, заканчивающуюся одиночным транзистором, коллектор которого не соединен с какими-либо цепями внутри микросхемы (Рис. 2.18,а). Транзистор управляется от предыдущей части схемы элемента так, что может находиться в насыщенном или запертом состоянии. Насыщенное состояние транзистора трактуется как отображение логического нуля, запертое, как логической единицы.

Поэтому для формирования высокого уровня напряжения на выходе элементов с открытым коллектором (типа ОК) требуется подключение внешних резисторов величиной порядка сотен Ом (или другие нагрузки), соединенные с источником питания.

Выход с открытым коллектором ОК можно считать состоящим из одного выключателя, замкнутому состоянию которого соответствует сигнал логического нуля, а разомкнутому - отключенное, пассивное состояние (Рис.2.18.б.).

Несколько выходов типа ОК можно соединять параллельно, подключая их к общей для всех выходов цепочке Ucc – R (Рис.2.18.в). При этом можно получит режим поочередной работы на общую линию, как и для элементов с тремя состояниями, если активным будет лишь один элемент, а выводы всех остальных окажутся запертыми. Если же разрешить активную работу элементов, выходы которых соединены, то можно получить дополнительную логическую операцию, называемую операцией монтажной логики.

При реализации монтажной логики высокое напряжение на общем выходе возникает только при запирании всех транзисторов, т.к. насыщение хоты бы одного из них снижает выходное напряжение до уровня U0 = Uкэн. То есть для получения логической единицы на выходе требуется единичное состояние всех выходов: выполняется монтажная операция И. Поскольку каждый элемент выполняет операцию Шеффера над своими входными переменными, общий результат окажется следующим:

F = X1X2 X3X4 … Xm-1 Xm = X1X2+X3X4+ …+Xm-1 Xm

|

|

|

|

|

а) |

б) |

в) |

|

Рис.2.18. Выход с открытым коллектором | ||

При использовании элементов с ОК в магистрально-модульных структурах требуется разрешать или запрещать работу того или иного элемента. Для элементов типа ОК кВ качестве входа ОЕ может быть использован один из обычных входов элемента. Если речь идет об элемента И-НЕ, то, подавая ) на любой из входов, можно запретить работу элемента, поставив его выход в разомкнутое состояние независимо от состояния других входов. Уровень 1 на этом входе разрешит работу элемента.

Положительной чертой элементов с ОК при работе в магистально-модульных системах является их защищенность от повреждений из-за ошибок управления, приводящих к одновременной выдаче на шину нескольких слов, а также возможность реализации дополнительных операций монтажной логики.

Недостатком таких элементов является большая задержка переключения из 0 в 1. При этом переключении происходит заряд выходной емкости сравнительно малым током резистора R. Сопротивление резистора нельзя сделать слишком малым, т.к. это привлекло бы к большим токам выходной цепи в статике при насыщенном состоянии выходного транзистора. Поэтому положительный фронт выходного напряжения формируется относительно медленно с постоянной времени RC.

До порогового напряжения (до середины полного перепада напряжения) экспоненциально изменяющийся сигал изменится за время 0,7RC, что и составляет задержку tз01.

При работе с элементами типа ОК проектировщик должен задать сопротивление резистора R, которое не является стандартным, а определяется для конкретных условий. Анализ статических режимов задает ограничения величины сопротивленияR снизу и сверху. Значение сопротивления резистора R выбирается в этом диапазоне с учетом быстродействия схемы и потребляемой ею мощности.

Ограничение снизу величины сопротивления резистора R связано с тем, что ее уменьшение может вызвать перегрузку насыщенного транзистора по току. На Рис.2.19.а показан режим, в котором нулевое состояние выхода схемы обеспечивается элементом 1 с ОК. Из этого рисунка видно, что через элемент 1 протекает суммарный ток, складывающийся из токов резистора, входных токов логических элементов (ЛЭ1…ЛЭn) и токов заперых транзисторов элементов с ОК 2 …m, т.е.

Iвых.0 = IR + nIвх.0+ (m-1)IZ≈ IR + nIвх.0, где

Iвх.0 – входные токи элементов приемников сигнала при низком уровне выходных напряжений;

IZ - токи запертых выходов ОК (обычно пренебрежимо малые);

IR = (Ucc – U0)/R.

Чтобы ток выхода элемента 1 не превысил допустимого значения следует соблюдать условие

R >= (Ucc – U0)/(IВых.0.max - nIВх.0.max).

Ограничение сверху величины сопротивления резистора R связано с необходимостью гарантировать достаточно низкий уровень напряжения U1 формируемого в схеме при запертом состоянии всех выходов элементов с ОК.

Из схемы Рис.2.19.б видно, что U1 = Ucc – IRR.

В то же время IR = mIZ + nIВх.1.max.

Из полученных выражений следует R <= (Ucc – UВых.1.min)/(mIZ + nIВх.1.max) , где UВых.1.min - паспортный параметр элемента.

Имея границы диапазона значений сопротивления R, полученные как показано выше, проектировщик должен выбрать некоторое конкретное его значение. Выбор вблизи нижней границы

|

|

|

|

а) |

б) |

|

Рис.2.19. Схемы для расчета минимального (б) и максимального (а) значений сопротивлений внешней цепи с открытым коллектором. | |

Улучшает быстродействие схемы, а выбор вблизи верхней потребляемую мощность.

Выход с тремя состояниями

Выход с тремя состояниями 3С очень похож на стандартный выход, но к двум состояниям добавляется еще и третье - пассивное, в котором выход можно считать отключенным от последующей схемы. Такой выход можно считать состоящим из двух переключателей (Рис. 2.20.а), которые могут замыкаться по очереди, давая логический нуль и логическую единицу, но могут и размыкаться одновременно. Третье состояние называется высокоимпедансным или Z-состоянием. Для перевода выхода в третье Z-состояние используется специальный управляющий вход, обозначаемый OE(Рис. 2.20.б)(Output Enable - разрешение выхода) или EZ (Enable Z-state).

|

|

|

|

|

а) |

б) |

с) |

|

Рис.2.20 Выход с тремя состояниями | ||

При наличии разрешения (ОЕ = 1) элемент работает как обычно, выполняя свою логическую операцию, а при его отсутствии (ОЕ=0) переходит в состояние «отключено».

Входы типа 3С можно соединять параллельно (Рис.2.20.с) при условии, что в любой момент времени активным может быть только один из них. В этом случае отключенные выходы не мешают активному формированию сигнала в точке соединения выходов. Эта возможность позволяет применять элементы 3С в магистрально-модульных микропроцессорных и других системах, где многие источники информации поочередно пользуются одной и той же линией связи (рис.2.21).

Объединение выходов цифровых микросхем совершенно необходимо также при шинной (или магистральной) организации связей между цифровыми устройствами.

При шинной организации связей все сигналы между устройствами передаются по одним и тем же линиям (проводам), но в разные моменты времени (это называется временным мультиплексированием). В результате количество линий связи резко сокращается, а правила обмена сигналами существенно упрощаются.

Рис. 2.21. Шинная организация связей

Группа линий (сигналов), используемая несколькими устройствами, как раз и называется шиной. Понятно, что объединение выходов в этом случае совершенно необходимо - ведь каждое устройство должно иметь возможность выдавать свой сигнал на общую линию. К недостаткам шинной организации относится, прежде всего, невысокая скорость обмена сигналами.

Используя микросхемы с тремя состояниями по выходу можно создавать магистрали с двунаправленными потоками информации, а также уплотнять каналы передачи данных (рис.2.22).

Элементы типа 3С сохраняют такие достоинства элементов с логическим выходом как быстродействие и высокая нагрузочная способность.

|

|

|

|

а) работа на общую нагрузку |

б) двухсторонняя передача информации |

|

Рис.2.22. Использование МС с тремя состояниями по выходу | |