- •Содержание

- •Введение

- •1. Основы цифровой электроники

- •1.1. Простейшие способы получения цифрового сигнала

- •1.2. Простейшие способы контроля цифровых сигналов

- •1.3. Логические переменные, базовые операции между логическими переменными

- •1.4. Числа, используемые в цифровой электронике

- •1.5. Арифметические действия над двоичными числами

- •1.6. Переполнение

- •1.7. Цифровая интегральная схема

- •1.8. Упрощение и минимизация логических функций

- •1.9 Недоопределенная функция

- •1.10. Контрольные вопросы

- •1.11. Индивидуальные задания

- •2. Логические элементы

- •2.1. Базовые логические элементы

- •2.2. Особенности работы логических элементов

- •2.2.1. Совместимость входных и выходных сигналов

- •2.2.2. Нагрузочная способность

- •2.2.3. Квантование (формирование) сигнала

- •2.2.4. Помехоустойчивость

- •2.2.5. Работоспособность в широкой области допусков и параметров

- •2.2.6. Затухание переходных процессов за время одного такта

- •2.3. Основные характеристики логических элементов

- •2.4. Основные параметры логических элементов

- •2.4.1. Динамические параметры

- •2.4.2. Статические параметры логических элементов

- •2.5. Особенности проектирования цифровых приборов

- •2.6. Входы и выходы цифровых микросхем

- •2.6.1. Входы микросхем.

- •2.6.2. Выходы микросхем

- •2.7. Контрольные вопросы

- •2.8. Индивидуальные задания

- •3. Триггеры

- •3.1.Общие сведения

- •3.1.1. Параметры триггера

- •3.2. Принцип работы асинхронного триггера

- •3.2.1. Асинхронный rs триггер

- •3.2.1. Асинхронный jk триггер

- •3.2.3. Асинхронный т триггер

- •3.3.Синхронные триггеры

- •3.3.1. Состязания в асинхронных комбинационных и последовательных схемах

- •3.3.2. Синхронный rs триггер

- •3.3.3. D триггер

- •3.4.Основные схемы включения триггеров

- •3.4.1. Подавление дребезга контактов выключателя при помощи триггера

- •3.4.2. Использование триггера в качестве флага процесса

- •3.4.3. Синхронизация с помощью триггера

- •3.4.4. Построение линий задержки с помощью триггера

- •3.5. Контрольные вопросы

- •3.6. Индивидуальные задания

- •4. Регистры

- •4.1.Общие сведения

- •4.2. Регистры хранения (памяти)

- •4.2.1. Стробируемые регистры

- •4.2.2. Тактируемые регистры

- •4.3. Регистры сдвига

- •4.4. Способы вывода информации из регистра

- •4.5. Контрольные вопросы

- •4.5. Индивидуальные задания

- •5. Счетчики

- •5.1.Общие сведения

- •5.2. Счетчики с последовательным переносом (асинхронные счетчики)

- •5.2.1. Суммирующие счетчики

- •5.2.2. Вычитающие счетчик

- •4.2.3. Увеличение разрядности асинхронных счетчиков

- •5.2.4. Применение асинхронных счетчиков

- •5.3. Счетчики с параллельным переносом (синхронные счетчики)

- •5.3.1. Синхронные счетчики с асинхронным переносом

- •5.3.2. Синхронные счетчики с синхронным переносом

- •5.4. Счетчики с произвольным коэффициентом счета

- •5.5. Контрольные вопросы

- •5.6. Индивидуальные задания

- •6. Шифраторы и дешифраторы

- •6.1.Общие сведения

- •6.2. Дешифраторы

- •6.2.1. Применение дешифраторов

- •6.3. Шифраторы

- •6.4. Контрольные вопросы

- •6.5. Индивидуальные задания

- •7. Мультиплексоры, демультиплексоры

- •7.1.Мультиплексоры

- •7.2. Демультиплексоры

- •7.3. Контрольные вопросы

- •7.4. Индивидуальные задания

- •8. Компараторы

- •8.1 Одноразрядный компаратор

- •8.2 Многоразрядный компаратор

- •8.3. Контрольные вопросы

- •8.4. Индивидуальные задания

- •9. Сумматоры

- •9.1.Общие сведения

- •9.2.Четвертьсумматор

- •9.3.Полусумматор

- •9.4. Полный одноразрядный двоичный сумматор

- •9.5. Многоразрядные сумматоры

- •9.5.1. Последовательный многоразрядный сумматор

- •9.5.2. Параллельный многоразрядный сумматор с последовательным переносом

- •9.5.3. Параллельный многоразрядный сумматор с параллельным переносом

- •9.6. Микросхемы многоразрядных сумматоров

- •9.7. Сумматоры групповой структуры

- •9.9. Контрольные вопросы

- •9.10. Индивидуальные задания

- •10. Преобразователи кодов

- •10.2. Контрольные вопросы

- •11. Одновибраторы и генераторы

- •11.1.Одновибраторы

- •11.2. Генераторы

- •11.3. Контрольные вопросы

- •12. Память

- •12.1 Общие сведения

- •12.2. Типовые структуры и функциональные узлы микросхем памяти

- •12.3. Условные графические обозначения микросхем памяти

- •12.4. Применение пзу

- •12.5. Применение озу

- •12.6 Контрольные вопросы

- •12.7. Индивидуальные задания

- •13. Цифро-аналоговые и аналого-цифровые преобразователи

- •13.1 Цифро-аналоговые преобразователи (цап)

- •13.2 Аналого-цифровые преобразователи (ацп)

- •Контрольные вопросы

- •14. Типовые ситуации при построении узлов и устройств на стандартных интегральных

- •14.1. Режимы неиспользуемых входов в логических элементах

- •14.2. Режимы неиспользуемых логических элементов

- •14.3. Наращивание числа входов логических элементов

- •14.4. Снижение нагрузок на выходах логических элементов

- •14.5. Паразитные связи цифровых элементов по цепям питания

- •14.6. Паразитные связи цифровых элементов по цепям питания

- •14.6.1.Внешние помехи

- •14.6.2.Токовые помехи

- •14.6.3. Перекрестные помехи

- •14.6.4. Искажения сигналов в несогласованных линиях

- •Последовательное согласование волновых сопротивлений

- •14.6.5. Линии передачи сигналов

- •Список литературы

2.3. Основные характеристики логических элементов

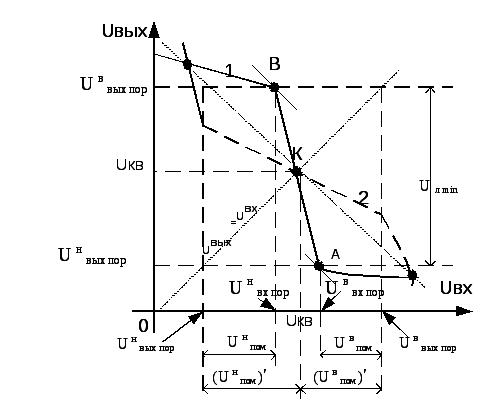

Амплитудная передаточная характеристика

Uвых = F(Uвх ) определяет формирующие свойства ЛЭ, его помехоустойчивость, амплитуду и уровни стандартного сигнала.

Вид характеристики зависит от типа логического элемента (ТТЛШ, пМОП, ЭСЛ и т.д.) и может изменяться в определенных пределах в зависимости от разброса параметров схем, изменений напряжения питания, нагрузки, температуры окружающей среды.

Рассмотрим типову амплитудную передаточную характеристику инвертирующего ЛЭ (Рис.2.10).

В статическом состоянии выходной сигнал ЛЭ может находится либо на верхнем Uв, либо на нижнем Uн уровне напряжения. Верхний (Uв) и нижний (Uн) уровни логических сигналов находятся как точки пересечения амплитудной передаточной характеристики (кривая 1) с ее зеркальным отображением (кривая 2) относительно прямой единичного усиления Uвых = Uвх.

Разность Uввых – Uнвых является логическим перепадом Uл выходных уровней ЛЭ.

Зоны статической помехоустойчивости ЛЭ по нижнему уровню (Uн пом)′ и верхнему (Uв пом)′ уровням напряжения в комбинационных логических цепях определяются выражениями:

|

|

|

Рис.2.10. Амплитудная передаточная характеристика инвертирующего ЛЭ |

(Uн пом)′ =Uкв -Uн вых пор

(Uв пом)′ = Uв вых пор – Uкв,

где (Uн пом)′ и (Uв пом)′ характеризуют максимально допустимые уровни статической помехи на входе ЛЭ в комбинационных логических цепях; Uн вых пор - выходное логическое напряжение нижнего уровня; Uв вых пор - выходное логическое напряжение верхнего уровня.

Однако из-за наличия схем с положительной обратной связью в технической документации на все интегральные схемы зоны статической помехоустойчивости по входу ограничиваются входными пороговыми напряжениями Uн вх пор - по нижнему уровню; Uв вх пор - по верхнему уровню.

Эти пороговые напряжения называются соответственно пороговыми напряжениями зоны переключения (порог зоны переключения) нижнего уровня и пороговым напряжением зоны переключения верхнего уровня.

В зоне переключения, заключенной между пороговыми напряжениями работа ЛЭ в статическом режиме запрещается.

Т.о. статическая помехоустойчивость ЛЭ по нижнему уровню входного сигнала определяется выражением Uн пом = Uн вх пор – Uн вых пор, а по верхнему уровню входного сигала – выражением Uв пом = Uв вых пор - Uв вх пор.

Максимальная помехоустойчивость ЛЭ по нижнему и верхнему уровням достигается при идеальной амплитудной передаточной характеристике, для которой Uн вх пор = Uв вых пор = Uкв.

Входная характеристика Iвх = F(Uвх) – зависимость входного тока ЛЭ от входного напряжения определяет нагрузочную способность ЛЭ и режим работы линий связи.

Выходная характеристика Uвых = F(Iвых) – зависимость выходного напряжения ЛЭ от выходного тока нагрузки. Эта характеристика в совокупности с входной позволяет определить нагрузочную способность ЛЭ, режим его работы и способ согласования переходных процессов в линиях связи.

2.4. Основные параметры логических элементов

Конструктивно-технологическая реализация цифровых ИС во многом определяет их основные технические параметры – быстродействие, потребляемую мощность, устойчивость к внешним дестабилизирующим факторам.

Различают следующие основные виды (типы) конструктивно-технологического исполнения ИС: биполярные ИС, ИС на основе МОП транзисторов, ИС на основе комбинированной биполярно-комплементарной (КМОП) технологии.

ИС на основе р-МОП обладают самой низкой стоимостью, однако имеют невысокие быстродействие и нагрузочную способность, не сопрягаются со стандартными ТТЛ-микросхемами.

ИС на основе n-МОП характеризуются высокой степенью интеграции и быстродействием, однако обладают низкой нагрузочной способностью при сравнительно высокой потребляемой мощности, хотя могут сопрягаться с ТТЛ-микросхемами.

ИС на основе КМОП-транзисторов обладают высоким быстродействием, очень низкой потребляемой мощностью и высокой помехоустойчивостью, сопрягаются со стандартными ТТЛ-микросхемами.

Цифровые ИС на основе ЭСЛ-технологии (эмиттерно-связанной технологии) отличаются сверхвысоким быстродействием, однако обладают высокой потребляемой мощностью, требуют специальных внешних схем для сопряжения ИС других типов.

Цифровые ИС на основе интегральной инжекционной логики (И2Л) характеризуются самой высокой степенью интеграции, низкой потребляемой мощностью, высоким быстродействием, сопрягаются с другими типами ИС.

Цифровые ИС на основе технологии транзисторно-транзисторной логики с диодами Шоттки (ТТЛШ) обладают более низким по сравнению с ЭСЛ ИС быстродействием, однако рассеивают меньшую мощность, обеспечивая высокие характеристики нагрузочной способности, помехоустойчивости.

КМОП ИС имеют лучшие черты биполярных (высокое быстродействие и нагрузочную способность) и КМОП ИС (низкая потребляемая мощность и высокая помехоустойчивость).

Различают статические и динамические параметры ЛЭ.