Lek2013 / lek3

.docЛекция 3

Комбинационная логика

Комбинационная логическая схема это та у которой состояние выходов зависит только от состояния входов. Т.е. комбинационная схема не содержит памяти.

Пример описания комбинационной логики:

Пусть есть схема:

Здесь комментарий выделен двумя тире --

Данный пример синтезирует схему

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity gates is

port (a, b: in STD_LOGIC_VECTOR (3 downto 0);

y1, y2, y3, y4,y5: out STD_LOGIC_VECTOR (3 downto 0));

end;

architecture synth of gates is

begin

— —шина 4 bit

y1<= a and b;

y2 <= a or b;

y3 <= a xor b;

y4 <= a nand b;

y5 <= a nor b;

end;

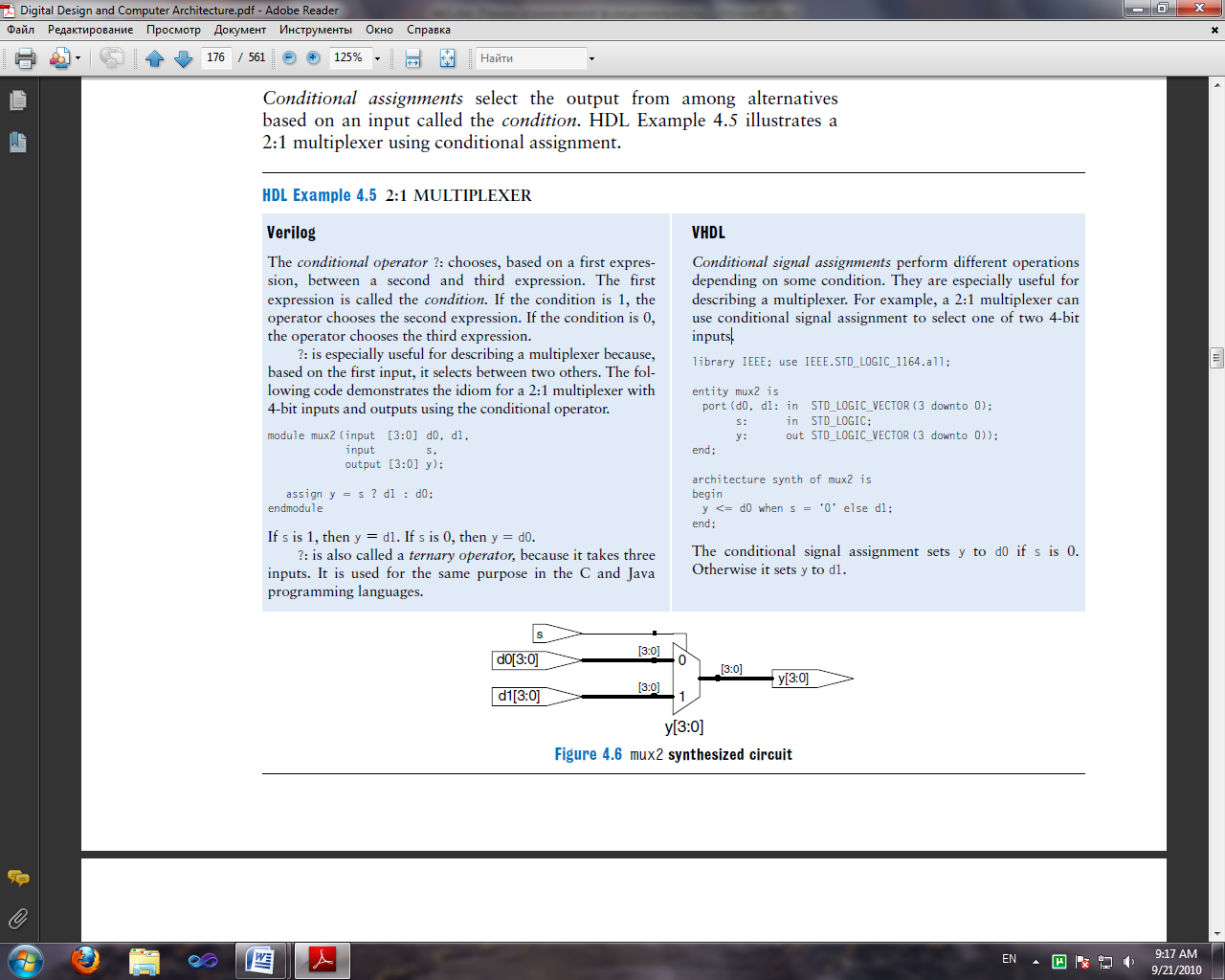

Мультиплексоры

Мультиплексор представляет из себя сему с 2^n шинами данных и n управляющими линиями и одной выходной шиной. Задача мультиплексора в зависимости от адреса на управляющих линиях коммутировать соответствующую входную шину на выход.

Пример n=1:

Описание данного мультиплексора на VHDL

library IEEE; use IEEE.STD_LOGIC_1164.all;

entity mux2 is

port (d0, d1: in STD_LOGIC_VECTOR (3 downto 0);

s: in STD_LOGIC;

y: out STD_LOGIC_VECTOR (3 downto 0));

end;

architecture synth of mux2 is

begin

y <= d0 when s = ‘0’ else d1;

end;

Когда на управляющий вход мультиплексора подан логический ноль то выходная 4-х битная шина соединяется с входной шиной D0, иначе со входной шиной D1.

П

00 D0 D1

О 01 Y

D2 d

10

11

D3 d

l S

entity mux4 is

p ort

(d0, d1,d2, d3: in STD_LOGIC_VECTOR (3 downto 0);

ort

(d0, d1,d2, d3: in STD_LOGIC_VECTOR (3 downto 0);

s: in STD_LOGIC_VECTOR (1 downto 0);

y: out STD_LOGIC_VECTOR (3 downto 0));

end;

architecture synt of mux4 is

begin

y <= d0 when s = “00” else

d1 when s= “01” else

d2 when s = “10” else

d3;

end;

Дешифратор (англ. Decoder)

Декодер получает на входе n-разрядное число и использует его для того чтобы, установить на одном из выходов логическую единицу. Декодер с n-входами имеет 2^n выходов.

Обозначение на схеме:

Пример релизации дешифратора в отдельной микросхеме: 74HC42

Пример использования декодера:

Пусть надо объединить 8 микросхем памяти. Тогда 3 старших бита адреса можно подать на декодер, а выходы декодера на входы разрешения работы микросхем.

Пример описания декодера 3:8

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity Decoder3_8 is

Port ( A : in STD_LOGIC_VECTOR (2 downto 0);

F : out STD_LOGIC_VECTOR (7 downto 0));

end Decoder3_8;

architecture Synth of m1 is

begin

F<=x"01" after 100ns when A="000" else

x"02" after 100ns when A="001" else

x"04" after 100ns when A="010" else

x"08" after 100ns when A="011" else

x"10" after 100ns when A="100" else

x"20" after 100ns when A="101" else

x"40" after 100ns when A="110" else

x"80" after 100ns;end Synth;

Компараторы

Задачей компаратора является сравнение двух двоичных слов поступающих на вход. Компаратор можно реализовать при помощи схемы, в которой единица на выходе означает равенство.

Обозначение на схеме:

Схема 4-х битового компаратора

Поведенческое описание компаратора:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity Comparator is

Port ( A : in STD_LOGIC_VECTOR (3 downto 0);

B : in STD_LOGIC_VECTOR (3 downto 0);

Y : out STD_LOGIC);

end Comparator;

architecture Synth of Comparator is

begin

Y <='1' when A=B else '0';

end Synth;

Поведенческое и структурное описание на VHDL

Как видно на примере выше поведенческое описание схемы не отражает внутреннее устройство схемы, а только при помощи конструкций языка описания аппаратуры описывает ее работу.

Кроме поведенческого стиля существует структурный – при котором код на VHDL описывает из каких элементов и из каких связей состоит схема.

Пример описания компаратора в поведенческом стиле (см. схема выше):

-

Сначала требуется выделить составные части схемы

Для примера Это будет двухвходовый элемент исключающий или с инверсией и 4-х входовый логический элемент И.

Для каждого элемента на VHDL требуется создать модуль описывающий роботу элемента в поведенческом стиле.

Файл NXOR2.vhd

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity NXOR2 is

Port ( i1 : in STD_LOGIC;

i2 : in STD_LOGIC;

y : out STD_LOGIC);

end NXOR2;

architecture Beh of NXOR2 is

begin

y<= not ( i1 xor i2);

end Beh;

//*************************************************

файл AND4.VHD

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity AND4 is

Port ( i1,i2,i3,i4 : in STD_LOGIC;

y : out STD_LOGIC);

end AND4;

architecture Beh of AND4 is

begin

y<= i1 and i2 and i3 and i4 after 10ns;

end Beh;

-

На втором этапе следует объединить все составные элементы схемы.

Для этого требуется пронумеровать внутренние соединения и составные блоки.

Описание внутренних соединений выполняется при помощи сигналов, которые схожи с глобальными переменными в обычных программах.

Файл main.vhd

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity main is

Port ( A0,A1,A2,A3 : in STD_LOGIC;

B0,B1,B2,B3 : in STD_LOGIC;

EQ : out STD_LOGIC);

end main;

architecture Struct of main is

--//внешний интерфейс составных компонент схемы

COMPONENT NXOR2

PORT(

i1,i2 : IN std_logic;

y : OUT std_logic

);

END COMPONENT;

COMPONENT AND4

PORT(

i1,i2,i3,i4 : IN std_logic;

y : OUT std_logic

);

END COMPONENT;

signal s0,s1,s2,s3 : STD_LOGIC;

begin

--соединение блоков

u0: NXOR2 PORT MAP(i1 =>A0 ,i2 =>B0 ,y => s0 );

u1: NXOR2 PORT MAP(i1 =>A1 ,i2 =>B1 ,y => s1 );

u2: NXOR2 PORT MAP(i1 =>A2 ,i2 =>B2 ,y => s2 );

u3: NXOR2 PORT MAP(i1 =>A3 ,i2 =>B3 ,y => s3 );

u4: AND4 PORT MAP(i1 => s0,i2 => s1,i3 =>s2 ,i4 => s3,y => EQ);

end Struct;

Достоинства структурного стиля описания:

отдельный блок можно описать в файле после чего его повторно использовать в новых проектах. Данный подход оправдан для сложных цифровых блоков (например процессорного ядра).

Недостаток структурного стиля описания:

Большая громоздкость кода по сравнению с поведенческим стилем.

Пример реализации на Verilog:

Файл nxor2.v

`timescale 1ns / 1ps

module nxor2(

input i1,

input i2,

output y

);

assign #20 y= i1 ~^ i2;

endmodule

Файл nand4.v

`timescale 1ns / 1ps

module and4(

input i1,

input i2,

input i3,

input i4,

output y

);

assign #10 y= i1 & i2 & i3 & i4;

endmodule

Файл Мain.v

`timescale 1ns / 1ps

module main(

input A0,

input A1,

input A2,

input A3,

input B0,

input B1,

input B2,

input B3,

output EQ );

wire s0,s1,s2,s3;

nxor2 u0(

.i1(A0),

.i2(B0),

.y(s0));

nxor2 u1(

.i1(A1),

.i2(B1),

.y(s1));

nxor2 u2(

.i1(A2),

.i2(B2),

.y(s2));

nxor2 u3(

.i1(A3),

.i2(B3),

.y(s3));

and4 u4(

.i1(s0),

.i2(s1),

.i3(s2),

.i4(s3),

.y(EQ));

endmodule