Lek2013 / lek4

.docЛекция 4

Сумматоры

Сумматор – цифровая схема позволяющая складывать два двоичных числа. Различают полусумматор и полный сумматор. В полном сумматоре есть вход переноса из младшего разряда и выход переноса для переноса в старший разряд. В полусумматоре присутствует только выход переноса.

Пример суммирования:

Схема полусумматора:

Полусумматор подходит для сложения битов нижних разрядов двух многобитовых слов. Для сложения битов в середине слова следует использовать полный сумматор.

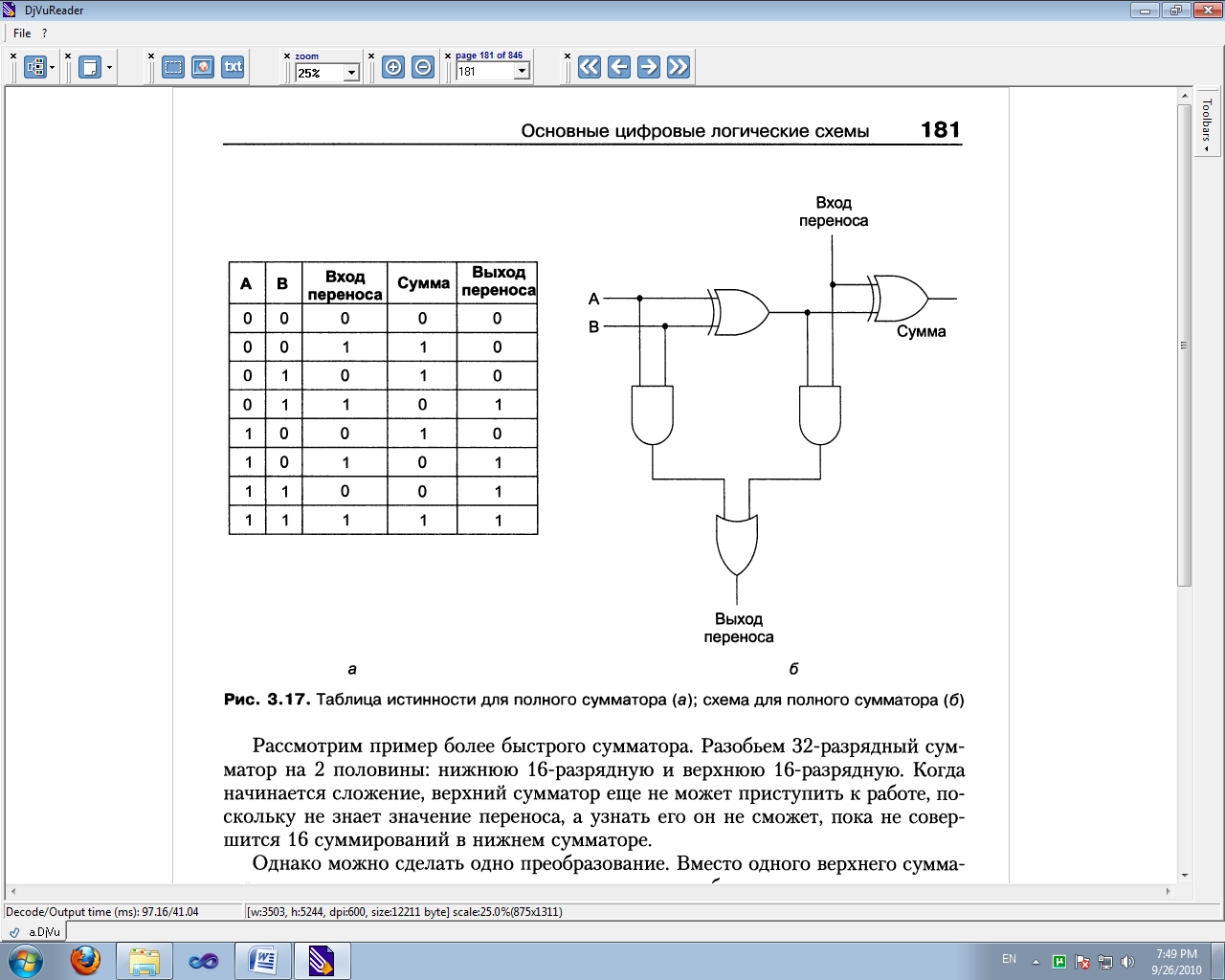

Схема полного сумматора:

Как видно из таблиц истинности получить полусумматор из полного сумматора можно подав на вход переноса логический ноль.

Описание полного одноразрядного сумматора на VHDL:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity add2 is

Port ( c1,a,b: in STD_LOGIC;

c2,s2 : out STD_LOGIC);

end add2;

architecture Beh of add2 is

signal t:std_logic;

begin

c2<=(a1 and c1) or (b and c1) or (a1 and b);

t<=a xor b; s2<=c1 xor t;

end Beh;

Чтобы получить N-разрядный сумматор надо объединить N полных одноразрядных сумматоров. Схема 4-х разрядного сумматора:

Описание 4-х разрядного сумматора на VHDL

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity main is

Port ( A,B : in STD_LOGIC_VECTOR (3 downto 0);

Sum : out STD_LOGIC_VECTOR (3 downto 0);

c2 : out STD_LOGIC;

c1 : in STD_LOGIC);

end main;

architecture Behav of main is

COMPONENT add2

PORT( c1,a,b : IN std_logic;

c2,s2 : OUT std_logic);

END COMPONENT;

signal s0,s1,s2: STD_LOGIC;

begin

u0: add2 PORT MAP(c1 =>c1,a =>A(0),b =>B(0),c2 =>s0,s2 =>Sum(0));

u1: add2 PORT MAP(c1 =>s0,a =>A(1),b =>B(1),c2 =>s1,s2 =>Sum(1));

u2: add2 PORT MAP(c1 =>s1,a =>A(2),b =>B(2),c2 =>s2,s2 =>Sum(2));

u3: add2 PORT MAP(c1 =>s2,a =>A(3),b =>B(3),c2 =>c2,s2 =>Sum(3));

end Behav;

Параметризованные модули и оператор generate

Часто требуется описать цифровую схему не фиксированной, а произвольной разрядности, состоящую из повторяющихся регулярных частей. Регулярные схемы также называю систолическими.

Разрядность может достигать нескольких сотен единиц, поэтому VHDL имеет специальную языковую конструкцию подключения в цепочку частей систолической схемы.

Оператор generate позволят задать повторяющуюся часть в виде цикла for, а нерегулярные части подключить используя оператор if. Параметр модуля задается при помощи слова generic перед описанием портов модуля.

Пример описания сумматора произвольной разрядности:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity main is

generic( N:integer:=4);

Port ( A,B : in STD_LOGIC_VECTOR (N-1 downto 0);

Sum : out STD_LOGIC_VECTOR (N-1 downto 0);

c2 : out STD_LOGIC;

c1 : in STD_LOGIC);

end main;

architecture Behavioral of main is

COMPONENT add2

PORT( c1,a,b : IN std_logic;

c2,s2 : OUT std_logic);

END COMPONENT;

signal s:STD_LOGIC_VECTOR(N-2 downto 0);

begin

g0:for i in N-1 downto 0 generate

g1:if(i=N-1) generate

bitN:add2 port map (c1 =>s(N-2),a =>A(N-1),b =>B(N-1),c2 =>c2,s2 =>Sum(N-1));

end generate g1;

g2:if(i>0 and i<N-1) generate

biti:add2 port map (c1 =>s(i-1),a =>A(i),b =>B(i),c2 =>S(i),s2 =>Sum(i));

end generate g2;

g3:if(i=0) generate

bit0:add2 port map (c1 =>c1,a =>A(0),b =>B(0),c2 =>S(0),s2 =>Sum(0));

end generate g3;

end generate g0;

end Behavioral;

АЛУ

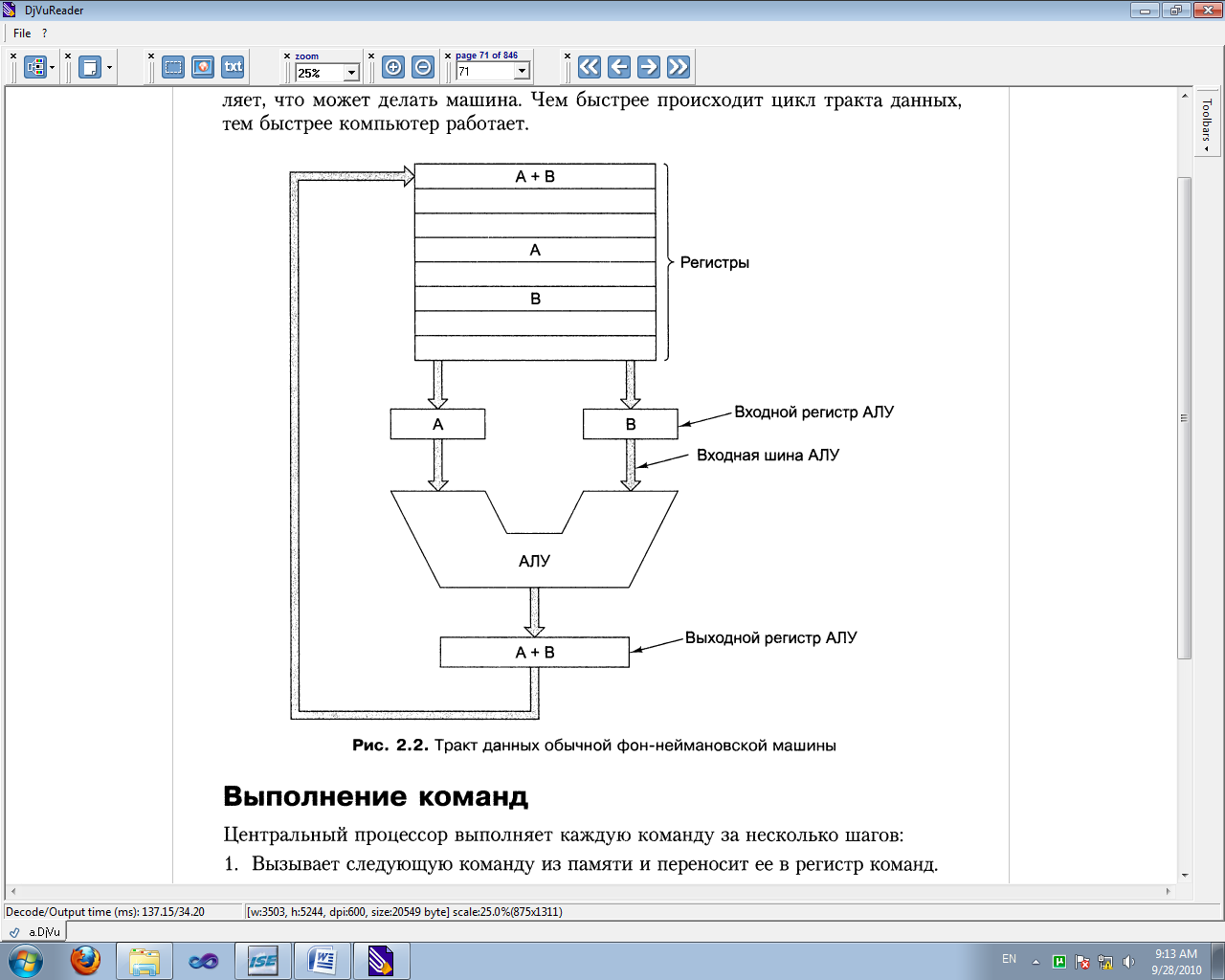

Тракт данных типового процессора включает набор регистров и арифметико-логическое устройство. В современных процессорах операнды загружаются в регистры общего назначения из памяти, после чего через промежуточные регистры поступают в АЛУ. Результат работы АЛУ снова записывается в регистр.

Схема тракта данных процессора:

Схема одноразрядного АЛУ

Это АЛУ может вычислять одно из 4-х действий:

1)A И В, 2) А ИЛИ В,3) инверсия И, 4) A+B

Выбор действия осуществляется подачей управляющих сигналов на входы F0F1.

F0=0 F1=0 => A И В

F0=0 F1=1 => A ИЛИ В

F0=1 F1=0 => инверсия В

F0=1 F1=1 => A + В

Операнды со входа A B считываются при подаче логической единицы на входы разрешения ENA ENB. При подаче единицы на вход INVA значение операнда A инвертируется.

Описание данной схемы на VHDL:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity alu1bit is

Port ( F : in STD_LOGIC_VECTOR (1 downto 0);

A,B,c1: in STD_LOGIC;

ENA,ENB,INVA:in STD_LOGIC;

c2,Y : out STD_LOGIC);

end alu1bit;

architecture Behavioral of alu1bit is

COMPONENT add2

PORT( c1,a,b : IN std_logic;

c2,s2 : OUT std_logic);

END COMPONENT;

signal abOr,abAnd,bNot,abSum:std_logic;

signal ea,eb: std_logic;

begin

ea<=INVA xor (A and ENA);

eb<=B and ENB;

abOr<=ea or eb;

abAnd<=ea and eb;

bNot<=not eb;

add2_i:add2 port map(c1=>c1,a=>ea,b=>eb,c2=>c2,s2=>abSum);

y<=abAnd when F="00" else

abOr when F="10" else

bNot when F="01" else

abSum;

end Behavioral;

Если требуется выполнить вычитание то одни член разности надо инвертировать, выполнить сложении и к результату прибавить единицу. На вышеприведенном АЛУ это можно сделать за несколько тактов синхронизации.

Пример

B=5; A=2; B-A=? Вычитаемое следует представить в

B=101; A=010;

Инверсия А= 101 - обратный код

Дополнительный код = 110= инверсия А+1

101+

110 = 1011

Старший разряд отбрасываем результат = 011=3