Lek2013 / lek2

.doc№ Технологическая реализация цифровой аппатауры

Вентили производятся в модулях именуемых микросхемами. Микросхема объединяет на одной кремниевой подложке множество транзисторов. Микросхемы классифицируют по числу вентилей:

МИС – малая интегральные схемы от 1 до 10 вентилей

СИС - средние интегральные схемы 10 -100

БИС – большие интегральные схемы 100 – 100 000

СБИС – сверхбольшие интегральные схемы более 100 000

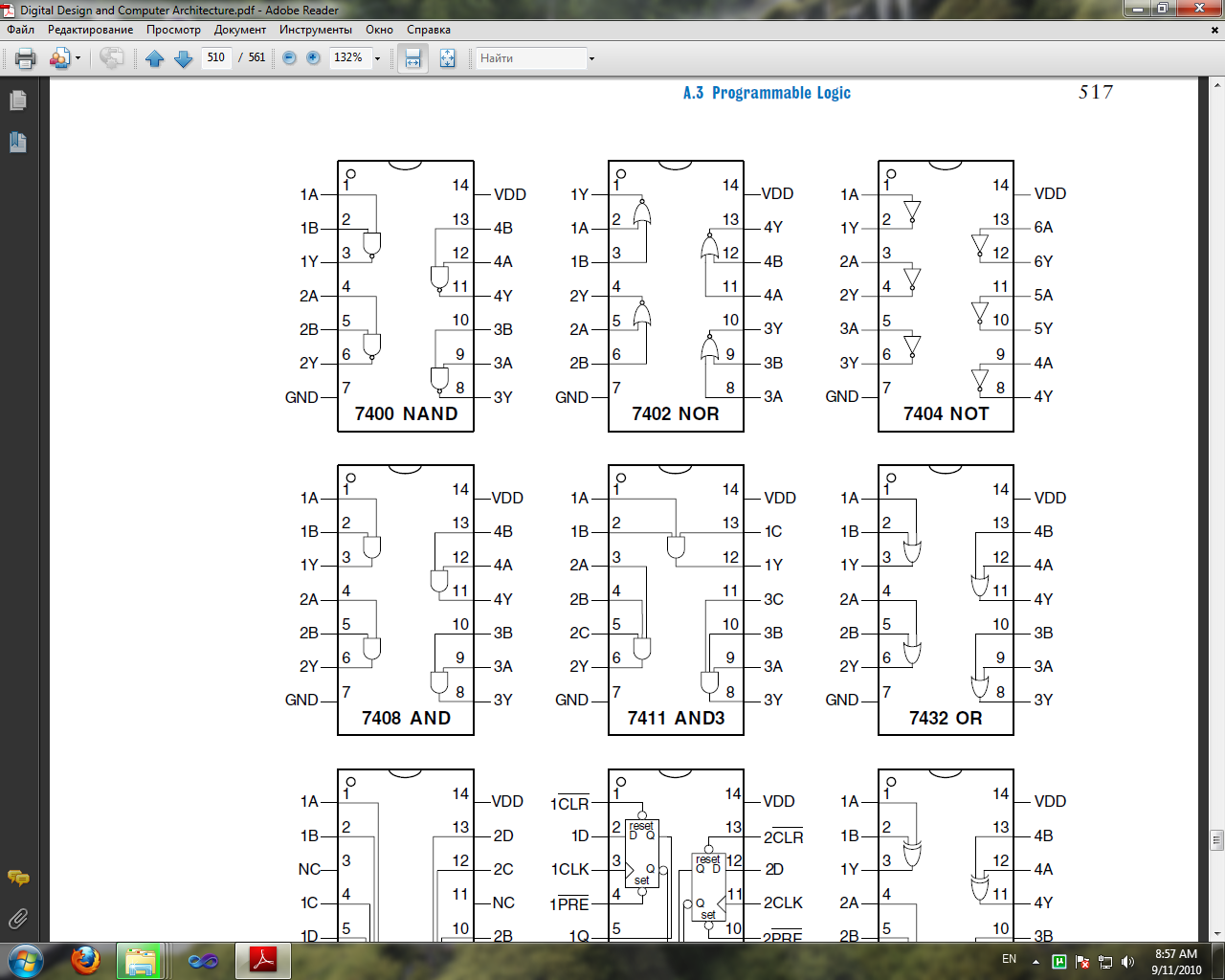

Пример микросхемы малой степени интеграции:

ST74HC00 - микросхема содержит 4 вентиля И-НЕ

Другие микросхемы

ST74HC04 – 6 вентилей NOT

ST74HC11 – 3 вентиля AND c тремя входами

ST74HC74 – два триггера

ST74HC138 - дешифратор и т.д.

Микросхемы могут выпускаться в различных корпусах. Различают следующие основные типы корпусов:

-

DIP(Dual In-Line Package) (малое число выводов <=40)

-

QFP (от англ. Quad Flat Package) (число выводов 44<pin<260) (шаг выводов 0.4-1 мм)

-

BGA (Ball grid array) (много выводов 200<pin<1200 но очень сложно

вести монтаж)

Мкросхемы цифровой аппаратуры размещают на плате из текстолита с вытравленными проводниками на обоих поверхностях. Для сложных устройств применяют многослойные платы содержащие проводники внутри текстолитовой подложки.

По способу монтажа различают:

-

Поверхностный SMD- ( surface mounted device)

Рисунок

-

Монтаж через отверстия. THT- (Through-hole technology)

Рисунок

Напряжение питания в современных устройствах обычно составляет 3.3В или 5В. Потребляемая мощность может составлять от долей ват до нескольких ват. При отключении тактового сигнала в статическом режиме потребление падает практически до нуля.

№Языки описания аппаратуры

Способ описания аппаратуры через графические принципиальные схемы трудоемок и часто ведет к ошибкам ввода. Начиная с 90-х годов широко стали внедряться компьютерные средства синтеза цифровых схем из программ, написанных на языке описания аппаратуры (HDL –hardware description language)

Наибольшее распространение получили языки

Verilog - создан в 85 году

VHDL - появился в 83 году и разработан военным ведомством США

Оба языка строятся на одинаковых принципах но имеют разный синтаксис. (как Паскаль и Си++)

Модули

Блок аппаратуры со входами и выходами называют модулем. Есть два стиля описания функциональности модуля:

-

Поведенческий (behavioral)

-

Структурный (structural.)

Поведенческий стиль говорит, что модуль делает, и в явном виде содержит алгоритм функционирования описываемого модуля.

Структурное описание модуля говорит из каких составных частей строиться данный модуль. Часто используется для создания схемы из готовых библиотечных модулей.

Пример поведенческого описания модуля на языке VHDL.

Пусть модуль вычисляет булеву функцию из примера к первой лаб. работе:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity modul1 is

Port ( x0 : in STD_LOGIC;

x1 : in STD_LOGIC;

x2 : in STD_LOGIC;

y : out STD_LOGIC);

end modul1;

architecture Behavioral of modul1 is

begin

y<=(x0 and x1) or (x1 and x2) or (x0 and x2);

end;

Описание на VHDL состоит из 3-х частей

-

Подключение библиотек

-

Блока entity с описанием всех входов и выходов

-

Блока реализации

Для всех входных и выходных сигналов следует описать их тип. В приведенном примере имя типа STD_LOGIC означает, что значение сигнала может принимать 0 или 1 а также неопределенное значение.

Тип STD_LOGIC определен в библиотеке IEEE.STD_LOGIC_1164.

Название модуля в блоке entity и в блоке реализации должно совпадать. Название архитектуры может быть любым.

Пример на языке Verilog

module modul1(

input x0,

input x1,

input x2,

output y

);

assign y=x0&x1 | x0&x2 | x1&x2;

endmodule

По статистике применяют Verilog – 40% VHDL – 60%

Например американское военное ведомство и европейское космическое агентство применяют VHDL, а коммерческий производитель графических ускорителей nVideo на собеседованиях требует Verilog.

Назначение языков описания аппаратуры

Языки описания аппаратуры служат для двух целей

-

Симуляции цифровых схем

-

Синтеза цифровых схем

При симуляции проверяется правильность выходных значении при подаче различных тестовых входных комбинаций сигналов. Верификацию схемы производят по так называемым временным диаграммам. Преимущество временных диаграмм перед таблицами истинности в том, что они кроме логических значений могут отображать временные задержки прохождения сигнала.

При синтезе из текстового описания на высокоуровневом языке получают цифровую схему устройства из элементарных модулей (логических вентилей, триггеров, сумматоров и т.д.). Во время синтеза обычно выполняется оптимизация для исключения дополнительных затрат. Полученную схему называют RTL (registr transfer leval) уровнем описания аппаратуры. Из RTL уровня можно получить технологические схемы изготовления кристалла интегральной схемы или прошивку ПЛИС.

Цифровые шины

В реальных схемах число сигнальных линий может достигать нескольких сотен. ( Например в графических картах могут применяться для передачи данных одновременно 128 или 256 сигнальных линий). Для удобства набор сигнальных линий одного назначения объединяют в шины.

На схеме шины обозначают жирной линией.

Пример: (инвертор на для 4-х битной шины)

При описании в VHDL для обозначения шин используют тип данных STD_LOGIC_VECTOR.

Пример описания модуля инвертора

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity inv is

port (

a: in STD_LOGIC_VECTOR (3 downto 0);

y: out STD_LOGIC_VECTOR (3 downto 0)

);

end;

architecture synth of inv is

begin

y <= not a;

end;

Здесь каждая сигнальная линия имеет свой индекс начиная от 0 до 3. Есть возможность описать начальный не нулевой индекс. Эту возможность удобно применить кода требуется одну большую шину разбить на несколько мелких.

Например

х: in STD_LOGIC_VECTOR (7 downto 3);

Над каждой сигнальной линей шины можно производить отдельные операции. Доступ к конкретному проводнику шины в VHDL коде выполняется через индекс. Индекс указывается в круглых скобках.

Пример – пусть надо описать модуль выполняющий логическое И над всеми линиями 8-битной шины:

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity and8 is

port (a: in STD_LOGIC_VECTOR (7 downto 0);

y: out STD_LOGIC);

end;

architecture synth of and8 is

begin

y <= a(7) and a(6) and a(5) and a(4) and a(3) and a(2) and a(1) and a(0);

end;

Синтезированная схема:

Чтобы объединить несколько сигналов в одну шину следует использовать оператор амперсанд &. Чтобы выделить часть сигналов из шины следует поставить круглые скобки, указав диапазон индексов, указывающим сигналы шины.

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity m2 is

Port ( x : in STD_LOGIC_VECTOR (7 downto 0);

y : out STD_LOGIC_VECTOR (7 downto 0));

end m2;

architecture Behavioral of m2 is

signal tmp:STD_LOGIC;

begin

tmp <=not(x(0) and x(1) and x(2) and not x(3));

y<=tmp & x(7 downto 1);

end Behavioral;