Design and characterization of flexible circuit for disk drive application

.pdf

Creating and Exporting Spice

Equivalent Circuits

Lumped vs Distributed Systems

Effective Length of electrical feature(rising edge) L = Tr / Delay

General rule of thumb : Circuits < L/6 are lumped TDR rise time = 35ps

Lumped Equivalent Circuit - Cells

To accurately model each flex section as a lumped equivalent, for each cell = Tr / Td > 20

Schematic and Spice Simulation

Step Source (TDR)

Tr=35ps

Pre-amp Body

Swage Plate |

Gimbal |

Termination |

|

|

Impedance Profile of FOS

Incident Step

Td

|

|

|

|

|

|

|

TDR |

|

|

DISCONTINUITY |

|

|

LOAD |

|

|

|

|

|||

|

|

|

|

|

|

|

Td Time Reference & Probe position

Td Time Reference & Probe position

Reflected pulse

Time scale for the impedance profile shows propagation time to discontinuity and back = round trip time

Total simulation time span = 2 x (Td to Load)

Shown by OC and SC termination results

Impedance Profile of FOS

TDR Measurement of FSA

|

140 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

120 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(ohms) |

100 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

80 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Impedance |

60 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

40 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

FSA1 Write |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

20 |

|

|

|

|

|

|

|

|

|

|

|

|

FSA2 Write |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

16 |

31 |

46 |

61 |

76 |

91 |

106 |

121 |

136 |

151 |

166 |

181 |

196 |

211 |

226 |

241 |

Time (ps)

TDR measurements showing single trip time

HGA Cross Section Investigations

Ansoft SI 2D Parametric Sweeps

|

|

|

|

Zdiff |

|

|

|

|

|

1.000E+02 |

|

|

|

|

|

|

|

|

9.000E+01 |

|

|

|

|

|

|

|

(ohms) |

8.000E+01 |

|

|

|

|

|

|

|

7.000E+01 |

|

|

|

|

|

|

|

|

6.000E+01 |

|

|

|

|

|

|

|

|

Impedance |

5.000E+01 |

|

|

|

|

|

|

|

4.000E+01 |

|

|

|

|

|

|

|

|

3.000E+01 |

|

|

|

|

|

|

|

|

2.000E+01 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1.000E+01 |

|

|

|

|

|

Zdiff |

|

|

0.000E+00 |

|

|

|

|

|

|

|

|

0.00E+ 2.00E- 4.00E- 6.00E- 8.00E- 1.00E- 1.20E- 1.40E- |

|||||||

|

00 |

02 |

02 |

02 |

02 |

01 |

01 |

01 |

Width (um)

Trace Width Variation

Parametric Sweeps in Ansoft SI2DStudy impedance changes with variations in trace spacing, widths, thickness in seconds

Zdiff

|

1.200E+02 |

|

|

|

|

|

|

(ohms) |

1.000E+02 |

|

|

|

|

|

|

8.000E+01 |

|

|

|

|

|

|

|

Impedance |

|

|

|

|

|

|

|

6.000E+01 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4.000E+01 |

|

|

|

|

|

|

|

2.000E+01 |

|

|

|

|

|

|

|

0.000E+00 |

|

|

|

|

Zdiff |

|

|

|

|

|

|

|

|

|

|

0.00E+0 |

5.00E- |

1.00E- |

1.50E- |

2.00E- |

2.50E- |

3.00E- |

|

0 |

03 |

02 |

02 |

02 |

02 |

02 |

Spacing (um)

Trace Spacing Variation

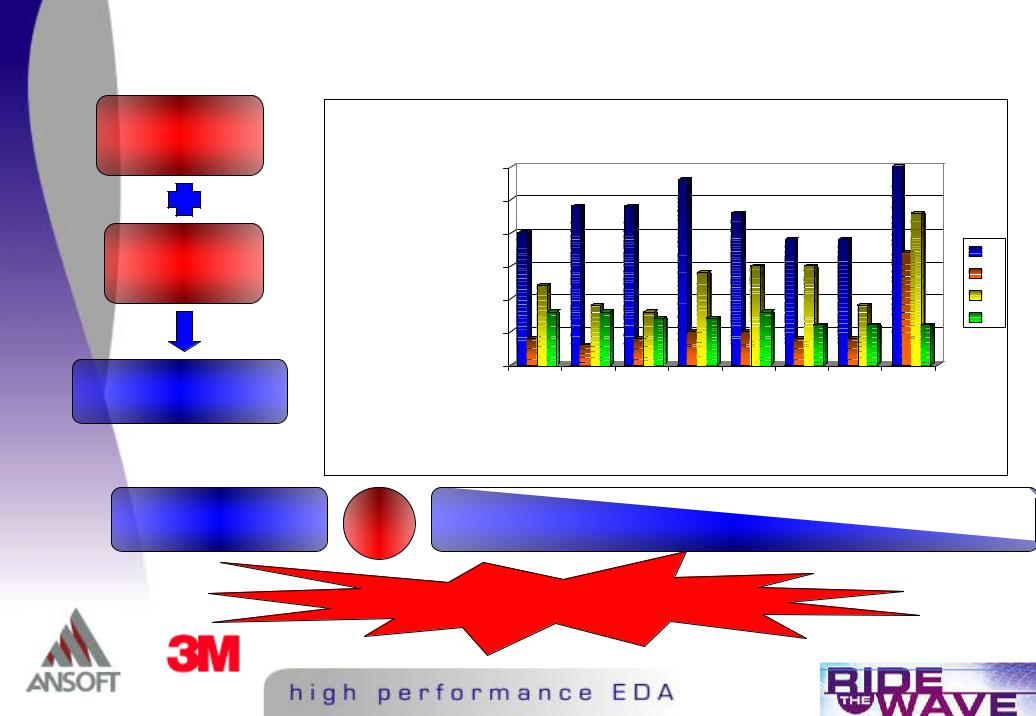

Crosstalk Analysis

Crosstalk analysis are performed using Ansoft Q3D and schematic Capture to investigate the coupling between the Read and Write channels in the FSA

The coupling is especially evident in the ‘body’ region of the flex where the Read and Write Trace are closely spaced.

Q3D Extraction |

Spice Equivalent |

Schematic Capture |

Circuit |

The rise time of the differential signal is at 300ps during typical read/write cycle

The source pulse waveforms used in Spice Simulation

Crosstalk Analysis

"Writer Crosstalk to the Read circuit is of a concern

"A Read typical biased at 5mA, tolerate MAXIMUM continuous current = 10mA "For a 50ohm Read circuit, bias voltage = 5mA x 50ohm = 250mV

"This gives a margin of 250mV beyond which the GMR head will be damaged.

Waveform from Spice

Crosstalk less than 250mV

Simulation Time vs Prototype Test

SI2D Total

Time

394s

SPICE

SIMULATION 4s

TOTAL 6min 37s Approx

Simulation Time for each 2D Project |

|

|

30 |

|

|

25 |

|

|

20 |

C |

|

Time (s) 15 |

||

L |

||

10 |

Z |

|

Y |

||

|

5 |

0 |

af amp |

ccns |

nccns |

|

|

|

|

amp c |

nccws2 |

nccwsad |

ccwsad |

nccwsa |

2D Project Name

With Modeling Time |

VS |

5 to 6 weeks to run another prototype |

3-4 DAYS |

(From Flex Circuit manufacturing to Assembly into a HGA |

TIME SAVING BY 90%

Summary

!The use of Ansoft EDA tools in the design and Characterization of Flex Suspension Assembly have achieved major objectives of :

!Decreasing the number of prototype and test iterations

!Setting of design rules and early detection of electrical design faults through simulation

!Greatly decrease the overall design cycle time and achieved faster time to market

References

!Howard W Johnson, Martin Graham, High Speed Digital Design:A Handbook of Black Magic (Prentice Hall PTR,1993)

!Robert Dodsworth, George Hare, HGA Technology Driver - The need for Speed With Control, 3M Pte Ltd

!Eric Jensen, Mike Resso, Dima Smolyansky, Laurie Taira-Griffin, Improved Method for Characterizing and Modeling Gigabit Flex-Circuit Based Interconnects (DesignCon 2001)