- •Lection №2 Флэш-память

- •Outline

- •Какая память бывает?

- •Флэшка: взгляд снаружи

- •СЭМ-снимок

- •Стирание и запись

- •Уравнение Фаулера — Нордхейма

- •Запись

- •Инжекция горячих электронов

- •Двухтранзисторная ячейка памяти

- •Двухтранзисторная ячейка памяти

- •Multi-Level Cells

- •Что дальше?

- •Перспективы

- •Принцип действия: NOR архитектуры

- •NOR архитектура

- •Принцип действия

- •Принцип действия: NAND

- •NAND архитектура

- •Размер ячейки, страницы, блока NAND-памяти

- •Специальные алгоритмы

- •Специальные алгоритмы

- •Алгоритм удаления

- •Адресация

- •Адресация

- •Адресация

- ••Physics Faculty, Electronic Computing Devices & Systems, 6th semester,2011 Dr. Mokhovikov Alexander Yurievich

- ••Physics Faculty, Electronic Computing Devices & Systems, 6th semester,2011 Dr. Mokhovikov Alexander Yurievich

- •http://hengooru.blogspot.com/2010/05/flash-1.html http://kit-e.ru/articles/memory/2009_10_33.php http://www.gliffer.ru/articles/elektronika-dlya-nachinayushchih--vzglyad-iznutri-flash-pamyat-i-ram/ http://www.ixbt.com/storage/flash-tech.shtml

- •Используемые Интернет-ресурсы:

- •литература:

Двухтранзисторная ячейка памяти

Преимущества двухтранзисторной ячейки памяти:

можно создавать более компактные и хорошо масштабируемые микросхемы памяти, поскольку в данном случае транзистор с плавающим затвором изолируется от битовой линии.

Кроме того, в отличие от однотранзисторной ячейки памяти, где для записи информации используется метод инжекции горячих электронов, в данном случае и для записи, и для стирания информации применяется метод квантового туннелирования Фаулера-Нордхейма, что позволяет снизить напряжение, необходимое для операции записи.

Двухтранзисторные ячейки используются в памяти с архитектурой NAND

•Physics Faculty, Electronic Computing Devices & Systems, 6th semester,2011 Dr. Mokhovikov Alexander Yurievich

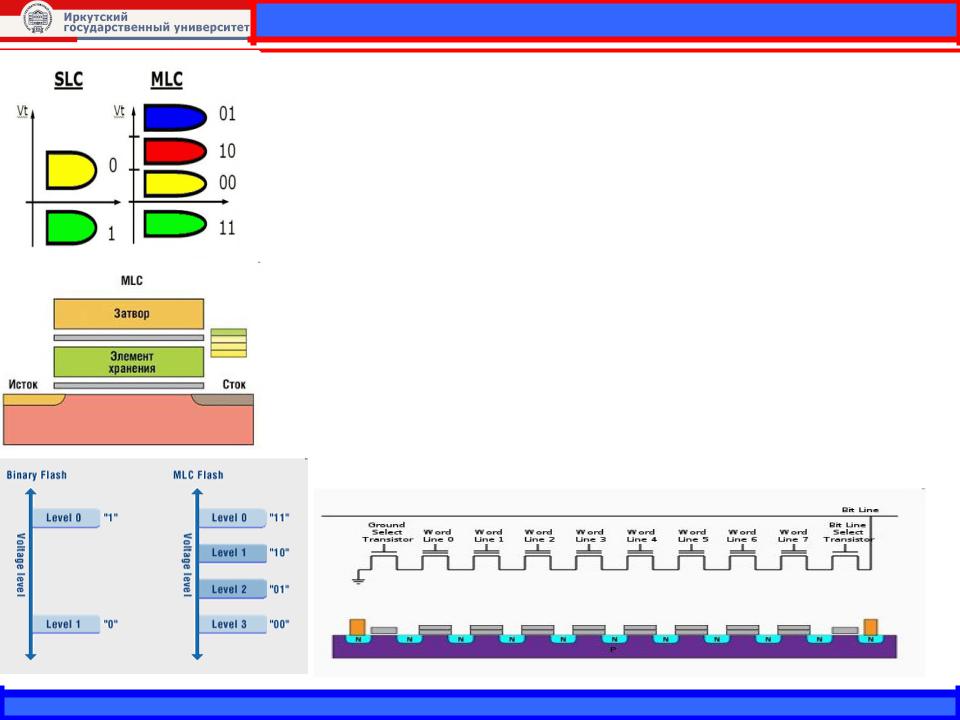

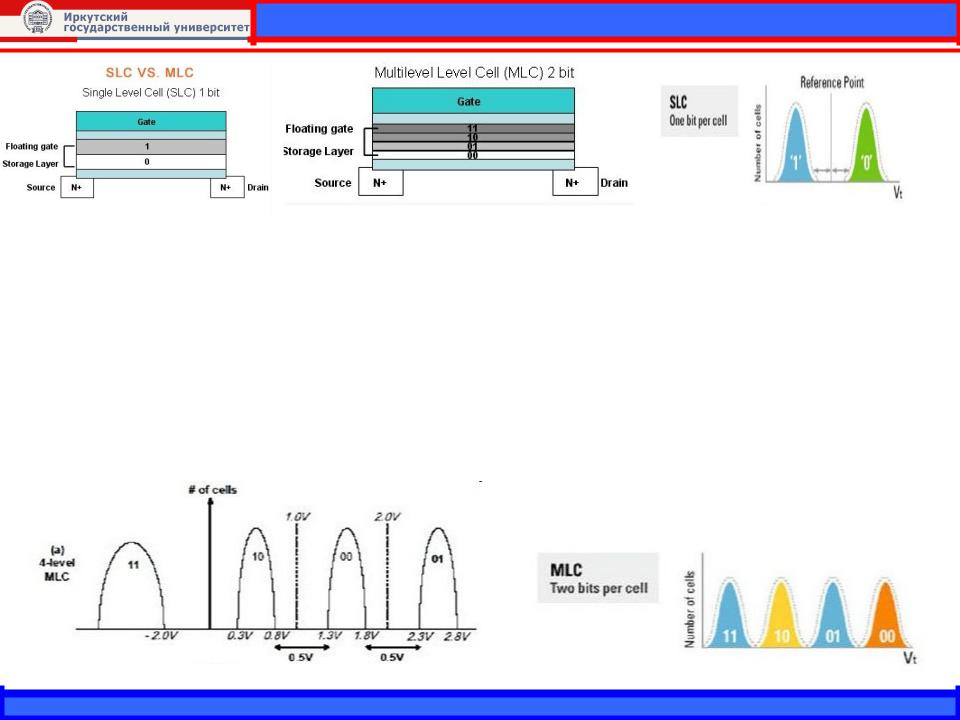

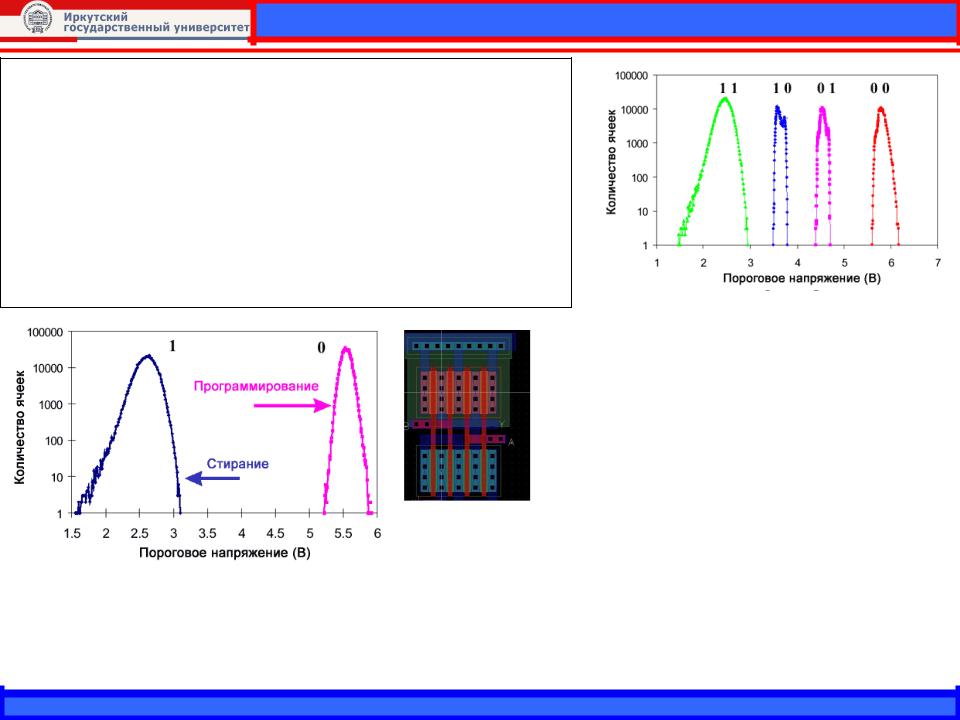

Multi-Level Cells

Технология MLC позволяет за счет наращивания уровней существенно увеличить объем диска, оставив его физические размеры неизменными, что уменьшает себестоимость каждого гигабайта.

На этом положительные качества данной технологии заканчиваются. С каждым дополнительным уровнем усложняется задача распознавания уровня сигнала, не говоря уже об уменьшении ресурса работы

Более сложная организация MLC памяти достигается путем изменения типа заряда подаваемого на каждую ячейку и его оценки.

Увеличение количества уровней приводит к увеличению количества необходимого вида заряда и его распознавания с каждого уровня.

•Physics Faculty, Electronic Computing Devices & Systems, 6th semester,2011 Dr. Mokhovikov Alexander Yurievich

MLC

Любая запись или удаление информации сопровождается перетеканием электроном. В одном поле электроны удерживаются благодаря их перетеканию через слои специального диэлектрика, а само перетекание осуществляется с помощью электромагнитных полей, создаваемых транзистором.

Именно данный слой диэлектрика, является еще одним слабым местом памяти для твердотельных накопителей. В процессе записи и удаления информации данный слой диэлектрика разрушается, и компенсировать данное состояние возможно только путем изменения напряжения подаваемого сигнала.

•Physics Faculty, Electronic Computing Devices & Systems, 6th semester,2011 Dr. Mokhovikov Alexander Yurievich

SLC vs MLC

Сравнительная таблица |

SLC |

MLC |

основных характеристик |

||

Чтение страницы, мкс |

25 |

50 |

Стирание блока, мс |

2 |

2 |

Запись страницы, мкс |

250 |

900 |

Количество циклов, |

1 000 000 |

100 000 |

раз |

|

|

Стертые ячейки (логическая "1") имели порог 3.1В, в то время как запрограммированные (логический "0") имели пороговое напряжение более 5В.

После стирания или точного программирования одного из трех состояний (трех, потому что одно состояние получается при стирании) были измерены величины пороговых напряжений и результаты помещены в виде гистограммы на рисунок. Заметим, что точное управление зарядом позволило двум средним состояниям сузить разброс напряжений до 0.3В, что соответствует 3000 электронов.

•Physics Faculty, Electronic Computing Devices & Systems, 6th semester,2011 Dr. Mokhovikov Alexander Yurievich

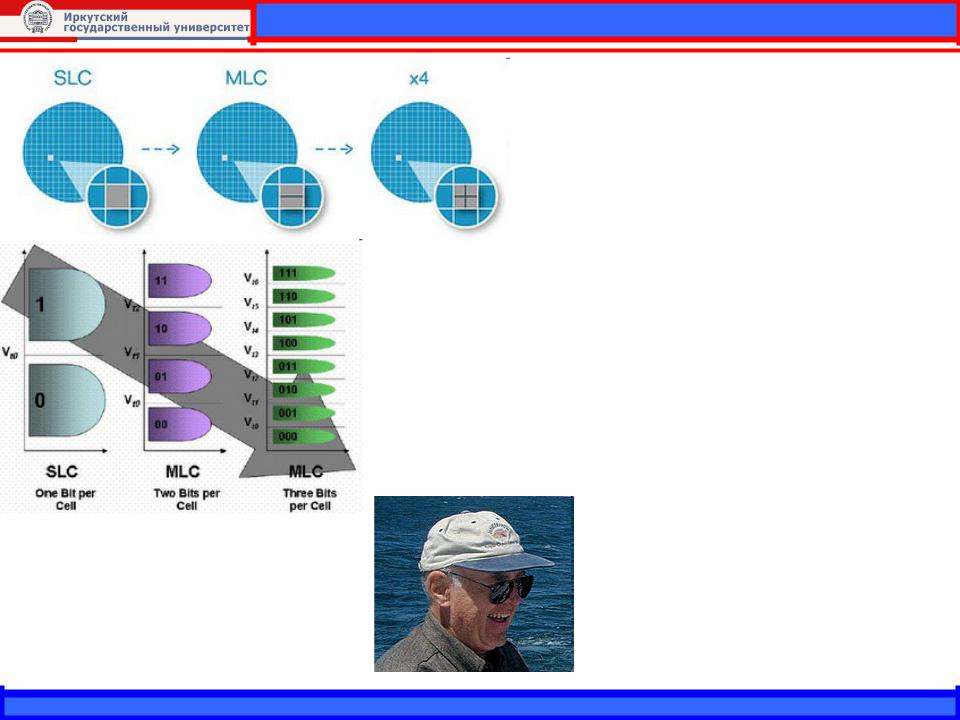

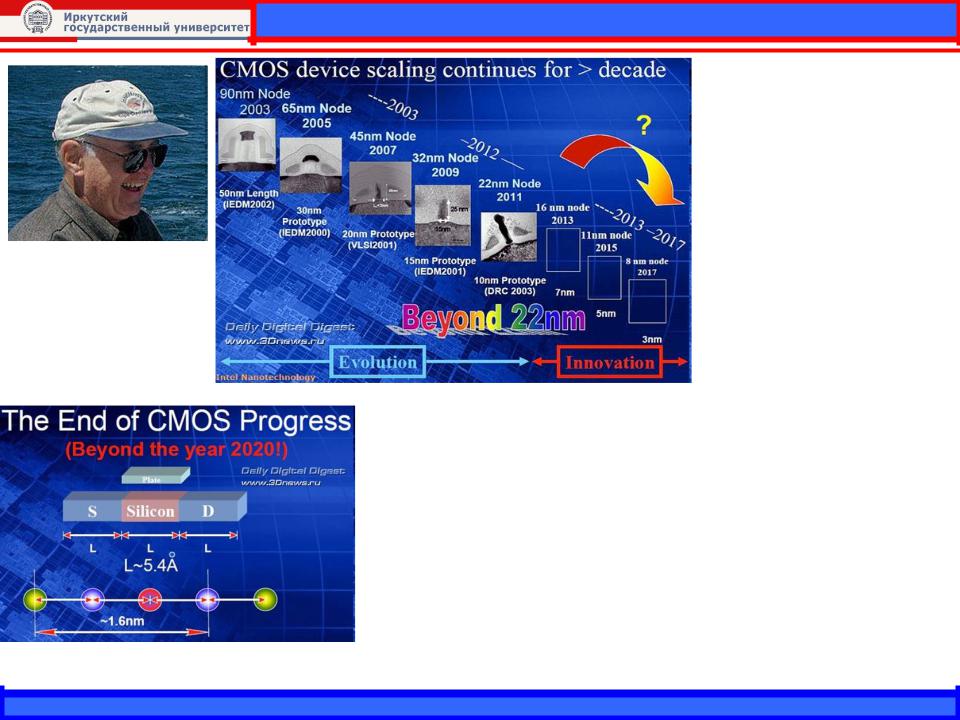

Что дальше?

Суть технологии, которая позволяет записывать сразу 4 бита в одну ячейку памяти, а не 1-2 бит, как раньше.

Закон Мура — эмпирическое наблюдение, изначально сделанное Гордоном Муром, согласно которому (в современной формулировке) количество транзисторов, размещаемых на кристалле интегральной схемы, удваивается каждые 18 месяцев.

Почётный председатель совета директоров и основатель корпорации Intel Сейчас ему 83 года (3 января 1929)

•Physics Faculty, Electronic Computing Devices & Systems, 6th semester,2011 Dr. Mokhovikov Alexander Yurievich

Перспективы

А дальше наступит физический предел даже для "идеального" транзистора, функционирующего в совершенно идеальных условиях. Ибо при таких масштабах приходится оперировать с габаритами отдельных атомов и где классические приёмы уже не дают никакой гарантии стабильной работы, тем более в масштабе миллиардов электронных ключей чипа.

•Physics Faculty, Electronic Computing Devices & Systems, 6th semester,2011 Dr. Mokhovikov Alexander Yurievich

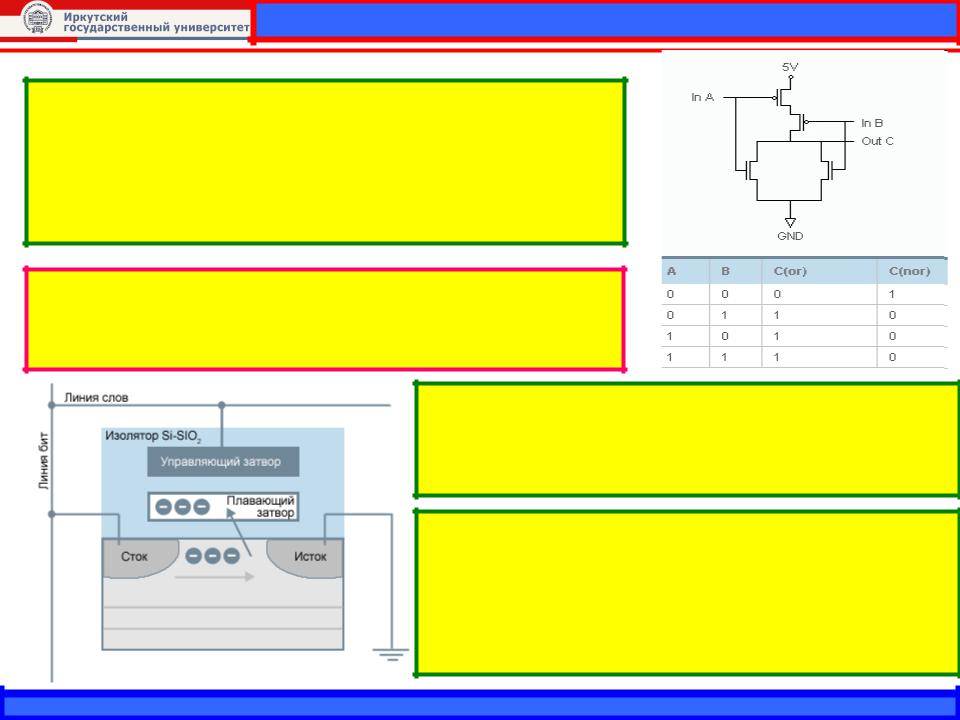

Принцип действия: NOR архитектуры

Поскольку память с такой организацией считается первой представительницей семейства Flash, с нее и начнем.

Схема логического элемента, собственно давшего ей название (NOR — Not OR — в булевой математике обозначает отрицание «ИЛИ»)

С помощью нее осуществляется преобразование входных напряжений в выходные, соответствующие «0» и «1». Они необходимы, потому что для чтения/записи данных в ячейке памяти используются различные напряжения.

Она характерна для большинства флэш-чипов и представляет из себя транзистор с двумя изолированными затворами: управляющим (control) и плавающим (floating).

Важной особенностью последнего является способность удерживать электроны, то есть заряд. Также в ячейке имеются так называемые «сток» и «исток». При программировании между ними, вследствие воздействия положительного поля на управляющем затворе, создается канал — поток электронов.

•Physics Faculty, Electronic Computing Devices & Systems, 6th semester,2011 Dr. Mokhovikov Alexander Yurievich

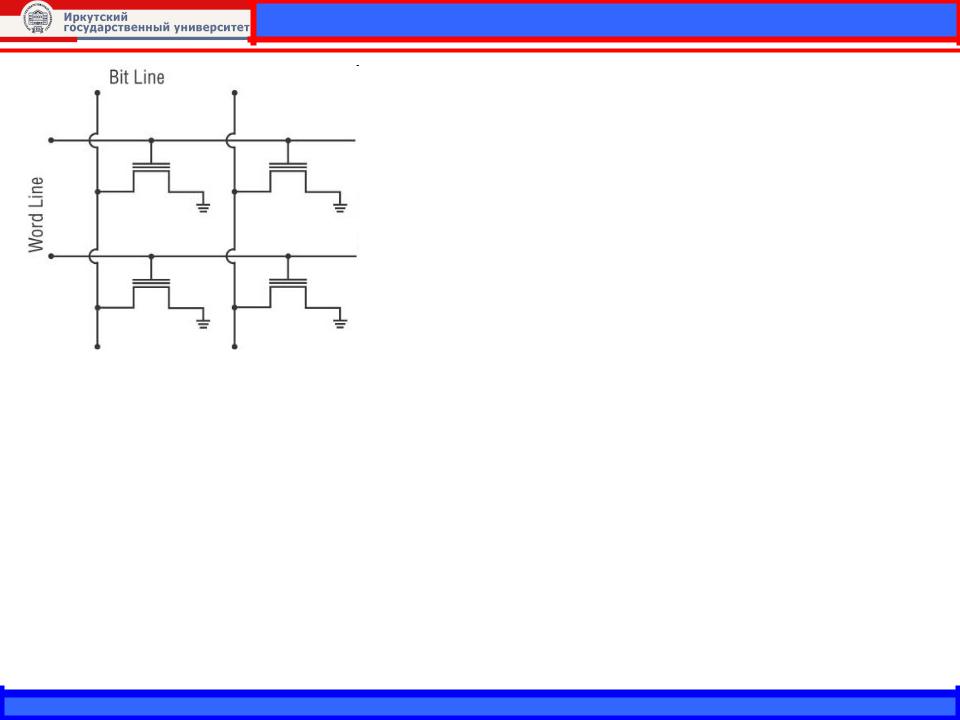

NOR архитектура

Для инициализации ячейки памяти, то есть для получения доступа к содержимому ячейки, необходимо подать напряжение на управляющий затвор. Поэтому все управляющие затворы должны быть подсоединены к линии управления, называемой линией слов (Word Line). Анализ содержимого ячейки памяти производится по уровню сигнала на стоке транзистора. Поэтому стоки транзисторов подключаются к линии, называемой линией битов (Bit Line).

Логическая операция NOR над несколькими операндами дает единичное значение, когда все операнды равны нулю, и нулевое значение во всех остальных случаях. Если под операндами понимать значения ячеек памяти, то в рассмотренной архитектуре единичное значение на битовой линии будет наблюдаться только в том

случае, когда значение всех ячеек, подключенных к данной битовой линии, равно нулю (все транзисторы закрыты).

•Physics Faculty, Electronic Computing Devices & Systems, 6th semester,2011 Dr. Mokhovikov Alexander Yurievich

Принцип действия

Некоторые из электронов, благодаря наличию большей энергии, преодолевают слой изолятора и попадают на плавающий затвор, где могут храниться в течение нескольких лет.

Определенный диапазон количества электронов (заряда) на плавающем затворе соответствует логической единице, а все, что больше его, — нулю.

При чтении эти состояния распознаются путем измерения порогового напряжения транзистора.

Для стирания информации на управляющий затвор подается высокое отрицательное напряжение, и электроны с плавающего затвора переходят (туннелируют) на исток.

В технологиях различных производителей этот принцип работы может отличаться по способу подачи тока и чтению данных из ячейки.

Для хранения 1 бита информации задействуется только один элемент (транзистор), в то время как в энергозависимых типах памяти для этого требуется несколько транзисторов и конденсатор.

•Physics Faculty, Electronic Computing Devices & Systems, 6th semester,2011 Dr. Mokhovikov Alexander Yurievich

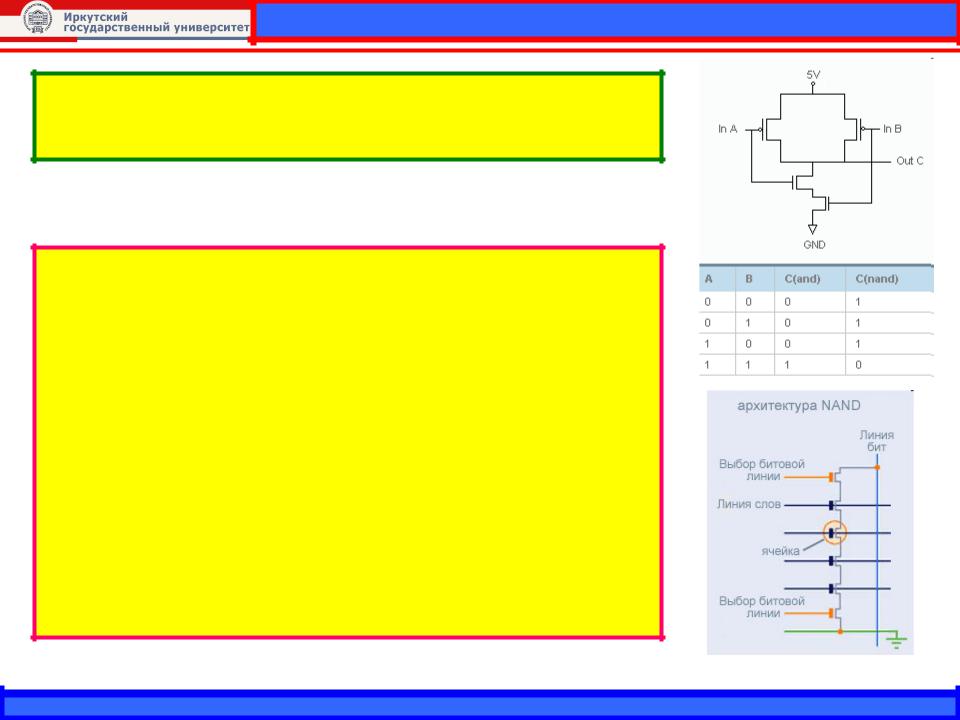

Принцип действия: NAND

NAND — Not AND — в той же булевой математике обозначает отрицание «И». Отличается такая память от предыдущей разве что логической схемой.

Устройство и принцип работы ячеек у нее такой же, как и у NOR.

Хотя, кроме логики, все-таки есть еще одно важное отличие — архитектура размещения ячеек и их контактов.

В отличие от вышеописанного случая, здесь имеется контактная матрица, в пересечениях строк и столбцов которой располагаются транзисторы.

Это сравнимо с пассивной матрицей в дисплеях (а NOR — с активной TFT).

В случае с памятью такая организация несколько лучше — площадь микросхемы можно значительно уменьшить за счет размеров ячеек.

Недостатки заключаются в более низкой по сравнению с NOR скорости работы в операциях побайтового произвольного доступа.

•Physics Faculty, Electronic Computing Devices & Systems, 6th semester,2011 Dr. Mokhovikov Alexander Yurievich