- •Материалы для студента

- •§ 8.2. Теоретические вопросы Модуля 8

- •§ 8.3. Задание Модуля 8

- •§ 8.4. Варианты схем к заданию Модуля 8

- •§ 8.5. Компьютерное моделирование №1 к заданию Модуля 8

- •§ 8.6. Краткая теория и примеры Модуля 8

- •Особенности построения логических устройств

- •Комбинационные логические схемы

- •Последовательностные цифровые устройства: триггер, счетчики импульсов, регистры

- •Цифровые запоминающие устройства

- •Программируемые логические интегральные схемы

- •§ 8.7. Примеры тестов

Программируемые логические интегральные схемы

Изготовление заказных больших и сверхбольших интегральных схем (БИС, СБИС) это длительный и дорогостоящий процесс. Решение проблемы найдено через создание универсальных логических устройств большой степени интеграции, алгоритмы которых задаются разработчиком (ПЛИС).

Программируемые управляющие устройства нашли широкое применение в системах управления различными технологическими процессами, совокупность арифметико-логического устройства, регистров общего назначения, устройств запоминающих, устройств ввода-вывода и др. реализуется в виде отдельных или общих микросхемах. Мозгом микропроцессоров является арифметико-логическое устройство, которое представляет собой логический комбинационный автомат. Основное назначение АЛУ заключается в приеме данных, хранящихся в памяти, и осуществление над ними арифметических и логических операций под действием устройства управления. Схема АЛУ содержит комбинационные логические устройства, генераторы логических функций, сумматоры и полусумматоры.

§ 8.7. Примеры тестов

1. Число 110112 в десятичной системе исчисления

2.Число 111002 в десятичной системе исчисления

3.Число 1410 в двоичной системе исчисления

4.Число 1210 в двоичной системе исчисления

5. В двоичной системе исчисления сумма двух чисел 11012+1410 (пять бит)

6. В двоичной системе исчисления сумма двух чисел 11112+1510 (пять бит)

7.В двоичной системе исчисления сумма двух чисел 11112+1610 (пять бит)

8. В десятичной системе исчисления разность двух чисел 110102 - 001102

9. В десятичной системе исчисления разность двух чисел 110102 - 001112

10. Результат перемножения двух числе в двоичной системе исчисления 11112и 210 (пять бит)

11. Результат перемножения двух числе в двоичной системе исчисления 11012и 210 (пять бит)

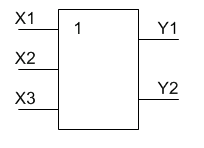

12. Уровень сигнала на выходе Y1 при подаче на вход схемы сигналов с логическими уровнями

X1=1

X2=1

X3=1

13. Логический уровень сигнала на выходеY1 при подаче на вход схемы сигналов с логическими уровнями

X1=0

X2=0

X3=1

14. Логический уровень сигнала на выходе Y2 при подаче на вход схемы сигналов с логическими уровнями

X1=1

X2=1

X3=1

-15. Логический уровень сигнала на выходе Y1 при подаче на вход схемы сигналов с логическими уровнями

X1=1

X2=1

X3=1

-16. Логический уровень сигнала на выходе Y1 при подаче на вход схемы сигналов с логическими уровнями

X1=0

X2=0

X3=1

17. Логический уровень сигнала на выходе Y1 при подаче на вход схемы сигналов с логическими уровнями

X1=1

X2=0

X3=1

17. Логический уровень сигнала на выходе Y1 при подаче на вход схемы сигналов с логическими уровнями, если выходные сигналы описаны уравнением:

![]()

![]()

X1=1

X2=1

X3=1

18. Логический уровень сигнала на выходе Y1 при подаче на вход схемы сигналов с логическими уровнями, если выходные сигналы описаны уравнением:

![]()

![]()

X1=0

X2=0

X3=1

19. Логический уровень сигнала на выходе Y1 при подаче на вход схемы сигналов с логическими уровнями, если выходные сигналы описаны уравнением:

![]()

![]()

X1=1

X2=0

X3=1

20. Логический уровень сигнала на выходе Y1 при подаче на вход схемы сигналов с логическими уровнями, если выходные сигналы описаны уравнением:

![]()

![]()

X1=1

X2=1

X3=1

21. Логический уровень сигнала на выходе Y1 при подаче на вход схемы сигналов с логическими уровнями, если выходные сигналы описаны уравнением:

![]()

![]()

X1=0

X2=0

X3=1

22. Логический уровень сигнала на выходе Y1 при подаче на вход схемы сигналов с логическими уровнями, если выходные сигналы описаны уравнением:

![]()

![]()

X1=1

X2=0

X3=1