- •Оглавление

- •5.15 Обзор регистров dma-контроллера 51

- •13.15 Описание регистров мультипортовой конфигурации 118

- •14.13 Обзор регистров 140

- •15.8 Обзор регистров 150

- •17.4 Обзор регистров 157

- •18.4 Обзор регистров 162

- •25.16 Описание регистра канала ацп 248

- •27 Аналоговый компаратор ac 263

- •33.11 Блок sdram 321

- •Рекомендации по чтению руководства

- •Ресурсы

- •Рекомендовано для прочтения

- •Функциональная схема

- •Отличительные особенности

- •Обзор архитектуры

- •Арифметико-логическое устройство

- •Аппаратное умножающее устройство

- •Программный поток

- •Временная диаграмма выполнения инструкций

- •Регистр статуса

- •Стек и указатель стека

- •Регистровый файл

- •Регистры X, y и z

- •Регистры ramp и расширенной косвенной адресации

- •Регистры rampx, rampy и rampz

- •Регистр rampd

- •Регистр расширенной косвенной адресации eind

- •Доступ к 16-битным регистрам

- •Доступ к 24- и 32-битным регистрам

- •Защита от изменения конфигурации

- •Последовательность записи защищенных регистров ввода-вывода

- •Последовательность выполнения защищенных инструкций spm/lpm

- •Fuse-биты для блокировки изменений

- •Описание регистров

- •Регистр защиты от изменения конфигурации ccp

- •Краткий обзор регистров

- •Запоминающие устройства

- •Отличительные особенности

- •Flash-память программ

- •Сектор прикладной программы

- •Сектор таблицы приложения

- •Загрузочный сектор

- •Сигнатурный код производителя и ячейки калибровки

- •Сигнатурный код пользователя

- •Fuse- и Lock-биты

- •Память данных

- •Внутреннее sram

- •Доступ к eeprom в пространстве памяти данных

- •Память ввода-вывода

- •Регистры ввода-вывода общего назначения

- •Внешняя память

- •Память данных и арбитраж шины

- •Шинный приоритет

- •Временные характеристики доступа к памяти

- •Идентификация микроконтроллера

- •Обзор регистров Fuse- и Lock-бит

- •Обзор регистров кода сигнатуры производителя

- •Обзор регистров ввода-вывода общего назначения

- •Обзор регистров управления микроконтроллером

- •Векторы прерываний контроллера энергонезависимой памяти

- •Контроллер прямого доступа к памяти (dma-контроллер)

- •Отличительные особенности

- •Транзакция dma

- •Передача блока и повтор

- •Передача пакета

- •Запуск передачи

- •Адресация

- •Приоритеты каналов

- •Двойная буферизация

- •Передача буферов

- •Обнаружение ошибок

- •Программный сброс

- •Прерывания

- •Описание регистров dma-контроллера

- •Ctrl - регистр управления dma

- •Intflags - регистр статуса прерываний dma

- •Status - Регистр статуса dma

- •Temph - старший байт временного регистра dmtemp

- •Templ - младший байт временного регистра dmtemp

- •Описание регистров dma-канала

- •Ctrla - регистр а управления dma-каналом

- •Ctrlb - регистр b управления dma-каналом

- •Addrctrl - регистр управления адресом dma-канала

- •Trigsrc - источник запуска dma-канала

- •Trfcnth - старший регистр счетчика байт при передаче блока по dma-каналу

- •Trfcntl - младший регистр счетчика байт при передаче блока по dma-каналу

- •Repcnt - регистр счетчика повторов в dma-канале

- •Srcaddr2 - регистр 2 адреса источника dma-канала

- •Srcaddr1 - регистр 1 адреса источника dma-канала

- •Srcaddr0 - регистр 0 адреса источника dma-канала

- •Destaddr2 - регистр 2 адреса получателя dma-канала

- •Destaddr1 - регистр 1 адреса получателя dma-канала

- •Destaddr0 - регистр 0 адреса получателя dma-канала

- •Обзор регистров dma-контроллера

- •Обзор регистров dma-канала

- •Обзор векторов прерываний dma

- •Использование dma микропроцессора Xmega

- •Каналы dma

- •Передача данных

- •Блочная передача и режим повтора

- •Dma посылка

- •Режимы адресации

- •Перезагрузка адреса

- •Запуск передачи и режим однократного запуска

- •Обработка прерываний

- •Доступ контроллера dma к многобайтным регистрам

- •Дополнительные возможности

- •С чего начать

- •Система событий

- •Отличительные особенности

- •События

- •Сигнальные события

- •Информационные события

- •Ручная генерация событий

- •Сеть маршрутизации событий

- •Временные характеристики передачи событий

- •Фильтрация

- •Квадратурный декодер

- •Работа квадратурного декодера

- •Настройка квадратурного декодера

- •Описание регистров

- •CHnMux - регистр мультиплексора канала события n

- •CHnCtrl - Регистр управления каналом события n

- •Strobe - строб-регистр события

- •Data - регистр данных события

- •Обзор регистров

- •Системная синхронизация и источники синхронизации

- •Отличительные особенности

- •Распределение сигналов синхронизации

- •Внутренний генератор частоты 32 мГц с возможностью автоматической калибровки

- •Внутренний генератор частоты 2 мГц с возможностью автоматической калибровки

- •Внешние источники синхронизации

- •Кварцевый генератор частоты 0.4…16 мГц

- •Вход внешней синхронизации

- •Кварцевый генератор частоты 32 кГц

- •Настройка системной синхронизации и предделителей частоты

- •Блок pll с коэффициентом умножения от 1 до 31

- •Блоки dfll 2- и 32-мегагерцевых генераторов

- •Функция обнаружения отказа внешнего источника синхронизации

- •Описание регистров системы синхронизации

- •Обзор регистров генераторов

- •Обзор регистров блоков dfll32m/dfll2m

- •Обзор вектора прерывания при отказе кварцевого генератора

- •Управление энергопотреблением и экономичные режимы

- •Отличительные особенности

- •Экономичные режимы работы

- •Режим idle

- •Описание регистров управления экономичными режимами

- •Ctrl- регистр управления экономичными режимами работы

- •Описание регистров снижения энергопотребления

- •Prgen - общий регистр снижения энергопотребления

- •Prpa/b - регистр снижения энергопотребления порта а/в

- •8.6.3. Prpc/d/e/f - регистр снижения энергопотребления порта c/d/e/f

- •Обзор регистров управления экономичными режимами работы

- •Обзор регистров управления энергопотреблением

- •Система сброса

- •Отличительные особенности

- •Последовательность сброса

- •Счетчик задержки сброса

- •Запуск генератора

- •Калибровка генератора

- •Источники сброса

- •Сброс при подаче питания

- •Супервизор питания

- •Сброс от детектора просадки питания

- •Внешний сброс

- •Сброс сторожевым таймером

- •Программный сброс

- •Сброс через интерфейс программирования и отладки

- •Описание регистров

- •Status - Регистр статуса сброса

- •Ctrl - регистр управления сбросом

- •Обзор регистров

- •Система резервного батарейного питания

- •Отличительные особенности

- •Модуль с резервированием питания

- •Обнаружение подачи питания резервного батарейного питания

- •Супервизор батарейного питания

- •Исчезновение основного питания

- •Основной сброс и последовательность запуска

- •Резервирование питания разрешено

- •Резервирование питания не разрешено и сбой в его работе

- •Описание регистров

- •Ctrl: регистр управления резервированием питания

- •Status: регистр статуса модуля с резервированием питания

- •Backup0: регистр 0 с резервным батарейным питанием

- •Обзор регистров

- •Сторожевой таймер wdt

- •Отличительные особенности

- •Нормальный режим работы

- •Оконный режим работы

- •Синхронизация сторожевого таймера

- •Защита и блокировка конфигурации

- •Описание регистров

- •Ctrl - регистр управления сторожевым таймером

- •Winctrl - регистр управления оконным режимом

- •Status - регистр статуса сторожевого таймера

- •Обзор регистров

- •Прерывания и программируемый многоуровневый контроллер прерываний

- •Отличительные особенности

- •Принцип действия

- •Прерывания

- •Немаскируемые прерывания (nmi)

- •Задержка реагирования на прерывание

- •Уровень прерывания

- •Приоритет прерывания

- •Статическая приоритезация

- •Динамическая приоритезация

- •Перемещение векторов прерываний между сектором прикладной программы и загрузочным сектором

- •Описание регистров

- •Status - регистр статуса pmic-контроллера

- •Intpri - регистр приоритета прерываний pmic Priority Register

- •Ctrl - регистр управления pmic-контроллером

- •Обзор регистров

- •Порты ввода-вывода

- •Отличительные особенности

- •Использование линий ввода-вывода

- •Настройка линий ввода-вывода

- •Двухтактный выход

- •Настройка параметров контроля входа

- •Прерывания порта

- •Генерация событий портом ввода-вывода

- •Альтернативные функции портов

- •Управление скоростью фронтов

- •Вывод синхронизации и событий

- •Мультипортовая конфигурация

- •Виртуальные регистры

- •Описание регистров портов

- •Dirset - регистр установки бит направления

- •Dirclr - регистр сброса бит направления

- •Dirtgl - регистр инвертирования бита направления

- •Outset - регистр установки выходов порта

- •Outclr - регистр сброса выходов порта

- •Outtgl - регистр инвертирования выходов порта

- •Intctrl - регистр управления прерываниями

- •Int0mask - регистр маски прерывания 0

- •Int1mask - регистр маски прерывания 1

- •Intflags - регистр флагов прерывания

- •PiNnCtrl - конфигурационный регистр линии n

- •Описание регистров мультипортовой конфигурации

- •Mpcmask - регистр маски одновременной и одинаковой конфигурации нескольких линий в/в

- •Vpctrla - регистр а управлению связью с виртуальными портами

- •Vpctrlb - регистр в управлению связью с виртуальными портами

- •Clkevout - регистр вывода сигналов событий и синхронизации

- •Описание регистров виртуальных портов

- •Intflags - регистр флагов прерываний

- •Обзор регистров портов

- •Обзор регистров мультипортовой конфигурации

- •Обзор регистров виртуальных портов

- •Обзор векторов прерываний портов ввода-вывода

- •Отличительные особенности

- •Определения

- •Функциональная схема

- •Источники синхронизации и событий

- •Двойная буферизация

- •Работа счетчика

- •Нормальная работа

- •Управляемый событиями режим работы

- •Изменение периода

- •Канал захвата

- •Входной захват

- •Захват частоты

- •Захват длительности импульса

- •Переполнение захвата

- •Канал сравнения

- •Генерация импульсов

- •Генерация частотных сигналов (frq)

- •Генерация шим сигнала в режиме pwm с однонаправленным счетом

- •Генерация шим сигнала в режиме pwm с двунаправленным счетом

- •Вывод сигналов генератора импульсов на линии порта

- •Прерывания и события

- •Поддержка dma

- •Команды таймера-счетчика

- •Описание регистров

- •Ctrla - регистр управления а

- •Ctrlb - регистр управления в

- •Ctrlc - регистр управления c

- •Ctrld - регистр управления d

- •Ctrle - регистр управления e

- •Intctrla - регистр а разрешения прерываний

- •Intctrlb - регистр в разрешения прерываний

- •Ctrlfclr/ctrlfset - сброс/установка регистра управления f

- •Ctrlgclr/ctrlgset - сброс/установка регистра управления g

- •Intflags - регистр флага прерывания

- •Temp - временный регистр для 16-битного доступа

- •Cnth - старший регистр счетчика

- •Cntl - младший регистр счетчика

- •Perh - старший регистр периода

- •Perl - младший регистр периода

- •CCxH - старший регистр n захвата/сравнения

- •CCxL - младший регистр n захвата/сравнения

- •Perbufh - старший буферный регистр периода таймера-счетчика

- •Perbufl - младший буферный регистр периода таймера-счетчика

- •CCxBufh - старший регистр буфера захвата или сравнения х

- •CCxBufl - младший регистр буфера захвата или сравнения X

- •Обзор регистров

- •Обзор векторов прерываний

- •Блок расширения возможностей генерации импульсов aWeX

- •Отличительные особенности

- •Перекрытие порта

- •Генерация паузы неперекрытия

- •Образцовый генератор

- •Защита от повреждения

- •Действия защиты

- •Режимы восстановления нормальной работы

- •Изменение защиты

- •Взаимодействие со встроенной отладочной системой

- •Описание регистров

- •Ctrl - Регистр управления

- •Fdemask - регистр маски событий для обнаружения повреждения

- •Fdctrl - регистр управления обнаружением отказа

- •Status - регистр статуса

- •Dtboth - регистр общего доступа к паузам неперекрытия

- •Dtbothbuf - регистр общего доступа к буферным регистрам пауз неперекрытия

- •Dtls - регистр паузы неперекрытия нижнего уровня

- •Dths - регистр паузы неперекрытия верхнего уровня

- •Dtlsbuf - буферный регистр паузы неперекрытия нижнего уровня

- •Dthsbuf - буферный регистр паузы неперекрытия верхнего уровня

- •Outoven - регистр разрешения перекрытия выходов

- •Обзор регистров

- •Блок расширения разрешающей способности

- •Отличительные особенности:

- •Описание регистров

- •Ctrla - регистр управления а блока Hi-Res

- •Обзор регистров

- •Счетчик реального времени rtc

- •Отличительные особенности

- •Домены синхронизации

- •Прерывания и события

- •Описание регистров

- •Ctrl - регистр управления счетчиком реального времени

- •Status - регистр статуса счетчик реального времени

- •Intctrl - регистр управления прерываниями счетчика реального времени

- •Intflags - регистр флагов прерываний счетчика реального времени

- •Temp - временный регистр счетчика реального времени

- •Cnth - старший регистр счетчика реального времени

- •Cntl - младший регистр счетчика реального времени

- •Perh - старший регистр периода счетчика реального времени

- •Perl - младший регистр периода счетчика реального времени

- •Comph - старший регистр сравнения счетчика реального времени

- •Compl - младший регистр сравнения счетчика реального времени

- •Обзор регистров

- •Обзор векторов прерываний

- •Отличительные особенности

- •Настройка синхронизации

- •Домены синхронизации

- •Домена питания

- •События и прерывания

- •Описание регистров

- •Ctrl - регистр управления

- •Syncctrl - регистр управления/статуса синхронизации

- •Intctrl - регистр управления прерываниями

- •Intflags - регистр флагов прерываний

- •Cnt3 - регистр счетчика 3

- •Cnt2 - регистр счетчика 2

- •Cnt1 - регистр счетчика 1

- •Cnt0 - регистр счетчика 0

- •Per3 - регистр периода 3

- •Per2 - регистр периода 2

- •Per1 - регистр периода 1

- •Per0 - регистр периода 0

- •Comp3 - регистр сравнения 3

- •Comp2 - регистр сравнения 2

- •Comp1 - регистр сравнения 1

- •Comp0 - регистр сравнения 0

- •Обзор регистров

- •Обзор векторов прерываний

- •Двухпроводной интерфейс twi

- •Отличительные особенности

- •Принцип действия шины twi

- •Электрические характеристики

- •Условия start и stop

- •Передача бит

- •Пакет адреса

- •Пакет данных

- •Транзакция

- •Синхронизация и задержка импульсов синхронизации

- •Арбитраж

- •Синхронизация ведущих устройств

- •Логика контроля состояния шины twi

- •Работа ведущего модуля twi

- •Передача пакета адреса

- •Сценарий m1: арбитраж проигран или ошибка во время передачи пакета адреса

- •Сценарий m2: Передача пакета адреса завершена, но он не подтвержден подчиненным устройством

- •Сценарий m3: Завершена передача пакета адреса с равным нулю битом направления

- •Сценарий m4: Завершена передача пакета адреса с равным единице битом направления

- •Передача пакетов данных

- •Прием пакетов данных

- •Работа подчиненного модуля twi

- •Прием пакета адреса

- •Сценарий 1: принят пакета адреса с равным единице битом направления

- •Описание регистров модуля twi

- •Ctrl - общий регистр управления модуля twi

- •Описание регистров ведущего модуля twi

- •Ctrla - регистр управления а ведущего модуля twi

- •Ctrlb - регистр управления в ведущего модуля twi

- •Ctrlc - регистр управления с ведущего модуля twi

- •Status - регистр статуса ведущего устройства

- •Baud - регистр скорости

- •Addr - регистр адреса ведущего модуля twi

- •Data - регистр данных ведущего модуля twi

- •Описание регистров подчиненного модуля twi

- •Ctrla - регистр управления а подчиненного модуля twi

- •Ctrlb - регистр управления в починенным модулем twi

- •Status- регистр статуса подчиненного модуля twi

- •Addr - регистр адреса подчиненного модуля twi

- •Addrmask - регистр маски адреса подчиненного модуля twi

- •Обзор регистров модуля twi

- •Обзор регистров ведущего модуля twi

- •Обзор регистров подчиненного модуля twi

- •Обзор векторов прерываний

- •Последовательный интерфейс spi

- •Отличительные особенности

- •Ведущий режим

- •Подчиненный режим

- •Режимы spi

- •Поддержка dma

- •Описание регистров

- •Ctrl - регистр управления spi

- •Intctrl - регистр управления прерываниями spi

- •Status - регистр статуса модуля spi

- •Data - регистр данных spi

- •Обзор регистров

- •Векторы прерываний модуля spi

- •Модуль usart

- •Отличительные особенности

- •Генерация синхронизации

- •Внутренняя генерация синхронизации дробным генератором скорости

- •Внешняя синхронизация

- •Работа с удвоенной скоростью (clk2x)

- •Синхронный режим

- •Генерация синхронизации для шины spi

- •Форматы посылок

- •Вычисление бита паритета

- •Инициализация usart

- •Отправка данных передатчиком usart

- •Отправка посылок

- •Отключение передатчика

- •Получение данных приемником usart

- •Прием посылок

- •Флаги ошибок приемника

- •Восстановление синхронизации

- •Восстановление данных

- •Рабочий диапазон асинхронного приемника

- •Дробная генерация скорости

- •Работа usart в ведущем spi-совместимом режиме

- •Сравнение режима spi модуля usart с модулем spi

- •Режим мультипроцессорной связи

- •Использование режима мультипроцессорной связи

- •Работа в режиме ircom

- •Поддержка dma

- •Описание регистров

- •Data - регистр ввода-вывода данных модуля usart

- •Status - регистр статуса usart

- •Ctrla - регистр управления а модуля usart

- •Ctrlb - регистр управления в модуля usart

- •Ctrlc - регистр управления с модуля usart

- •Baudctrla - регистр скорости usart

- •Baudctrlb - регистр скорости usart

- •Обзор регистров

- •Описание регистров модуля usart

- •Описание регистров модуля usart, работающего в режиме ведущего интерфейса spi

- •Обзор векторов прерываний

- •Модуль инфракрасной связи ircom

- •Отличительные особенности

- •22.2.1. Фильтрация системы событий

- •Описание регистров

- •Txplctrl - регистр управления длительностью импульса передатчика ircom

- •Rxplctrl - регистр управления длительностью импульса приемника ircom

- •Ctrl - регистр управления ircom

- •Обзор регистров

- •Криптоускорители

- •Отличительные особенности

- •Инструкция des

- •Модуль aes

- •Память ключа и память состояния

- •Поддержка dma

- •Обзор регистров модуля aes

- •Ctrl - регистр управления модулем aes

- •Status - регистр статуса модуля aes

- •State - регистр состояния модуля aes

- •Intctrl - регистр управления прерыванием модуля aes

- •Обзор регистров модуля aes

- •Вектор прерываний модуля aes

- •Интерфейс внешней шины ebi

- •Отличительные особенности

- •Выходы выбора микросхем

- •Базовый адрес

- •Размер адресного пространства

- •Выхода выбора микросхем в качестве адресных линий

- •Настройка линий ввода-вывода

- •Синхронизация ebi

- •Совместная работа со sram

- •Работа без мультиплексирования

- •Мультиплексирование данных с байтом адреса 0

- •Мультиплексирование данных с байтами адреса 0 и 1

- •Совместная работа с sdram

- •Поддерживаемые команды

- •Временная диаграмма

- •Инициализация

- •Регенерация

- •Комбинированное подключение к sram и sdram

- •Временная диаграмма интерфейса ebi

- •Режим sram без мультиплексирования

- •Описание регистров модуля ebi

- •Ctrl - регистр управления модулем ebi

- •Sdramctrla - регистр a управления sdram

- •Refresh - регистр периода регенерации sdram

- •Initdly - регистр задержки инициализации sdram

- •Sdramctrlb - регистр в управления sdram

- •Sdramctrlc - регистр с управления sdram

- •Описание регистров управления выбором микросхем

- •Ctrla - регистр а управления выбором микросхемы

- •Ctrlb (sram) - регистр в управления выбором микросхемы

- •Ctrlb (sdram) - регистр в управления выбором микросхемы

- •Baseaddr - регистр базового адреса выбора микросхемы

- •Обзор регистров модуля ebi

- •Обзор регистров управления выбором микросхем

- •Аналогово-цифровой преобразователь adc

- •Отличительные особенности

- •Входные источники

- •Дифференциальный вход

- •Дифференциальный вход с усилением

- •Несимметричный вход

- •Внутренние входы

- •Каналы ацп

- •Выбор опорного напряжения

- •Результат преобразования

- •Функция сравнения

- •Запуск преобразования

- •Синхронизация и временная диаграмма преобразования ацп

- •Одиночное преобразование без усиления

- •Одиночное преобразование с усилением

- •Одиночные преобразования в двух каналах ацп

- •Одиночные преобразования в двух каналах ацп с усилением в канале 0

- •Одиночные преобразования в двух каналах ацп с усилением в канале 1

- •Автоматический режим с усилением в двух каналах ацп

- •Прерывания и события

- •Калибровка

- •Приоритет каналов

- •Синхронизация выборок

- •Описание регистров модуля ацп

- •Ctrla - регистр управления а модуля ацп

- •Ctrlb - регистр управления в модуля ацп

- •Refctrl - регистр управления опорным напряжением ацп

- •Evctrl - регистр управления событиями ацп

- •Prescaler - регистр предделителя синхронизации ацп

- •Intflags - регистр флагов прерываний ацп

- •Temp - временный регистр ацп

- •Call - регистр младшего байта калибровочного значения ацп

- •Calh - регистр старшего байта калибровочного значения ацп

- •CHnResh - старший регистр результата канала ацп n

- •CHnResl - младший регистр результата канала ацп n

- •Cmph - старший регистр сравнения модуля ацп

- •Cmpl - младший регистр сравнения модуля ацп

- •Описание регистра канала ацп

- •Ctrl - регистр управления канала ацп

- •Muxctrl - регистры управления мультиплексором канала ацп

- •Intctrl - регистры управления прерыванием канала ацп

- •Intflag - регистр флагов прерываний канала ацп

- •Resh - старший регистр результата канала ацп n

- •Resl - младший регистр результата канала ацп n

- •Обзор регистров ацп

- •Обзор регистров канала ацп

- •Обзор векторов прерываний

- •Цифро-аналоговый преобразователь dac

- •Отличительные особенности

- •Запуск преобразования

- •Выходные каналы

- •Синхронизация модуля dac

- •Ограничения к временным характеристикам

- •Экономичный режим работы

- •Калибровка

- •Описание регистров

- •Ctrla - регистр а управления модулем dac

- •Ctrlb - регистр в управления модулем dac

- •Ctrlc - регистр с управления цап

- •Evctrl - регистр управления событиями

- •Timctrl - регистр задания временных характеристик цап

- •Status - регистр статуса цап

- •Ch0datah - старший регистр данных канала цап 0

- •Правое выравнивание

- •Левое выравнивание

- •Ch0datal - младший регистр данных канала цап 0

- •Правое выравнивание

- •Левое выравнивание

- •Ch1datah - старший регистр данных канала цап 1

- •Правое выравнивание

- •Левое выравнивание

- •Ch1datal - младший регистр данных канала цап 1

- •Правое выравнивание

- •Левое выравнивание

- •Gaincal - регистр калибровки коэффициента передачи цап

- •Offsetcal - регистр калибровки смещения цап

- •Аналоговый компаратор ac

- •Отличительные особенности

- •Входные каналы

- •ACnMuxctrl - регистр управления мультиплексором аналогового компаратора n

- •Ctrla - регистр управления а

- •Ctrlb - регистр управления в

- •Winctrl - регистр управления оконным режимом аналоговых компараторов

- •Status - общий регистр статуса аналоговых компараторов

- •Обзор регистров

- •Обзор векторов прерываний

- •Ieee 1149.1-совместимый интерфейс jtag

- •Отличительные особенности

- •Jtag-инструкции

- •Регистры данных

- •Сканирование линий ввода-вывода

- •Сканирование линий pdi

- •Интерфейс программирования и отладки pdi

- •Отличительные особенности

- •Трансивер pdi

- •Разрешение работы

- •Отключение

- •Формат посылки и символы

- •Символы

- •Последовательные передача и прием

- •Последовательная передача данных

- •29.3.5.1. Обнаружение конфликтов управления и коллизий

- •Последовательный прием

- •Обнаружение символа break

- •Изменение направления

- •Трансивер jtag

- •Разрешение работы

- •Отключение

- •Набор инструкций jtag

- •Инструкция pdicom

- •Формат посылки и символов

- •Специальные символы данных

- •Последовательные передача и прием

- •Последовательная передача

- •Сигнализация статуса

- •Последовательный прием

- •Проверка паритета

- •Обнаружение символа break

- •Контроллер pdi

- •Переключение между режимами pdi и jtag

- •Доступ к внутренним интерфейсам

- •Ключ программирования энергонезависимой памяти

- •Обработка исключительных ситуаций

- •Управление сбросом

- •Набор инструкций

- •Ldcs - загрузка данных из пространства регистров управления и статуса pdi

- •Stcs - сохранение данных в пространстве регистров управления и статуса pdi

- •Repeat - настройка счетчика повтора инструкций

- •Обзор набора инструкций

- •Описание регистров инструкции и адресации интерфейса pdi

- •Регистр инструкции

- •Регистр указателя

- •Регистр счетчика повторов

- •Регистр счетчика операндов

- •Описание регистров управления и статуса интерфейса pdi

- •Status - регистр статуса интерфейса pdi

- •Reset - регистр сброса

- •Ctrl - регистр управления интерфейсом pdi

- •Обзор регистров

- •Программирование запоминающих устройств

- •Отличительные особенности

- •Команды с запуском по действию

- •Страничные буферы Flash-памяти и eeprom

- •Страничный буфер Flash-памяти

- •Страничный буфер eeprom

- •Последовательности программирования Flash-памяти и eeprom

- •Последовательность программирования Flash-памяти

- •Последовательность программирования eeprom

- •Защита энергонезависимой памяти

- •Предотвращение нарушения данных

- •Сбои во время записи

- •Сбои во время чтения

- •Проверка crc

- •Самопрограммирование под управлением программы загрузчика

- •Программирование Flash-памяти

- •Сектор прикладной программы и загрузочный сектор

- •Адресация Flash-памяти

- •Чтение Flash-памяти

- •Стирание страничного буфера Flash-памяти

- •Загрузка страничного буфера Flash-памяти

- •Стирание страницы Flash-памяти

- •Запись страницы Flash-памяти

- •Вычисление crc для диапазона Flash-памяти

- •Стирание сектора прикладной программы

- •Стирание страницы сектора прикладной программы/загрузочного сектора

- •Запись страницы сектора прикладной программы/загрузочного сектора

- •Стирание и запись страницы сектора прикладной программы/загрузочного сектора

- •Вычисление crc в секторе прикладной программы/загрузочном секторе

- •Стирание сигнатурного кода пользователя

- •Запись сигнатурного кода пользователя

- •Чтение сигнатурного кода пользователя/калибровочных данных

- •Запись Lock-бит

- •Чтение Fuse-бит

- •Программирование eeprom

- •Адресация eeprom

- •Загрузка страничного буфера eeprom

- •Стирание страничного буфера eeprom

- •Стирание страницы epprom

- •Запись страницы eeprom

- •Стирание и запись страницы eeprom

- •Стирание eeprom

- •Чтение epprom

- •Внешнее программирование

- •Разрешение работы интерфейса внешнего программирования

- •Программирование nvm

- •Адресация nvm

- •Занятость nvm

- •Стирание всей памяти

- •Чтение nvm

- •Стирание страничного буфера Flash-памяти/eeprom

- •Загрузка страничного буфера Flash-памяти/eeprom

- •Стирание страницы Flash-памяти/eeprom

- •Запись страницы Flash-памяти/eeprom

- •Стирание и запись страницы Flash-памяти/eeprom

- •Стирание сектора прикладной программы/загрузочного сектора/eeprom

- •Проверка crc Flash-памяти

- •Запись Fuse-/Lock-бит

- •Описание регистров

- •Обзор регистров

- •Карта памяти модулей ввода-вывода

- •Краткое описание набора инструкций

- •Приложение а. Временные диаграммы модуля ebi

- •Блок sdram

- •Запись 4-битного sdram

- •Чтение 4-битного sdram

- •Регенерация sram

- •Электрические характеристики

- •Предельно-допустимые параметры*

- •Статические характеристики

- •Быстродействие

- •Характеристики ацп

- •Характеристики цап

- •Характеристики аналоговых компараторов

- •Сведения о выявленных ошибках в работе микроконтроллеров

- •Микроконтроллер aTxmega256a3

- •Версия a

- •1. Сбои в работе аналоговых компараторов при выборе в качестве входного сигнала для каждого из них напряжения Bandgap-элемента

- •2. Нелинейная и неточная работа цап при работе с внешним опорным напряжением 2.4в…vcc-0.6в

- •3. Выходной диапазон усилительного каскада ацп ограничен напряжением 2.4в

- •4. Работа супервизора питания в режиме периодических выборок, когда микроконтроллер работает в активном режиме, вносит шум на выход встроенного bandgap-элемента, использующегося в качестве ион

- •9. Супервизор питания (bod) включается в работу после активизации любого из источников сброса

- •10. Для выполнения автоматической калибровки одного из внутренних генераторов, необходимо включить в работу оба генератора и обе схемы фапч

- •11. Ограничения рабочей частоты и напряжения

Приложение а. Временные диаграммы модуля ebi

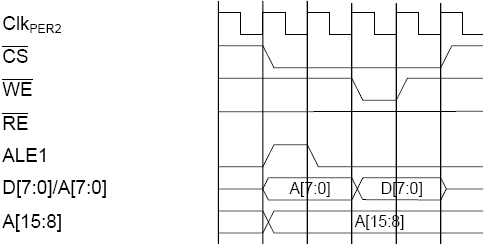

3-портовое подключение SRAM с ALE1 и CS

Рисунок 33.1. Запись (без ALE)

Рисунок 33.2. Запись (ALE)

Рисунок 33.3. Чтение (без ALE)

Рисунок 33.4. Чтение (ALE)

3-портовое подключение SRAM с ALE12 и CS

|

Рисунок 33.5. Запись (без ALE) |

Рисунок 33.6. Запись (ALE1) |

|

Рисунок 33.7. Запись (ALE1 + ALE2) |

Рисунок 33.8. Чтение (без ALE) |

|

Рисунок 33.9. Чтение (ALE1) |

Рисунок 33.10. Чтение (ALE1 + ALE2) |

4-портовое подключение SRAM с ALE2 и CS

|

Рисунок 33.11. Запись (без ALE) |

Рисунок 33.12. Запись (ALE) |

|

Рисунок 33.13. Чтение (без ALE) |

Рисунок 33.14. Чтение (ALE) |

4-портовое подключение SRAM с CS и без ALE

Рисунок 33.15. Запись

Рисунок 33.16. Чтение

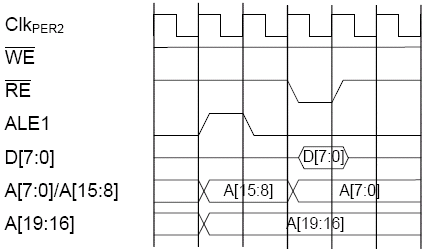

2-портовое подключение LPC памяти с ALE12 и CS

Рисунок 33.17. Запись (ALE1)

Рисунок 33.18. Запись (ALE1 + ALE2)

Рисунок 33.19. Чтение (ALE1)

Рисунок 33.20. Чтение (ALE1 + ALE2)

3-портовое подключение LPC памяти с ALE1 и CS

Рисунок 33.21. Запись

Рисунок 33.22. Чтение

2-портвоое подключение LPC памяти с ALE1 и CS

Рисунок

33.23. Запись

Рисунок

33.23. Запись Рисунок

33.24. Чтение

Рисунок

33.24. Чтение3-портовое подключение SRAM с ALE1 и без CS

Рисунок

33.25. Запись (без ALE)

Рисунок

33.25. Запись (без ALE) Рисунок

33.26. Запись (ALE)

Рисунок

33.26. Запись (ALE) Рисунок

33.27. Чтение (без ALE)

Рисунок

33.27. Чтение (без ALE) Рисунок

33.28. Чтение (ALE)

Рисунок

33.28. Чтение (ALE)4-портвоое подключение SRAM без ALE и CS

Рисунок

33.29. Запись

Рисунок

33.29. Запись Рисунок

33.30. Чтение

Рисунок

33.30. Чтение2-портовое подключение LPC памяти с ALE12 и без CS

Рисунок 33.31. Запись ALE1

Рисунок 33.32. Запись ALE1 + ALE2

Рисунок 33.33. Чтение ALE1

Рисунок 33.34. Чтение ALE1 + ALE2

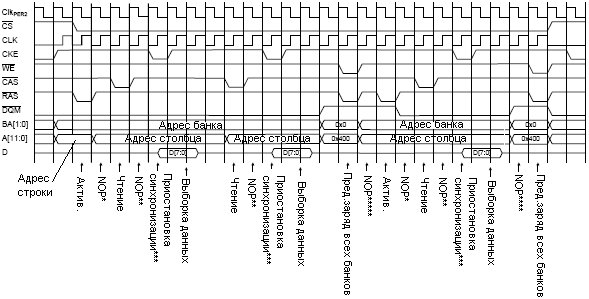

Блок sdram

Рисунок 33.35. Блок SDRAM

* Количество NOP равно RPDLY[2:0] (на рисунке RPDLY = 1)

** Авторегенерация и последующие NOP-ы повторяются 8 раз.

Количество NOP равно ROWCYCDLY[2:0] (на рисунке ROWCYCDLY = 1)

8-битная запись SDRAM

|

|

Рисунок 33.36. Одна запись

* Количество NOPравноROWCOLDLY[2:0] (на рисункеROWCOLDLY= 1) ** Количество NOP равно WRDLY[1:0] + 1 (на рисунке WRDLY = 0) *** Количество NOP равно RPDLY[1:0] (на рисунке RPDLY = 1)

|

|

|

Рисунок 33.37. Две записи подряд

* Количество NOP равно ROWCOLDLY[2:0] (на рисунке ROWCOLDLY = 1) ** Количество NOP равно WRDLY[1:0] + 1 (на рисунке WRDLY = 0) *** Количество NOP равно RPDLY[1:0] (на рисунке RPDLY = 1)

|

Рисунок 33.38. Потоковый доступ к одной странице

* Количество NOP равно ROWCOLDLY[2:0] (на рисунке ROWCOLDLY = 1)

** Количество NOP равно WRDLY[1:0] + 1 (на рисунке WRDLY = 0)

*** Количество NOP равно RPDLY[1:0] (на рисунке RPDLY = 1)

Рисунок 33.39. Потоковый доступ с пересечением границы страниц

* Количество NOP равно ROWCOLDLY[2:0] (на рисунке ROWCOLDLY = 1)

** Количество NOP равно WRDLY[1:0] + 1 (на рисунке WRDLY = 0)

*** Количество NOP равно RPDLY[1:0] (на рисунке RPDLY = 1)

8-битное чтение SDRAM

Рисунок 33.40. Одно чтение

* Количество NOP равно ROWCOLDLY[2:0] (на рисунке ROWCOLDLY = 1)

** NOP вставляется только для CAS3

*** Синхронизация приостанавливается на 1 цикл, когда EBI работает в режиме 1x и на 1 или 2 цикла, когда EBI работает в режиме 2x. Это необходимо для выборки данных по нарастающему фронту сигнала синхронизации 1x.

**** Количество NOP равно WRDLY[1:0] + 1 (на рисунке WRDLY = 0)

***** Количество NOP равно RPDLY[1:0] (на рисунке RPDLY = 1)

Рисунок 33.41. Два чтения подряд

* Количество NOP равно ROWCOLDLY[2:0] (на рисунке ROWCOLDLY = 1)

** NOP вставляется только для CAS3

*** Синхронизация приостанавливается на 1 цикл, когда EBI работает в режиме 1x и на 1 или 2 цикла, когда EBI работает в режиме 2x. Это необходимо для выборки данных по нарастающему фронту сигнала синхронизации 1x.

**** Количество NOP равно WRDLY[1:0] + 1 (на рисунке WRDLY = 0)

***** Количество NOP равно RPDLY[1:0] (на рисунке RPDLY = 1)

Рисунок 33.42. Потоковый доступ к одной странице

* Количество NOP равно ROWCOLDLY[2:0] (на рисунке ROWCOLDLY = 1)

** NOP вставляется только для CAS3

*** Синхронизация приостанавливается на 1 цикл, когда EBI работает в режиме 1x и на 1 или 2 цикла, когда EBI работает в режиме 2x. Это необходимо для выборки данных по нарастающему фронту сигнала синхронизации 1x.

**** Количество NOP равно WRDLY[1:0] + 1 (на рисунке WRDLY = 0)

***** Количество NOP равно RPDLY[1:0] (на рисунке RPDLY = 1)

Рисунок 33.43. Потоковый доступ с пересечением границы страниц

* Количество NOP равно ROWCOLDLY[2:0] (на рисунке ROWCOLDLY = 1)

** NOP вставляется только для CAS3

*** Синхронизация приостанавливается на 1 цикл, когда EBI работает в режиме 1x и на 1 или 2 цикла, когда EBI работает в режиме 2x. Это необходимо для выборки данных по нарастающему фронту сигнала синхронизации 1x.

**** Количество NOP равно WRDLY[1:0] + 1 (на рисунке WRDLY = 0)

***** Количество NOP равно RPDLY[1:0] (на рисунке RPDLY = 1)