2. Классификация машинных команд

Система команд последнего на сегодняшний день процессора Pentium IV архитектуры IA-32 содержит более 300 машинных команд. Весь набор машинных команд можно разбить на четыре группы (рис. 3).

Рис. 3. Машинные команды процессора Intel (Pentium IV)

В пределах каждой из этих больших групп, исходя из функционального назначения отдельных команд, можно провести дальнейшее разбиение на более мелкие подгруппы. Такой подход позволяет достичь нескольких целей:

оценить возможности процессора по обработке данных;

рассмотреть совокупность команд процессора архитектуры IA-32 как иерархическую и самодостаточную систему;

осмысленно изучать отдельные машинные команды в контексте остальных.

На рисунке 4 приведена классификация целочисленных машинных команд процессора архитектуры IA-32.

Рис. 4. Функциональная классификация целочисленных машинных команд

2. Формат машинных команд

Система машинных команд является важнейшей частью архитектуры компьютера, так как с их помощью производится непосредственное управление работой процессора. К примеру, система команд процессора Pentium IV содержит более 300 машинных команд. С появлением каждой новой модели процессора количество команд, как правило, возрастает, отражая архитектурные новшества данной модели по сравнению с предшествующими.

При знакомстве с системой машинных команд необходимо учитывать два аспекта – собственно набор машинных команд и правила представления этих команд на уровне процессора, то есть формат машинных команд. Процессору компьютера понятен только один язык – язык машинных команд. Машинные команды представляют собой сформированные по определенным правилам последовательности нулей и единиц. Для того чтобы заставить процессор выполнить некоторое действие, ему нужно выдать соответствующее указание в виде машинной команды, а для выполнения более сложной работы достаточно написать программу в двоичных кодах. Программирование первых компьютеров осуществлялось именно таким способом. Недостатки процесса написания программ в двоичном коде очевидны. Для облегчения процесса разработки программ был придуман язык ассемблера, как символический аналог машинного языка, а в архитектуру компьютера введен блок микропрограммного управления. Для каждой машинной команды блок микропрограммного управления содержит отдельную микропрограмму, с помощью которой действия, заданные этой командой, переводятся на язык сигналов, направляемых нужным подсистемам процессора. После этих нововведений процесс разработки программы значительно упростился. Человек пишет программу на понятном ему языке символов, специальная программа – ассемблер – переводит (транслирует) программу человека на машинный язык, а блок микропрограммного управления нужным образом интерпретирует машинные команды для процессора, процессор выполняет нужную работу.

В дальнейшем, с появлением программного обеспечения более высокого уровня, язык ассемблера не потерял своей роли, а наоборот, приобрел новые качества. В силу иерархичности программного обеспечения компьютера ассемблер стал промежуточным, связующим звеном между разнородным и разноязыким программным обеспечением более высокого уровня и процессором.

Таким образом, существует взаимно однозначное соответствие машинных команд и команд ассемблера. Понимание правил формирования машинных команд из команд ассемблера является одним из необходимых условий не только для изучения языка ассемблера, но и для понимания логики работы компьютера в целом.

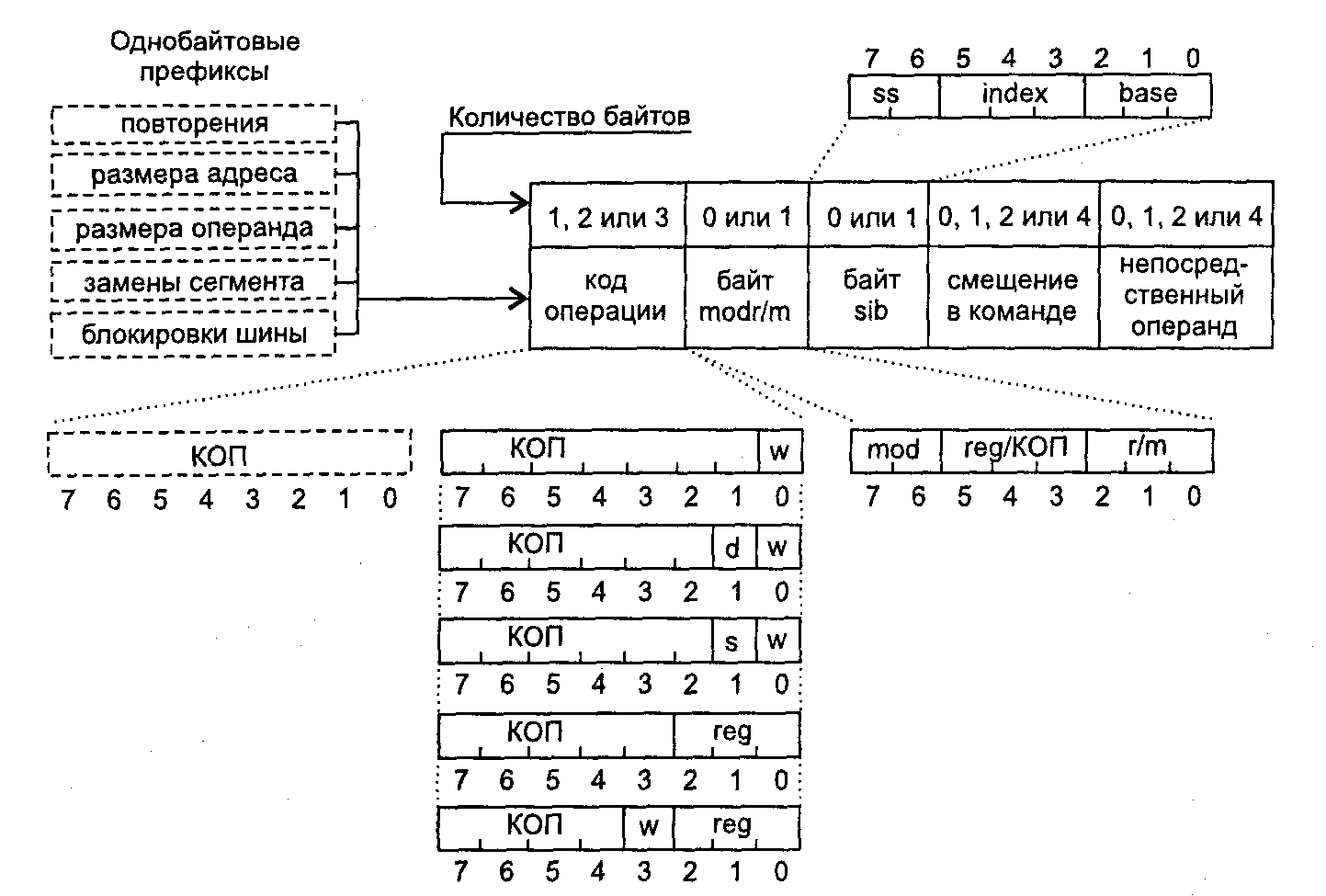

Машинная команда представляет собой закодированное по определенным правилам указание процессору на выполнение некоторой операции. Правила кодирования команд называются форматом команд. Команды процессоров архитектуры IA-32 считаются сложными. Максимальная длина машинной команды IA-32 составляет 15 байт. Реальная команда может содержать гораздо меньшее количество полей, вплоть до одного – только код операции. Приведенный на рис. 5 формат машинной команды является наиболее полным.

Рис. 5 Формат машинной команды

Каждая машинная команда всегда однозначна по отношению к производимым ею действиям на уровне аппаратуры.

Логически любая команда языка ассемблера содержит несколько элементов:

элемент, описывающий, что делать, называется кодом операции (КОП). Значение в поле кода операции определяет в блоке микропрограммного управления подпрограмму, реализующую действия для данной команды;

элементы, описывающие объекты, с которыми нужно что-то делать, являются операндами. Операнды в команде могут и не задаваться, а подразумеваться по умолчанию;

элементы, описывающие, как делать, являются типами операндов и обычно задаются неявно. Они используются транслятором ассемблера при формировании машинной команды для определения значения поля кода операции.

Эти же элементы имеет и машинная команда, но в закодированном виде. Перевод команд ассемблера в соответствующие машинные команды осуществляет специальная программа – ассемблер, которую можно также назвать транслятором (компилятором) ассемблера.

Поле префиксов

Префиксы – необязательные однобайтные элементы машинной команды. Назначение префиксов – изменить действия, выполняемые командой. Префиксы могут указываться программистом явно при написании исходного текста программы, либо их, по определенным соображениям, может вставить ассемблер. Процессор распознает префиксы по их значениям. Машинная команда может иметь до четырех префиксов одновременно. В памяти префиксы предшествуют команде. Порядок их следования при этом может быть любым.

Далее перечислены типы префиксов, которые может использовать прикладная программа:

префикс замены сегмента в явной форме указывает, какой сегментный регистр используется в данной команде для адресации стека или данных. Префикс отменяет выбор сегментного регистра по умолчанию. Префиксы замены сегмента имеют следующие значения:

2Eh — замена сегмента CS;

36h — замена сегмента SS;

3Eh — замена сегмента DS;

26h — замена сегмента ES;

64h — замена сегмента FS;

65h — замена сегмента GS;

префикс повторения используется с цепочечными командами (командами обработки строк). Этот префикс «зацикливает» команду для обработки всех элементов цепочки. Система команд поддерживает два типа префиксов: безусловные (REP — 0F3h), заставляющие цепочечную команду повторяться некоторое количество раз, и условные (REPE/REPZ - 0F3h, REPNE/REPNZ - 0F2h), которые при зацикливании проверяют некоторые флаги, и в результате проверки возможен досрочный выход из цикла;

префикс блокировки шины инициирует выдачу процессором сигнала LOCK# (значение 0F0h) для блокировки системной шины. Используется в многопроцессорных конфигурациях для обеспечения монопольного владения системной шиной. Сигнал LOCK# может формироваться лишь с определенной номенклатурой команд процессора, работающих в цикле «чтение-модификация-запись»;

префикс размера адреса (значение 67h) уточняет разрядность адреса: 16 или 32 бита. Каждой команде, в которой используется адресный операнд, ставится в соответствие разрядность адреса этого операнда. Если разрядность адреса для данной команды составляет 16 битов, это означает, что команда содержит 16-разрядное смещение и оно соответствует 16-разрядному смещению адресного операнда относительно начала некоторого сегмента. Это смещение называется эффективным адресом. Если разрядность адреса составляет 32 бита, это означает, что команда содержит 32-разрядное смещение, оно соответствует 32-разрядному смещению адресного операнда относительно начала сегмента и по его значению формируется 32-разрядное смещение в сегменте. С помощью префикса разрядности адреса можно изменить действующее по умолчанию значение разрядности адреса. Это изменение будет касаться только той команды, которой предшествует префикс;

префикс размера операнда (значение 66h) аналогичен префиксу размера адреса, но указывает на разрядность операндов (32 или 16 битов), с которыми работает команда. Значения атрибутов разрядности адреса и операндов по умолчанию устанавливаются по следующим правилам. Если команда имеет операнд в памяти, то его адрес представляет собой значение смещения относительно начала сегмента данных (если не используется префикс переопределения сегмента) и содержится в поле смещения машинной команды. Размер этого поля зависит от текущего режима адресации (атрибуты usel6 или use32 в директивах сегментации). При 16-разрядной адресации размер поля смещения в машинной команде составляет 16 битов. При 32-разрядной адресации размер поля смещения в машинной команде составляет 32 бита. Явное задание префикса размера адреса позволяет указать процессору значение, отличающееся от действующего по умолчанию. Например, если действующий размер адреса равен 16 битам, то использование перед какой-либо командой префикса 67h определит для нее (и только для нее!) размер адреса в 32 бита. И наоборот, если действующий размер адреса равен 32 бита, то указание перед командой префикса 67h определит для нее (и только для нее!) размер адреса в 16 битов. Физически это будет отражаться на размере поля смещения в данной машинной команде;

префикс размера операнда 66h позволяет сменить действующий для данной команды атрибут размера операнда. Команда, которая по умолчанию работает со словом (16 битов) или с двойным словом (32 бита), имеет атрибут размера операнда, равный 16 и 32 бита соответственно. Применение префикса размера операнда позволяет сменить действующий по умолчанию атрибут.

При работе процессора i8086 в реальном и виртуальном режимах атрибуты размера адреса и операнда по умолчанию равны 16 битов. В защищенном режиме значения этих атрибутов зависят от значения бита D дескриптора сегмента. Если D = 0, то атрибуты размера адреса и операнда равны 16 битов, если D = 1, то эти атрибуты равны 32 бита. Изменить действующие по умолчанию атрибуты адреса и размера операндов можно применением атрибутов use16 или use32 в директивах сегментации.

В реальном режиме с помощью префикса разрядности адреса можно задействовать 32-разрядную адресацию, но при этом необходимо помнить об ограниченности размера сегмента величиной 64 Кбайт. Аналогично префиксу разрядности адреса можно использовать префикс разрядности операнда в реальном режиме для работы с 32-разрядными операндами (к примеру, в арифметических командах).

В команде префиксы размера адреса и операнда могут указываться одновременно. Каким образом комбинация префиксов (указанных явно и установленных по умолчанию) влияет на атрибуты размера операнда и адреса машинной команды, показано в табл. 1. В ней отражено и то, как влияет на эти атрибуты состояние бита D дескриптора сегмента в защищенном режиме. Строки таблицы, соответствующие нулевому значению бита D, используются в реальном и виртуальном режимах работы процессора i8086.

Таблица 1. Значения атрибутов размеров операнда и адреса

|

Бит D |

66h |

67h |

Размер операнда |

Размер адреса |

|

0 |

- |

- |

16 |

16 |

|

0 |

- |

+ |

16 |

32 |

|

0 |

+ |

- |

32 |

16 |

|

0 |

+ |

+ |

32 |

32 |

|

1 |

- |

- |

32 |

32 |

|

1 |

- |

+ |

32 |

16 |

|

1 |

+ |

- |

16 |

32 |

|

1 |

+ |

+ |

16 |

16 |

Необходимо обратить внимание на то, что команды работы со стеком также имеют аналогичные атрибуты размера и адреса операнда. Атрибут размера адреса влияет на выбор регистра – указателя стека: при размере адреса 16 битов используется регистр SP, при размере адреса 32 бита используется регистр ESP. Аналогично влияет на работу команд со стеком префикс размера операнда: при использовании префикса размера операнда 16 битов операнд в стеке трактуется как 16-разрядный, при использовании префикса размера операнда 32 бита операнд в стеке трактуется как 32-разрядный.

В качестве примера префикса, который при формировании машинной команды вставляет сам ассемблер, можно привести префикс со значением 0FFh. Он называется префиксом смены алфавита и извещает о том, что поле кода операции в данной команде двухбайтовое.

Код операции

Код операции – обязательный элемент, описывающий операцию, выполняемую командой. Код операции может занимать от одного до трех байт. Для некоторых машинных команд часть битов кода операции может находиться в байте mod r/m.

Многим командам соответствует несколько кодов операций, каждый из которых определяет нюансы выполнения операции. При этом поле кода операции не имеет однозначной структуры. В зависимости от конкретных команд, не обязательно разных с точки зрения языка ассемблера, оно может иметь в своем составе от одного до трех элементов, назначение которых описано в табл. 2. Один из этих трех элементов является непосредственно кодом операции или ее частью, остальные уточняют детали операции. Такое строение поля кода операции усложняет, в частности, процесс дизассемблирования. Для определения размера и границ очередной команды необходимо полностью проанализировать ее поле кода операции.

Последующие поля машинной команды определяют характеристики и местоположение операндов, участвующих в операции, и особенности их использования.

Таблица 2. Назначение дополнительных битов поля кода операции

|

Поле |

Количество |

Назначение |

|

d |

1 |

Определяет направление передачи данных: 0 — передача данных из регистра reg в память (или регистр), адресуемую полем r/m; 1 — передача данных из памяти (или регистра), адресуемой полем г/т, в регистр reg. При наличии байта sib адрес операнда в памяти формируется с учетом содержимого этого байта |

|

s |

1 |

Задает необходимость расширения 8-разрядного непосредственного операнда до 16 или 32 бита. Старшие биты при этом заполняются значением старшего (знакового) бита исходного 8-разрядного операнда |

|

w |

1 |

Определяет размер данных, которыми оперирует команда: байт, слово, двойное слово: 0 — 8 битов; 1 — 16 битов для 16-разрядного размера операндов или 32 бита для 32-разрядного размера операндов |

|

reg |

3 |

Определяет регистр, используемый в команде. Значение поля зависит от поля w, в том числе если поле w отсутствует |

Байт режима адресации mod r/m

Байт режима адресации mod r/m, иногда называемый постбайтом, несет информацию об операндах и режиме адресации. Большинство команд процессора Intel — двухоперандные. Операнды могут находиться в памяти, а также в одном или двух регистрах. Архитектура IA-32 не допускает, чтобы оба операнда команды находились в памяти. Если операнд находится в памяти, то байт mod r/m определяет компоненты (смещение, базовый и индексный регистры), используемые для вычисления его эффективного адреса. Байт mod r/m состоит из трех полей:

поле mod (два бита) определяет способ адресации и количество байтов, занимаемых в команде адресом операнда (поле смещения в команде). Поле mod используется совместно с полем r/m, которое определяет способ модификации адреса операнда полем смещения в команде. Поле mod в комбинации с полем r/m образует 32 возможных значения, обозначающих один из восьми регистров и 24 режима адресации. К примеру, если mod = 00, то поле смещения в команде отсутствует и адрес операнда определяется содержимым базового и/или индексного регистра. Какие именно регистры потребуются для вычисления эффективного адреса, определяется значением этого байта. Если mod = 01, то поле смещения в команде присутствует, занимает один байт и модифицируется содержимым базового и/или индексного регистра. Если mod = 10, то поле смещения в команде присутствует, занимает два или четыре байта (в зависимости от значения, действующего по умолчанию или определяемого префиксом размера адреса) и модифицируется содержимым базового и/или индексного регистра. Если mod = 11, то операндов в памяти нет — они находятся в регистрах. Это же значение байта mod используется в случае, когда команда работает с непосредственным операндом;

поле reg (3 бита) определяет либо регистр, находящийся в команде на месте второго операнда, либо возможное расширение кода операции (давая в совокупности размер поля КОП в 11 битов);

поле r/m используется совместно с полем mod и определяет либо регистр, находящийся в команде на месте первого операнда (если mod = 11), либо базовые и индексные регистры, применяемые для вычисления эффективного адреса (совместно с полем смещения в команде).

В архитектуре Intel один из операндов обязательно находится в регистре, и он может быть первым или вторым. Расположение первого и второго операндов в формате команды фиксировано. Но, например, команда MOV может выполнять пересылку как из регистра в память, так и из памяти в регистр. В машинном представлении это одна и та же команда. В ее поле reg будет содержаться код регистра, а в поле r/m – код режима адресации. Эти две команды будут различаться только одним битом d, который определяет направление передачи. Если в команде участвуют два регистра, то в этом случае вступает в силу правило: поле reg определяет второй операнд, а поле r/m – первый. Если команда MOV работает с ячейкой памяти, то в исходном тексте программы могут быть следующие варианты записи этой команды:

mov abl1.ax ;пересылка содержимого ах в ячейку памяти abl1

или

mov ax.abl1 ;пересылка содержимого ячейки памяти abl1 в ах

В машинном представлении эти две команды будут выглядеть одинаково, за исключением бита d:

для команды MOV abl1.ax бит d = 0;

для команды MOV ax.abl1 бит d = 1.

Байт масштаба, индекса и базы

Байт масштаба, индекса и базы (Scale-Index-Base – sib) используется для расширения возможностей адресации операндов. На наличие байта sib в машинной команде указывает сочетание одного из значений 01 или 10 поля mod и значения поля r/m = 100. Байт sib состоит из трех элементов:

в поле масштаба (ss) размещается масштабный множитель для индексного компонента index, занимающего следующие три бита байта sib. В поле ss может содержаться значение 1, 2, 4 или 8. При вычислении эффективного адреса на это значение будет умножаться содержимое индексного регистра;

поле index позволяет хранить номер индексного регистра, содержимое которого применяется для вычисления эффективного адреса операнда;

поле base требуется для хранения номера базового регистра, содержимое которого также применяется для вычисления эффективного адреса операнда. В качестве базового и индексного регистров могут использоваться большинство регистров общего назначения.

По значению байта sib можно восстановить компоненты машинных команд, содержащие адрес операнда с учетом его масштабирования.

Одно значение базового регистра (base) в табл.10 замещено символом звездочки (*). Это означает наличие в команде адреса смещ_32 без базы, если mod равно 00, и [EBP] — в противном случае. Такой подход обеспечивает следующие режимы адресации:

смещ_32 [индекс], если mod=00;

смещ_8 [ebp][индекс], если mod=01;

смещ_32 [ebp][индекс], если mod=10.

Поля смещения и непосредственного операнда

Поле смещения в команде – это 8-, 16- или 32-разрядное целое число со знаком, представляющее собой полностью или частично (с учетом приведенных ранее рассуждений) значение эффективного адреса операнда.

Поле непосредственного операнда – необязательное поле, представляющее собой 8-, 16- или 32-разрядный непосредственный операнд. Наличие этого поля, конечно, отражается на значении байта mod r/m.