- •16. Шинная архитектура ПЭВМ.

- •Схема формирования шинного интерфейса для внешних устройств.

- •Пояснения к шинной архитектуре ПЭВМ

- •Протокол передачи данных по заданному адресу памяти по шине ISA

- •Буферизация и изменение формата данных. Назначение буферного регистра:

- •Схема наследуемой шинной архитектуры на базе шины ISA

- •Схема наследуемой шинной архитектурой

- •Внешний вид системной платы с наследуемой шинной архитектурой

- •Схема шинной архитектуры на базе чипсета Intel 815

- •Внешний вид системной платы с шинной архитектуры Intel 815

- •Схема шинной архитектуры на базе чипсета Intel 865

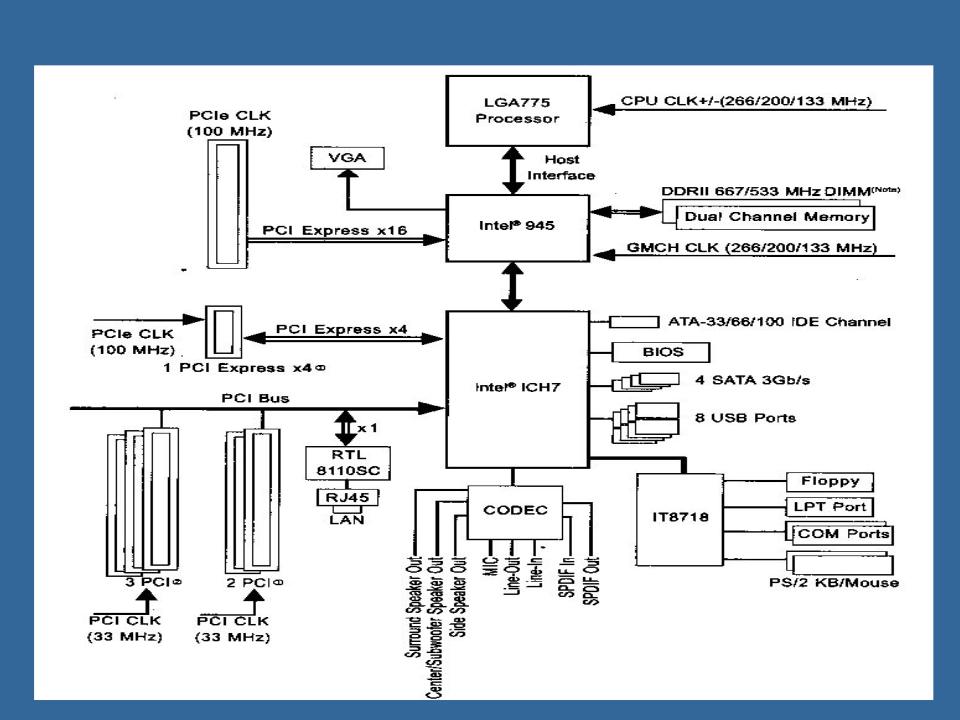

- •Схема шинной архитектуры на базе чипсета Intel 945

- •Внешний вид системной платы ASUS P7P55D DELUXE

- •Технические характеристики системной платы ASUS P7P55D DELUXE с шинной архитектурой на базе чипсета

- •Характеристика локальной шины PCI

- •PCI 64 — расширение базового стандарта PCI, появившееся в версии 2.1, удваивающее число

- •Mini PCI — новый форм-фактор PCI 2.2 для использования в основном в

- •17. Системный интервальный таймер ПЭВМ.

- •Режим 0 Прерывание терминального счета.

- •Режим 1 Ждущий мультивибратор.

- •Режим 2 Генератор частоты (периодический).

- •Режим 3 Генератор меандра (периодический).

- •Режим 4 Счетчик событий.

- •Режим 5 Счетчик событий с автозагрузкой.

- •В ПЭВМ каналы таймера имеют следующее назначение:

- •Канал 2 - генератор звука системного динамика или другое назначение пользователя (например, генерация

- •Системный таймер имеет следующие программно доступные регистры:

- •Управляющее слово имеет следующий формат:

- •18. Часы реального времени ПЭВМ, память CMOS.

- •Содержание основных регистров часов реального времени в CMOS

- •Особенности использования аппаратного прерывания IRQ8

- •Особенности использования прерывания 1Ah.

- •Особенности использования формата BCD.

- •19. Контроллер клавиатуры ПЭВМ i8049.

- •Схема прерывания от клавиатуры.

- •Процедура обработки СКЭН-кодов клавиатуры (XLAT)

- •содержание буфера клавиатуры

- •Содержание констант статуса клавиш-переключателей в ОЗУ

Схема шинной архитектуры на базе чипсета Intel 865

Схема шинной архитектуры на базе чипсета Intel 945

Внешний вид системной платы ASUS P7P55D DELUXE

с шинной архитектурой на базе чипсета Intel P55 Express

Технические характеристики системной платы ASUS P7P55D DELUXE с шинной архитектурой на базе чипсета Intel P55

Express

Поддерживаемые процессоры: INTEL CORE i5 Разъем: LGA1156

Чипсет: INTEL P55 EXPRESS

Память: 4 х DIMM. 16 ГБАЙТ max, DDRIII - 2133/1600/1333/1066 Слоты локальной шины : - З х PCI EXPRESS X16.

-2 х PCI EXPRESS X1.

-2 х PCI

Интерфейсы накопителей: - 9 х SATA,

- I х IDE UDMA.

Порты USB: |

- 6 на задней панели, |

|

- 8 дополнительно на системной плате |

Сетевой адаптер: контроллер REALTEK 8112L/8110SC 1 GB/c Звуковой адаптер: 10-канальный HDA-кодек VIA VT2020 Форм-фактор: АТХ.

Размеры: 305 х 244 мм.

Характеристика локальной шины PCI

(Peripheral component interconnect — взаимосвязь периферийных компонентов )

частота шины — 33,33 или 66,66 МГц, передача адреса и данных синхронная; разрядность шины — 32 или 64 бита, шина мультиплексированная (адрес и данные

передаются по одним и тем же линиям); пропускная способность для 32-разряднй шины на частоте 33,33 МГц — 133 Мбайт/с;

адресное пространство памяти — 32 бита (4 байта); адресное пространство портов ввода-вывода — 32 бита (4 байта);

конфигурационное адресное пространство (для одной функции) 256 байт;

напряжение 3,3 или 5 В.

Стандартные модификации шины PCI

PCI 2.0 — первая версия базового стандарта, получившая широкое распространение, Пиковая пропускная способность — 133 Мбайт/с; напряжение – 5 в.

PCI 2.1-3.0 — отличались от 2.0 возможностью одновременной работы нескольких bus- master устройств (т. н. конкурентный режим), а также появлением универсальных карт расширения, способных работать как в 5 В, так и в 3,3 В слотах (с частотой 33 и 66 МГц соответственно).

Версия 2.1 — работа с 3,3 В картами и наличие соответствующих линий питания Версия 2.2 —карты расширения имеют универсальный разъём и способны работать

практически во всех более поздних разновидностях слотов шины PCI, а также, в некоторых случаях, и в слотах 2.1;

Версия 2.3 — несовместима с картами PCI 5 В, несмотря на продолжающееся использование 32-битных слотов с 5 В-ключом. Карты расширения имеют универсальный разъём, но не способны работать в 5 В-слотах ранних версий (до 2.1 включительно);

Версия 3.0 — завершает переход на карты PCI 3,3 В, карты PCI 5 В больше не поддерживаются.

PCI 64 — расширение базового стандарта PCI, появившееся в версии 2.1, удваивающее число линий данных, и, следовательно, пропускную способность. Слот PCI64 является удлинённой версией обычного PCI-слота. Формально совместимость 32-битных карт с 64-битным слотами (при условии наличия общего поддерживаемого сигнального напряжения) полная, а совместимость 64-битной карты с 32-битным слотами является ограниченной (в любом случае произойдёт потеря производительности).

Работает на тактовой частоте 33 МГц. Пиковая пропускная способность — 266 Мбайт/с; PCI 66 — это PCI 64 работающий на тактовой частоте 66 МГц, использует 3,3 В-слоты,

карты имеют универсальный, либо 3,3 В форм-фактор. Пиковая пропускная способность — 533 Мбайт/с;

PCI 64/66 — комбинация PCI 64 и PCI 66, позволяет учетверить скорость передачи данных по сравнению с базовым стандартом PCI, и использует 64-битные 3,3 В-слоты, совместимые только с универсальными и 3,3 В 32-битными картами расширения.

Пиковая пропускная способность — 533 Мбайт/с;

PCI-X — расширение PCI64, для всех вариантов шины существуют следующие ограничения по количеству подключаемых к каждой шине устройств: 66 МГц — 4, 100 МГц — 2, 133 МГц — 1 (или 2, если одно или оба устройства не находятся на платах расширения, а уже интегрированы на одну плату вместе с контроллером), 266, 533 МГц и выше — 1;

Версия 1.0 — введено две новые рабочие частоты: 100 и 133 МГц, а также механизм раздельных транзакций для улучшения производительности при одновременной работе нескольких устройств.

Пиковая пропускная способность — 1024 Мбайт/с; Версия 2.0 — введено две новые рабочие частоты: 266 и 533 МГц, а также коррекция

ошибок чётности при передаче данных (ECC). Расширяет конфигурационное пространство PCI до 4096 байт и допускает расщепление на 4 независимых 16-битных шины, что применяется исключительно во встраиваемых и промышленных системах

Пиковая пропускная способность — 4096 Мбайт/с;

Mini PCI — новый форм-фактор PCI 2.2 для использования в основном в

ноутбуках;

Cardbus — PCMCIA форм-фактор для 32-бит, 33 МГц PCI;

CompactPCI — использует модули размера Eurocard, включаемые в PCI backplane;

PC/104-Plus — индустриальная шина, использующая сигнализацию PCI с

другим разъёмом;

PMC — PCI mezzanine card - мезонинная шина, соответствует стандарту

IEEE P1386.1;

ATCA или AdvancedTCA — шина следующего поколения для телекоммуникационной индустрии.

PCI Express (3GI0/Arapaho) — новый последовательный интерфейс, использующий программную модель PCI, однако обладающий более производительным многоуровневым механизмом передачи данных.

Реализация PCI Express |

Скорость передачи, Гбит/с |

||

с кодировкой |

без кодировки |

||

|

|||

x1 |

5 |

4 (500 Мбайт/с) |

|

x4 |

20 |

16 (2 Гбайт/с) |

|

x8 |

40 |

32 (4 Гбайт/с) |

|

x16 |

80 |

64 (8 Гбайт/с) |

|

PCI Express 2 - скорость передачи увеличена в 2 раза и более.

17. Системный интервальный таймер ПЭВМ.

Служит для задания временных интервалов и формирования сигналов с различными временными параметрами в ПЭВМ применяется программи- руемый таймер i8254

В состав таймера входят: буфер шины данных, схема управления вводом-выводом и три независимых канала, каждый из которых содержит регистр режима, схему управления каналом, буфер и 16-разрядный счетчик.

D0 … D7 |

|

|

|

|||

|

Буфер |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

обмена |

|

А0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

А1 |

|

|

|

Устройство |

||

RD |

|

|

|

управления |

||

WR |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

Регистр |

|

||

|

|

управляющего |

|

|||

|

слова порт 43h |

|

||||

|

|

|

|

|

|

|

внутренняя шина данных

CLK от часов CMOS |

|

|

|

|

|

Gate 0 |

||

|

|

|

|

|

||||

Счетчик 0 |

|

|

|

|

|

|||

|

||||||||

|

|

|

||||||

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

Out 0 |

|

Счетчик 1 |

|

|

|

|

|

Gate 1 |

||

|

|

|

||||||

|

|

|

||||||

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

Out 1 |

|

Счетчик 2 |

|

|

|

Регистр ввода-вывода |

|

||

порт 42h |

|

|

|

Регистр защелка |

Gate 2 |

||

Регистр счетчик |

n-- |

||

Out 2 |

|||

|

|

||

Режим 0 Прерывание терминального счета.

После записи управляющего слова в регистр режима канала на выходе ОUT устанавливается напряжение низкого уровня. Загрузка счетчика не изменяет это состояние. Затем начинается работа счетчика (декремент).

В момент, когда счетчик обнулится, на выходе OUT устанавливается напряжение высокого уровня и сохраняется до загрузки счетчика новым значением.

Счет возможен только при сигнале высокого уровня на входе GATE. Низкий уровень этого сигнала или ниспадающий фронт запрещают счет.

Перезагрузка счетчика во время счета приводит к остановке счета младшим байтом, загрузка старшего байта запускает новый цикл счета.

Минимально допустимое значение счетчика n равно 2.

CLK

WR |

n=5 |

n=4 |

|

|

GATE

OUT

n |

5 4 3 2 1 0 |

4 3 |

2 1 0 |

|

|

|

Режим 1 Ждущий мультивибратор.

На выходе OUT формируется отрицательный импульс длительностью t = n ●T, где n - число, загруженное в счетчик, T- период тактовых импульсов.

Низкий уровень на выходе OUT устанавливается со следующего такта после подачи на вход GATE сигнала высокого уровня.

Загрузка в счетчик нового числа не влияет на длительность текущего импульса, но учитывается при следующем запуске счетчика.

Перезапуск счетчика производится нарастающим фронтом сигнала на входе GATE (без перезагрузки счетчика).

Минимально допустимое значение счетчика n равно 1. CLK

WR |

n=4 |

n=5 |

|

|

GATE

OUT

n |

4 3 2 1 0 |

5 4 3 5 4 3 2 1 0 |

|

|