- •16. Шинная архитектура ПЭВМ.

- •Схема формирования шинного интерфейса для внешних устройств.

- •Пояснения к шинной архитектуре ПЭВМ

- •Протокол передачи данных по заданному адресу памяти по шине ISA

- •Буферизация и изменение формата данных. Назначение буферного регистра:

- •Схема наследуемой шинной архитектуры на базе шины ISA

- •Схема наследуемой шинной архитектурой

- •Внешний вид системной платы с наследуемой шинной архитектурой

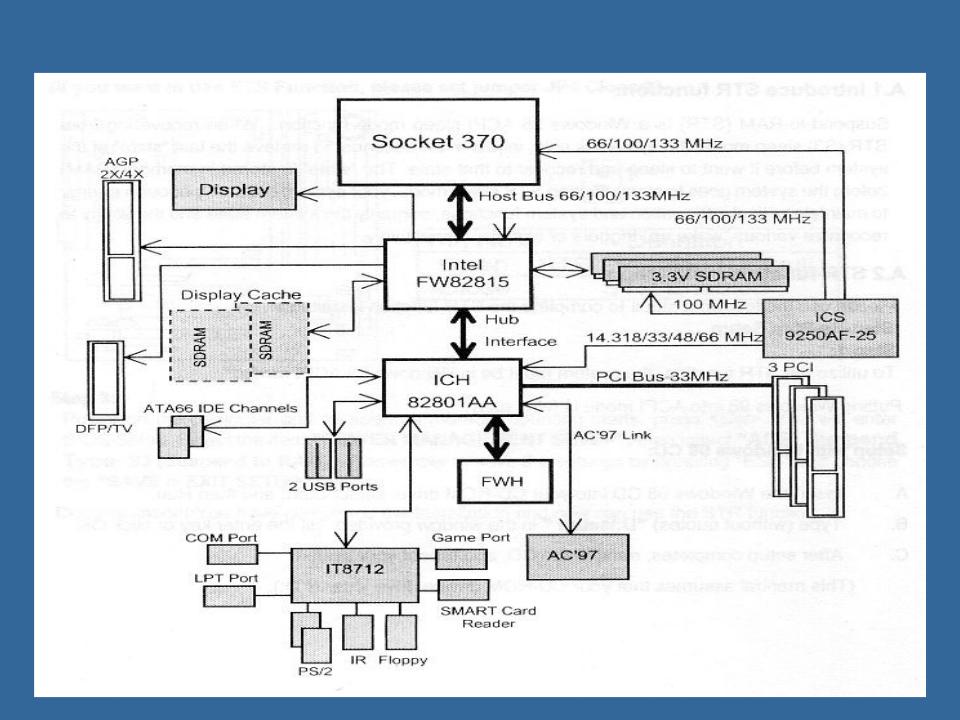

- •Схема шинной архитектуры на базе чипсета Intel 815

- •Внешний вид системной платы с шинной архитектуры Intel 815

- •Схема шинной архитектуры на базе чипсета Intel 865

- •Схема шинной архитектуры на базе чипсета Intel 945

- •Внешний вид системной платы ASUS P7P55D DELUXE

- •Технические характеристики системной платы ASUS P7P55D DELUXE с шинной архитектурой на базе чипсета

- •Характеристика локальной шины PCI

- •PCI 64 — расширение базового стандарта PCI, появившееся в версии 2.1, удваивающее число

- •Mini PCI — новый форм-фактор PCI 2.2 для использования в основном в

- •17. Системный интервальный таймер ПЭВМ.

- •Режим 0 Прерывание терминального счета.

- •Режим 1 Ждущий мультивибратор.

- •Режим 2 Генератор частоты (периодический).

- •Режим 3 Генератор меандра (периодический).

- •Режим 4 Счетчик событий.

- •Режим 5 Счетчик событий с автозагрузкой.

- •В ПЭВМ каналы таймера имеют следующее назначение:

- •Канал 2 - генератор звука системного динамика или другое назначение пользователя (например, генерация

- •Системный таймер имеет следующие программно доступные регистры:

- •Управляющее слово имеет следующий формат:

- •18. Часы реального времени ПЭВМ, память CMOS.

- •Содержание основных регистров часов реального времени в CMOS

- •Особенности использования аппаратного прерывания IRQ8

- •Особенности использования прерывания 1Ah.

- •Особенности использования формата BCD.

- •19. Контроллер клавиатуры ПЭВМ i8049.

- •Схема прерывания от клавиатуры.

- •Процедура обработки СКЭН-кодов клавиатуры (XLAT)

- •содержание буфера клавиатуры

- •Содержание констант статуса клавиш-переключателей в ОЗУ

16. Шинная архитектура ПЭВМ.

Шина (магистраль) – совокупность проводников (физических линий) данных, адреса и линий передачи сигналов управления, синхронизации и электропитания, а также протоколов обмена данными между устройствами, подключенными к шине.

Состав шины – количество линий данных определяет разрядность данных, количество линий адреса определяет адресуемое пространство памяти, количество линий сигналов управления и оповещения, частота шины, определяющая ее пропускную способность.

Шина |

Разрядность |

Тактовая частота МГц |

Пропускная |

|

бит |

|

способность Мб/с |

ISA |

16 |

8,33 |

16,6 |

PCI |

32 |

33 |

133,3 |

PCI 2.1 |

64 |

66 |

533,3 |

AGP |

32 |

66 |

266,6 |

AGP x4 |

32 |

66 х 4 |

1066,6 |

PCI e x16 |

32 |

100 x 2 |

1600 |

USB |

Mult |

200 |

12 |

Схема формирования шинного интерфейса для внешних устройств.

Любое внешнее устройство, предназначенное для установки в разъёмы расширений шины должно содержать, как минимум, 2 регистра: регистр данных (буфер данных) и регистр признаков (сигналов запроса-готовности), который связан с линией передачи сигналов.

Внешние устройства работают обычно существенно медленнее центрального процессора, т.е. асинхронно по отношению к нему, поэтому имеют в своем составе собственный генератор синхронизации.

Готовность к приёму/передачи данных должна подтверждаться соответствующими сигналами готовности. ЦП или вспомогательные схемы контроллера шины производят циклический опрос регистров состояния внешних устройств и, при приеме сигнала готовности, обеспечивают подключение к шине через дешифратор номера этого устройства.

CPU |

|

|

шина данных |

|

|

D |

D |

D |

D |

дешифратор |

OU 1 |

OU 2 |

OU 3 |

OU 4 |

|

|

|

|

|

Пояснения к шинной архитектуре ПЭВМ

Контроллер шины является устройством, связывающим центральный процессор с периферийными устройствами по сигналу запроса и сигналу готовности внешнего устройства к обмену данными с центральным процессором. При этом управление шиной передается этому внешнему устройству через дешифратор номера и это устройство становится задатчиком шины.

Задатчиками (хозяевами) шины могут выступать центральный процессор (обычная ситуация), контроллер ПДП, контроллер регенерации и некоторые платы системы расширения.

В каждом цикле обмена задатчиком всегда является только одно устройство. Контроллер ПДП захватывает магистраль (запрещает работу центрального процессора с шиной данных) на время прямой передачи информации между устройством ввода/вывода и памятью (по запросу устройства ввода/вывода).

Контроллер регенерации периодически становится задатчиком магистрали для проведения циклов регенерации системной динамической памяти через заданные интервалы времени.

Для 32-разрядных компьютеров (386DX, 486, Pentium и т.д.) обмен процессора с памятью (а иногда и с другими устройствами) осуществляется

Протокол передачи данных по заданному адресу памяти по шине ISA

Буферизация и изменение формата данных. Назначение буферного регистра:

1.Временное хранение данных для согласования скоростей устройств.

2.Подключение устройства к шине.

3.Изменение формата данных.

Схема мостового контроллера.

|

|

32 |

|

|

MUX |

|

D |

УУ |

CPU |

|

|

|

|

|

|

|

|

D |

|

|

36 |

16 |

|

|

|

|

|

|

Схема наследуемой шинной архитектуры на базе шины ISA

ЦП

ОЗУ

ВУ SCSI 7

ВУ SCSI 7

Внешнее

устройство

Внешнее

устройство

Контроллер |

клавиатура |

клавиатуры |

Контроллер ISA

CD ROM

|

Звуковой |

|

|

|

|

|

|

HDD1 |

||

|

адаптер |

|

|

|

|

|

|

Контроллер IDE |

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

HDD2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

Видео |

|

|

|

|

|

|

|||

|

|

|

|

|||||||

|

|

|

HDD3 |

|||||||

|

адаптер |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

SCSI |

|

|

|

|

|

FDD1 |

|||

|

|

|

|

|

|

|

||||

|

адаптер |

|

|

|

|

|

Контроллер FDD |

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

FDD2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

COM1 |

|

|

|

|

|

|

|

|

Контроллер COM |

|

|

|

Адаптер |

|

|

|

|

|

||||

|

|

|

|

|||||||

|

|

COM2 |

||||||||

|

внешних |

|

|

|

||||||

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

||

|

устройств |

|

|

|

|

|||||

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

LPT1 |

|

Адаптер |

|

|

|

|

|

||||

|

Контроллер LPT |

|

||||||||

|

внешних |

|

|

|

|

|

|

|

||

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|||

|

|

LPT2 |

||||||||

|

устройств |

|

|

|

|

|

||||

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

Схема наследуемой шинной архитектурой

Внешний вид системной платы с наследуемой шинной архитектурой

Схема шинной архитектуры на базе чипсета Intel 815