Архив2 / курсач docx283 / chistovik_kursach_Ilya_S

.docx

Федеральное агентство по образованию Российской Федерации

Государственное образовательное

учреждение высшего профессионального

образования

«Южно-Уральский государственный университет»

Факультет «Приборостроительный»

Кафедра «Автоматика и Управление»

«Разработка аппаратурного дешифратора адреса»

ПОЯСНИТЕЛЬНАЯ ЗАПИСКА

К КУРСОВОМУ ПРОЕКТУ

по дисциплине «Вычислительные машины, системы и сети»

ЮУрГУ–220201.2010.887.ПЗ

Нормоконтролер Руководитель работы

________ Е.В. Вставская ________ Е.В. Вставская

«____»______________

Автор работы

студент группы ПС-316

______________Семёнов И.А.

«____»______________

Работа защищена с оценкой

_________________________

«____»______________

Челябинск, 2012

Федеральное агентство по образованию Российской Федерации

Государственное образовательное учреждение высшего профессионального образования

«Южно-Уральский государственный университет»

Факультет «Приборостроительный»

Кафедра «Автоматика и Управление»

ЗАДАНИЕ

на курсовую работу студента

Семёнова Ильи Алексеевича

Группа ПС-316

Дисциплина «Вычислительные машины, системы и сети»

Тема проекта «Разработка аппаратурного дешифратора адреса»

В рамках курсовой работы необходимо разработать и схемотехнически реализовать адресный дешифратор в 16-битном адресном пространстве. В качестве исходных данных приводятся два независимых адресных диапазона и один фиксированный адрес. Выходными сигналами устройства должны быть четыре двоичных сигнала, единичный уровень которых индицирует:

1. полученный адрес соответствует любому из заданных диапазонов;

2. полученный адрес соответствует одноадресной ссылке;

3. полученный адрес соответствует первому диапазону адресов;

4. полученный адрес соответствует второму диапазону адресов;

Для выполнения работы необходимо:

1. преобразовать заданные значения адресов из 16-ричного кода в двоичный, записав диапазоны адресов в виде последовательности единиц и нулей;

2. на основе анализа изменяющихся частей адресных сегментов произвести формирование логических функций, реализующих возможность дешифрации адресных диапазонов;

3. произвести формальную минимизацию логических функций любым из доступных методов;

4. реализовать минимизированные логические функции с использованием элементной базы интегральных микросхем КМОП;

Исходные данные( вариант 22):

Адрес 1: 87C3

Диапазон 1: 69F1 – 69F9

Диапазон 2: 4100 - 4BFF

Руководитель проекта ___________ Вставская Е. В.

Студент ___________ Семёнов И.А.

АННОТАЦИЯ

Семёнов И.А. Разработка аппаратурного

дешифратора адреса: Пояснительная записка

к курсовому проекту по дисциплине «Вычислительные машины, системы и сети». – Челябинск: ЮУрГУ, 2012,

12 с, 2 ил., 3табл., библиогр. список – 3 наим., 2прил.

Данный курсовой проект состоит из двух разделов: в первом описывается механизм формирования логических функций, описывающих работу устройства; во втором рассматривается элементная база.

В приложении приводится схема реализации аппаратурного дешифратора, соответствующего исходным данным и реализованного на КМОП микросхемах 40xx серии.

ОГЛАВЛЕНИЕ

ВВЕДЕНИЕ…………………………………………………………..…..…..5

1 ФОРМИРОВАНИЕ ЛОГИЧЕСКИХ ФУНКЦИЙ, ОПИСЫВАЮЩИХ РАБОТУ УСТРОЙСТВА…………………………………………………………6

-

Преобразование систем счисления……………………….………..6

-

Функция одноадресной ссылки.…………………………..…….....6

1.3 Функция первого диапазона ……………………………………….6

1.4 Функция второго диапазона……………………………………….7

2 ВЫБОР ЭЛЕМЕНТНОЙ БАЗЫ……………………………….………….8

ЗАКЛЮЧЕНИЕ…………………………………………………………………9

БИБЛОГРАФИЧЕСКИЙ СПИСОК………………………………………….10

ПРИЛОЖЕНИЯ

ПРИЛОЖЕНИЕ A. СХЕМА РЕАЛИЗАЦИИ АППАРАТУРНОГО ДЕШИФРАТОРА………………………………….…………………………….11

ПРИЛОЖЕНИЕ Б. СПЕЦИФИКАЦИИ………………….……………..12

ВВЕДЕНИЕ

Дешифратором называется комбинационная схема, имеющая n входов и 2n выходов и преобразующая двоичный код на своих входах в унитарный код на выходах. Схемотехнически дешифратор представляет собой совокупность конъюнкторов (в дешифраторах с инверсными выходами - элементы И-НЕ ), не связанных между собой. Каждый конъюнктор (или элемент И-НЕ) вырабатывает одну из выходных функций.

Дешифраторы широко применяются в различных устройствах компьютеров. Прежде всего, они используются для выбора ячейки запоминающего устройства, к которой производится обращение для записи или считывания информации.

1 ФОРМИРОВАНИЕ ЛОГИЧЕСКИХ ФУНКЦИЙ, ОПИСЫВАЮЩИХ РАБОТУ УСТРОЙСТВА

-

Преобразование систем счисления.

Преобразование значений адреса и адресных диапазонов в двоичную систему счисления из шестнадцатеричной системы счисления:

87C316 = 1000 0111 1100 00112 адрес

69F116 = 0110 1001 1111 00012 начало первого диапазона

69F916= 0110 1001 1111 10012 конец первого диапазона

410016 = 0100 0001 0000 00002 начало второго диапазона

4BFF16 =0100 1011 1111 11112 конец второго диапазона

-

Функция одноадресной ссылки.

Функция одноадресной ссылки:

-

Функция первого диапазона.

Значения, определяющие первый диапазон:

0110 1001 1111 00012 - начало

0110 1001 1111 10012 - конец

Нетрудно заметить, что, что в первом диапазоне необходимо минимизировать только четвёртую тетраду.

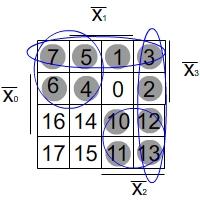

Рисунок 1-Диаграмма Вейча для четвёртой тетрады первого диапазона.

.

.

Функция первого диапазона:

.

.

1.4 Функция второго диапазона.

Значения, определяющие первый диапазон:

0100 0001 0000 0000- начало второго диапазона

0100 1011 1111 1111- конец второго диапазона

Нетрудно заметить, что, что во втором диапазоне минимизировать только вторую тетраду.

Рисунок 2-карта Вейча для второго диапазона.

.

.

Функция второго диапазона:

.

.

2 ВЫБОР ЭЛЕМЕНТНОЙ БАЗЫ

В качестве элементной базы для построения дешифратора использованы интегральные микросхем КМОП серии 40xx. Дешифратор реализован на элементах «И-НЕ», «ИЛИ-НЕ», «НЕ», так микросхемы, реализующие данные элементы помехоустойчивы и доступны.

Ниже приведены таблицы истинности используемых элементов:

|

x1 |

x2 |

y |

|

0 |

0 |

1 |

|

0 |

1 |

0 |

|

1 |

0 |

0 |

|

1 |

1 |

0 |

Таблица 1. Таблица истинности элемента «ИЛИ-НЕ»

|

x1 |

x2 |

y |

|

0 |

0 |

1 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

0 |

Таблица 2. Таблица истинности элемента «И-НЕ»

|

x |

y |

|

0 |

1 |

|

1 |

0 |

Таблица 3. Таблица истинности элемента «НЕ»

Для реализации данного устройства на интегральных микросхемах нам использованы:

4069 (6 НЕ): 3 шт;

4012 (4x2 И-НЕ): 6 шт;

4011 (2x4 И-НЕ): 2 шт;

4002 (2x4 ИЛИ-НЕ): 2 шт;

Заключение

В ходе работы были изучены принципы разработки и схемотехнической реализаций простейшего адресного дешифратора в 16-битном адресном пространстве.

-

Угрюмов Е.П. Цифровая схемотехника. – СПб.: БХВ-Санкт-Петербург, 2000.

-

Шило В.Л. Популярные цифровые микросхемы: Справочник. – М.: Металлургия, 1988.

-

Гудилин А.Е. Архитектура ЭВМ, узлы и подсистемы: Учебное пособие. –Челябинск: Изд. ЮУрГУ, 2004.