Микропроцессоры Токхайм / 8.6. АРИФМЕТИЧЕСКИЕ КОМАНДЫ МП INTEL 8080-8085

.doc8.6. АРИФМЕТИЧЕСКИЕ КОМАНДЫ МП INTEL 8080/8085

Приведем краткое описание арифметических команд МП Intel 8080/8085. Они предназначены для выполнения операций сложения, сложения с переносом, вычитания, вы-

читания

с заемом, инкрементирования,

декрементирования, десятичной коррекции

аккумулятора.

Как и в п. 8.5, группу арифметических команд будем изучать в собственном формате фирмы Intel. Эти команды оперируют с данными в памяти и регистрах. Во всех случаях, кроме указанных исключений, устанавливаются индикаторы нуля Z, знака 5, четности Р, переноса CY и вспомогательного переноса АС. Все операции вычитания проводятся с использованием дополнительного кода, устанавливают 1 в индикаторе переноса для указания переноса и сбрасывают его для указания отсутствия переноса. Как и в предыдущем случае, для понимания смысла сокращений следует обращаться к табл. 8.4.

ADD

r (Add register). Сложение содержимого регистра.

(А)<-(А) + (r). Содержимое регистра r

складывается с содержимым аккумулятора.

Результат помещается в аккумулятор.![]()

Циклов — 1; периодов T— 4; адресация — регистровая; индикаторы —Z, S, Р, CY, АС.

ADD М (Add memory). Сложение данных памяти. (A)<-(A)+((H) (L)). Содержимое памяти, адрес которой содержится в регистрах Я и L, складывается с содержимым аккумулятора. Результат помещается в аккумулятор.

![]()

Циклов — 2; периодов T— 7; адресация — косвенная регистровая; индикаторы — Z, S, Р, CY, АС.

ADI data (Add immediate). Непосредственное сложение. (A)<-(A)+(байт 2). Содержимое байта команды 2 складывается с содержимым аккумулятора. Результат помещается в аккумулятор.

![]()

Циклов — 2; периодов T— 7; адресация — непосредственная; индикаторы — Z, S, Р, CY, АС.

ADC г (Add register with carry). Прибавление содержимого регистра и переноса. (A)<-(A) + (r) + (CY). Содержимое регистра r и индикатора переноса (бит переполнения) складывается с содержимым аккумулятора. Результат помещается в аккумулятор.

![]()

Циклов — 1; периодов T — 4; адресация — регистровая; индикаторы —Z, S, Р, CY, АС.

ADC М (Add memory with carry). Прибавление содержимого памяти и переноса. (А)<-(А) + ((Н) (L))+(CY). Содержимое памяти, адресом которой является содержимое пары регистров HL, и индикатора переноса складывается с содержимым аккумулятора. Результат помещается в аккумулятор.

![]()

Циклов — 2; периодов T — 7; адресация — косвенная регистровая; индикаторы — Z, S, Р, CY, АС.

ACI data (Add immediate with carry). Непосредственное сложение с учетом переноса. (А)<-(А)+ (байт 2)+ (CY).

Содержимое

2 байт команды и индикатора переноса

складывается с содержимым аккумулятора.

Результат помещается в аккумулятор.![]()

Циклов — 2; периодов T— 7; адресация — непосредственная; индикаторы — Z, S, Р, CY, АС.

SUB

r [Subtract register). Вычитание содержимого

регистра. (А)<-(А) — (r). Содержимое

регистра r вычитается из содержимого

аккумулятора. Результат помещается в

аккумулятор.![]()

Циклов—1; периодов T— 5; адресация — регистровая; индикаторы — Z, S, Р, CY, АС.

SUB

М (Subtract memory). Вычитание содержимого

памяти. (A)<-(A) — ((H) (L)). Содержимое

памяти, адрес которой является содержимым

пары регистров HL, вычитается из

аккумулятора. Результат помещается в

аккумулятор.![]()

Циклов — 2; периодов T— 7; адресация — косвенная регистровая; индикаторы — Z, S, Р, CY,AC.

SUI data (Subtract immediate). Непосредственное вычитание. (А)<-(А) — (байт 2). Содержимое 2 байт команды вычитается из содержимого аккумулятора. Результат помещается в аккумулятор.

Циклов — 2; периодов T— 7; адресация — непосредственная; индикаторы — Z, S, Р, CY, АС.

SBB

r (Subtract register with borrow). Вычитание содержимого

регистра и переноса. (А)<-(А) — (r) — (CY).

Содержимое регистра r и индикатора CY

вычитается из содержимого аккумулятора.

Результат помещается в аккумулятор.![]()

Циклов — 1; периодов T— 4; адресация — регистровая; индикаторы—Z, S, Р, CY, АС.

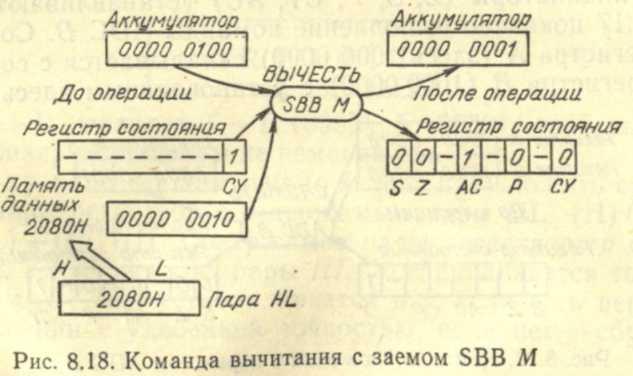

SBB М (Subtract memory with borrow). Вычитание содержимого памяти и переноса. (А)->(А) — ((Н) (L)) —

— (CY). Содержимое памяти, адресом которой является содержимое пары регистров HL, и индикатора CY вычитается из аккумулятора. Результат помещается в аккумулятор.

![]()

Циклов — 2; периодов T— 7; адресация — косвенная регистровая; индикаторы — Z, S, Р, CY, АС.

SBB data (Subtract immediate with borrow). Непосредственное вычитание данных и переноса. (А)<-(А) —

— (байт 2) — (CY). Содержимое 2 байт команды и индикатора CY вычитаются из аккумулятора. Результат помещается в аккумулятор.

Циклов — 2; периодов T— 7; адресация — непосредственная; индикаторы — Z, S, Р, CY, АС.

INR г (Increment register). Инкремент содержимого регистра, (r)<—(r) + 1. Содержимое регистра увеличивается на 1. Устанавливаются все индикаторы состояния, за исключением CY.

![]()

Циклов—1; периодов T — 4 (8085), 5 (8080); адресация — регистровая; индикаторы — Z, S, Р, АС.

INR М (Increment memory). Инкремент содержимого памяти. ((H)(L))<-((H) (L))+l. Содержимое памяти, адрес которой содержится в паре регистров HL, увеличивается на 1. Устанавливаются все индикаторы, кроме CY.

![]()

Циклов — 3; периодов T—10; адресация — косвенная регистровая; индикаторы — Z, S, Р, АС,

DCR r (Decrement regisrer). Декремент содержимого регистра, (r)<-(r) — 1. Содержимое регистра r уменьшается на 1. Устанавливаются все индикаторы, кроме СУ.

![]()

Циклов — 1; периодов T — 4 (8085), 5 (8080); индикаторы—Z, S, Р, АС.

DCR М (Decrement memory). Декремент содержимого памяти. ((H) (L))<-((H)(L)) — 1. Содержимое памяти, адрес которой содержится в паре регистров HL, уменьшается на 1. Устанавливаются все индикаторы, кроме CY.

![]()

Циклов — 3; периодов T—10; адресация — косвенная регистровая; индикаторы — Z, S, Р, АС.

INX rр (Increment register pair). Инкремент содержимого пары регистров (rh) (rl)<—(rh) (rl)+l. Содержимое пары регистров rр увеличивается на 1. Не устанавливаются никакие индикаторы.

![]()

Циклов —1; периодов T— 6 (8085), 5 (8080); адресация-регистровая, индикаторы не изменяются.

DCX

rр (Decrement register pair). Декремент пары

регистров. (rh)(rl)<-(rh)(rl)—1. Содержимое

пары регистров rр уменьшается на 1.

Не устанавливаются никакие индикаторы.![]()

Циклов —1; периодов T —6 (8085), 5 (8080); адресация-регистровая; индикаторы не изменяются.

DAD rр (Add register pair to H and L). Сложить содержимое пары регистров с содержимым пары HL. (Н)(L)<-<-(Н)(L)+(rh)(rl). Содержимое пары регистров rр складывается с содержимым пары HL. Устанавливается только индикатор CY. Он устанавливается в 1, если есть перенос при сложении с удвоенной точностью, если нет — сбрасывается.

![]()

Циклов —3; периодов T—10; адресация — регистровая; индикаторы — СУ.

DAA (Decimal adjust accumulator). Десятичная коррекция аккумулятора. 8-разрядиое число в аккумуляторе разбивается на два 4-разрядных двоично-десятичных. Далее выполняются следующие действия: 1) если значение младшей тетрады акумулятора меньше 9 или установлен индикатор AС, к содержимому аккумулятора добавляется 6; 2) если значение старшей тетрады аккумулятора больше 9 или установлен индикатор переноса СУ, 6 добавляется к значению старшей тетрады аккумулятора.

![]()

Циклов—1; периодов T—4; индикаторы —Z, S, Р, СУ, АС.

Рассмотрим команду ADC В (сложить содержимое регистра и индикатора переноса). Ее выполнение было описано выше как ADC r в формате Intel 8085, записывают ее в символической форме как (A)<-(A)+(r)+(CY).

Это означает, что содержимое r (регистр В в нашем примере) и содержимое бита переноса СУ складываются с содержимым аккумулятора (регистр А). Сумма помещается в аккумулятор. Описание Intel показывает, что это однобайтовая команда и она выполняется за один машинный цикл —четыре периода T. Способ адресации регистровый, и все индикаторы (Z, S, Р, СУ, АС) устанавливаются. На рис. 8.17 показано выполнение команды ADC В. Содержимое регистра А (здесь 1000 0000) складывается с содержимым регистра В (1000 0000) с установленным здесь в

единицу

битом переноса. Задача могла бы быть

представлена следующим образом:

Восемь МБ (0000 0001) помещаются в аккумулятор (см. рис. 8.17). Переполнение аккумулятора (наиболее значимый бит суммы) устанавливает в 1 индикатор переноса СУ после операции. Другие индикаторы сброшены в 0 после выполнения команды ADC В (рис. 8.17).

Рассмотрим теперь команду SBB М (вычесть содержимое памяти и переноса). Символическая запись фирмы Intel следующая:

(A)<-(A)-((H)(L))-(CY).

Это означает, что содержимое ячейки памяти, указанной парой HL, вычитается из содержимого аккумулятора. Бит переноса (СУ) регистра состояния также вычитается из содержимого аккумулятора, и разность помещается в аккумулятор после выполнения команды. SBB М является однобайтовой командой, которая занимает два машинных цикла — семь периодов T.

На

рис. 8.18 показано выполнение этой команды.

Регистр А содержит 0000 0100, бит переноса

—1, и ячейка памяти, указанная парой HL,

содержит 0000 0010. Рассмотрим действие

команды SBB М над данными.

Содержимое ячейки памяти, указанной парой HL, и бит переноса прежде всего складываются (0000 0010+ l) =0000 0011,

новый член берется в дополнительном коде (1111 1101) и складывается с содержимым аккумулятора, что дает 1 0000 0001. Младших 8 бит (в нашем примере 0000 0001) составляют разность, тогда как переполнение 1 инвертируется МП, сбрасывая индикатор переноса СУ в 0, т.е. переноса нет, первый член (содержимое А) был больше суммы двух других членов:

Команды сложения и вычитания с переносом не используются в случае вычитания или регулярного сложения с единственным байтом. Это особые команды, которые используют, чтобы сложить или вычесть два или несколько байт данных. Использование этих команд при реальном программировании будет показано в главе, посвященной программированию (см. гл. 9).

Упражнения

8.46. Код операции ADD С _____; по этой команде

содержимое регистра _______ складывается с содержимым

аккумулятора, и выполняется это с ________ (регистровой,

косвенной регистровой) адресацией.

8.47. Код операции команды INX Н ______ ; по этой

команде _______ (инкрементируется, декрементируется) пара ______ (ВС, HL), она _________ (устанавливает все,

не устанавливает никаких) индикаторов.

См. рис. 8.19. Код операции команды DAD В ________.

См. рис. 8.19. По команде DAD В складывается содержимое пары HL емкостью _____ (8, 16) бит с содержимым пары ________.

См. рис. 8.19. После операции DAD В пара HL содержит ________.

См. рис. 8.19. Записать значения индикаторов регистра состояния после команды DAD В.

8.52. См. рис. 8.20. Является ли содержимое аккумулятора до операции DAA правильным двоично-десятичным (двоично-десятичное 8421)?

8.53. См. рис. 8.20. Содержимое аккумулятора после операции DAA будет двоично-десятичным, десятичный эквивалент которого ______.

8.54. См. рис. 8.20. Записать состояние индикаторов в регистре состояния после операции DAA.

8.55. См. рис. 8.21. Команда SUB Е вычитает содержи- мое регистра _______ из содержимого аккумулятора.

8.56. См. рис. 8.21. После выполнения команды SUB Е содержимое аккумулятора _______.

8.57. См. рис. 8.21. Записать состояние индикаторов после выполнения команды SUB Е.

Решения

8.46. 81Н; С; регистровой. 8.47. 23Н; инкрементируется HL; не устанавливает никаких. 8.48. 09Н. 8.49. 16; ВС. 8.50. Операцией является FFFFH+0001H=10000H; ((H)(L)) =0000Н. 8.51. Устанавливается только индикатор переноса СУ, состояние других индикаторов непредсказуемо. Так как имеется переполнение или перенос в ходе операции FFFFH+0001H=10000H, (CY) = 1. 8.52. 0000 1110 не является правильным двоично-десятичным, так как 1110 не имеет двоично-десятичного эквивалента. 8.53. 0001 0100ДДК , т.е. 1410. Так как 11102 больше 9, 0110 (6ю) было прибавлено к «неправильному» двоично-десятичному, что дает 0001 0100ддк =1410. 8.54. DAA осуществляет сложение 01102 с 0000 11102, что дает 0001 0100. Тогда индикаторы устанавливаются следующим образом: (Z)=0, (S)=0, (АС) = 1, (Р) = 1 и (CY)=0. 8.55. Е. 8.56. Микропроцессор преобразует содержимое Е (0000 0010 в регистре Е) в дополнительный код (1111 1110) и производит следующую операцию:

Восемь младших бит разности (1111 1111) помещены в аккумулятор. А в десятичной форме задача записывается как 1—2=-1ю= 1111 11112 в дополнительном коде. 8.57. (S) = l, (Z)=0, (АС) = 1, (P) = l, (CY) = 1. Микропроцессор преобразует второй член (0000 0010 в регистре Е) в дополнительный код (1111 1110) и складывает:

Заметим, что переполнение (старший бит) в разности — 0, он инвертируется и помещается в CY. Индикатор СУ, установленный после вычитания, показывает, что разность является дополнительным кодом и второй член больше первого.