Микропроцессоры Токхайм / 3.8. ИСПОЛЬЗОВАНИЕ ОПЕРАТИВНОЙ И ПОСТОЯННОЙ ПАМЯТИ

.doc3.8. ИСПОЛЬЗОВАНИЕ ОПЕРАТИВНОЙ И ПОСТОЯННОЙ ПАМЯТИ

Организация ПЗУ или ОЗУ может быть наглядно представлена своеобразной таблицей истинности. Таблица 3.10 представляет собой один из возможных вариантов организации ячеек памяти. Здесь речь идет об ОЗУ 16X4 бит, о чем мы можем сделать вывод, имея 16 4-разрядных групп (эти группы составляют слова памяти). В табл. 3.10 большинство ячеек памяти пусты, за исключением слова 12, которое содержит данные 0101. В действительности пустые ячейки памяти могут содержать неизвестные сочетания нулей и единиц.

На рис. 3.25 представлена логическая схема ОЗУ 16X4 бит. В этом случае ОЗУ с объемом памяти 64 бит выполняет операцию записи поступающих данных 0101 в

ячейку памяти 1210 (11002). На входы данных поступает для записи в память слово 01012, а положение слова в ячейке с адресом 12ю определено величиной 11002 (12ю), поступающей на адресные входы.

Затем две команды управления![]() переводят

переводят

ОЗУ в состояние записи. Заметим, что

входы активизации записи![]() и

выбора кристалла

и

выбора кристалла![]() должны

быть в L-co-стоянии для того, чтобы

выполнялась операция записи. Данные

01012 помещаются тогда на место слова

памяти по адресу 12ю, как показано на

рис. 3.25. Некоторые конструкторы

вызывают активизацию памяти по входу

управления

должны

быть в L-co-стоянии для того, чтобы

выполнялась операция записи. Данные

01012 помещаются тогда на место слова

памяти по адресу 12ю, как показано на

рис. 3.25. Некоторые конструкторы

вызывают активизацию памяти по входу

управления

![]() .

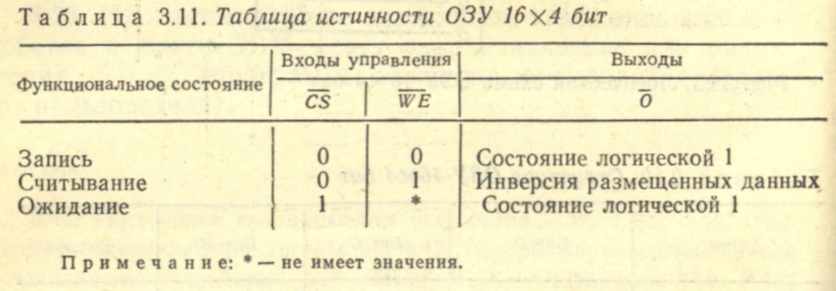

В табл. 3.11 приведена таблица истинности

такого ОЗУ с объемом памяти 64 бит.

.

В табл. 3.11 приведена таблица истинности

такого ОЗУ с объемом памяти 64 бит.

Оперативное запоминающее устройство

находится в состоянии записи, когда две

линии управления![]() находятся в L-состоянии. В ходе операции

записи 4 бит данных (D4, D3, D2, D1) загружаются

в ячейки памяти, на которую указывает

адрес, и в течение этого времени выходы

находятся в L-состоянии. В ходе операции

записи 4 бит данных (D4, D3, D2, D1) загружаются

в ячейки памяти, на которую указывает

адрес, и в течение этого времени выходы

![]() держатся в Н-состоянии. Когда входы

команд

держатся в Н-состоянии. Когда входы

команд![]() , ОЗУ находится в состоянии считывания

из него данных.

, ОЗУ находится в состоянии считывания

из него данных.

В ходе операции инверсное значение слова данных, на которое указывают адресные входы, появляется на выходах. Данные, расположенные в ОЗУ, не разрушаются операцией считывания. В состоянии ожидания все выходы переходят к Н-уровню и никакие данные не проходят через входы D.

Упражнения

3.57. Оперативное запоминающее устройство с памятью объемом 64 бит, приведенное на рис. 3.26, находится в состоянии (ожидания, записи) во время прохождения импульсов а. Следовательно, все выходы находятся в (Н-, L-состоянии).

3.58. См. рис. 3.26. Во время прохождения импульсов b, с, d и е ОЗУ находятся в состоянии (записи, чтения).

3.59. Обратиться к рис. 3.26. В течение импульсов f, g, h и i ОЗУ находятся в состоянии (записи, чтения).

Обратиться к рис. 3.26. Перечислить адреса размещения и данные, помещаемые в ОЗУ, в ходе операции записи в течение импульсов b с, d, е.

См. рис. 3.26. Перечислить адреса и данные, которые появляются на выходах ОЗУ во время операции считывания, в течение прохождения импульсов f, g, h, i.

Если ОЗУ, показанное на рис. 3.26, стало бы ПЗУ, какие входы на рисунке следует устранить?

Решения

3.57. Во время импульса а обе линии

управления![]() имеют

имеют

Н-уровень. Таблица истинности состояния

(табл. 3.11) указывает, что ОЗУ находится

в состоянии ожидания; выходы находятся,

таким образом, в Н-состоянии. 3.58. Во

время импульсов b, с, d и е обе линии

управления![]() находятся

на L-уровне. Таблица истинности состояния

(табл. 3.11) показывает, что речь идет о

состоянии записи в ОЗУ. Данные от

источника на входах D копируются в ячейку

памяти, адресованную входами А, в

течение длительности этих четырех

импульсов. 3.59. В течение длительности

этих импульсов

находятся

на L-уровне. Таблица истинности состояния

(табл. 3.11) показывает, что речь идет о

состоянии записи в ОЗУ. Данные от

источника на входах D копируются в ячейку

памяти, адресованную входами А, в

течение длительности этих четырех

импульсов. 3.59. В течение длительности

этих импульсов![]() . Таблица

. Таблица

истинности состояния (см. табл. 3.11) показывает, что речь идет о состоянии чтения. Данные, помещенные в ячейку памяти, указанную адресными входами, появятся на выходе в инверсной форме. Операция считывания не разрушает содержимого ОЗУ. 3.60. Импульс b — адрес 0000, данные 1111; импульс с — адрес 0001, данные 1110; импульс d — адрес ООП, данные 1100,1101; импульс е — адрес 0011, данные 1100. 3.61. Импульс f — адрес 0000, данные 1111, выходные инверсные данные 0000; импульс g — адрес 0001, данные 1110, выходные инверсные данные 0001; импульс h—адрес 0010, данные 1101, выходные инверсные данные 0010; импульс i — адрес ООП, нет данных в этой ячейке памяти, выходные данные неизвестны (случайны). 3.62. Входы активизации (или разрешения) записи и четыре входа данных. Постоянное запоминающее устройство программируется постоянно конструктором и не имеет состояния записи.

Дополнительные упражнения к гл. 3

Для образования последовательной логической схемы используют триггеры, для построения комбинационной логической схемы используют _____.

Начертить логическую схему элемента И с тремя входами.

Начертить логическую схему элемента ИЛИ с тремя входами.

Логическая функция может быть описана четырьмя способами: своим названием, логической схемой, таблицей истинности, функцией.

См. рис. 3.27. Привести последовательность импульсов на выходе Y, зная, что логическая схема — элемент И с двумя входами.

См. рис. 3.27. Описать последовательность импульсов на выходе Y, зная, что логическая схема — элемент НЕ-И с двумя входами.

См. рис. 3.27. Привести последовательность импульсов на выходе Y, зная, что логическая схема — элемент ИЛИ ИСКЛЮЧАЮЩЕЕ с двумя входами.

Обычно МП снабжаются четырьмя командами логических действий в своем составе команд. Какими?

Записать булеву функцию для таблицы истинности (табл. 3.12).

3.72. Начертить логическую схему, удовлетворяющую таблице истинности (табл. 3.12).

3.73. Инициализировать триггер — значит

добиться 1

на нормальном выходе, т.е.

на выходе ![]()

Сбросить или дезактивизировать триггер

— значит получить 0 на выходе ![]() _____

.

_____

.

Когда триггер работает защелкой, он используется как устройство _____ (счета, памяти).

Перечислить функциональные режимы JK-триггера на рис. 3.28 для каждого тактового импульса.

3.77. Перечислить двоичные сигналы на нормальном выходе Q JK-триггера на рис. 3.28 после каждого тактового импульса.

3.78. Трансляторы цифрового кода называются обычно _____ или _____ .

3.79. Семисегментный индикатор управляется устройством, называемым _____ в код семи сегментов.

3.80. См. рис. 3.16, в. Чтобы подать напряжение на сегмент d, вход d индикатора должен находиться в _____

(Н-, L-состоянии).

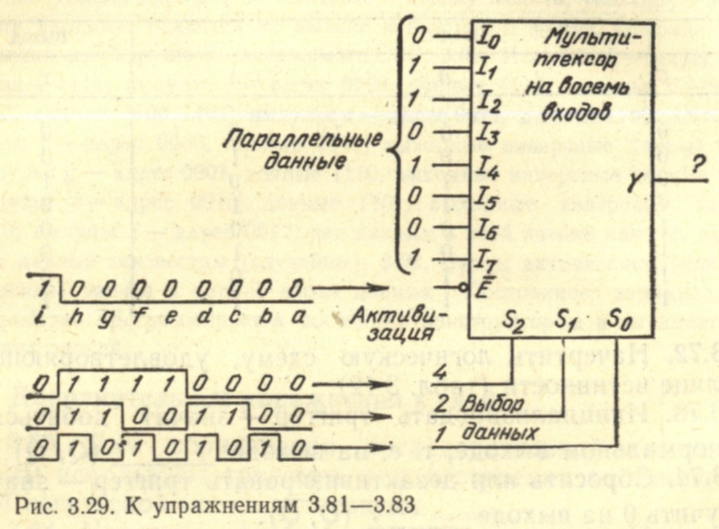

См. рис. 3.29. В течение импульсов а цепь мультиплексор-селектор данных _____ (активна, неактивна).

См. рис. 3.29. Перечислить выходы мультиплексора с восемью входами для каждой из групп импульсов (b-i).

3.83. Включенный по схеме рис. 3.29 мультиплексор функционирует в соответствии с таблицей истинности эле-мента ______ (ИЛИ, НЕ-И).

3.84. См. рис. 3.29. Логический сигнал _____ (0, 1)

передается на выход _____ мультиплексора при группе

импульсов f.

В вычислительной технике сокращение ТТЛ означает _____.

Когда элементы ТТЛ подсоединены на шину микро-ЭВМ, выходы могут находиться в _____.

Когда выход тристабильного элемента ни 0, ни 1, но элемент подсоединен на напряжение шины, он находится в состоянии высокого ______.

Какие два типа распространенных устройств памяти используются в микро-ЭВМ?

Постоянное запоминающее устройство и ____

(ППЗУ, ОЗУ) очень сходны в том смысле, что оба являются устройствами постоянной памяти.

3.90. Поместить данные в память соответствует операции _____ (записи, чтения).

3.91. Копировать данные, существующие в памяти, со- ответствует операции _____ (записи, чтения).

3.92. На практике сокращением, относящимся к памяти с произвольным доступом (оперативная память), является _____ (ППЗУ, ОЗУ).

Каковы два типа существующих ОЗУ?

В нормальных режимах использования _____ (ППЗУ, ОЗУ) могут только считывать.

3.95. Программы пользователя в микро-ЭВМ помещаются только в _______ (ОЗУ, ПЗУ).

Какая длина слова ОЗУ 256x4 бит?

Сколько слов данных содержит ОЗУ 32x8 бит?

3.98. Каков общий объем памяти (в бит) ППЗУ 512x8 бит?

3.99. См. рис. 3.30. Оперативное запоминающее устройство объемом 64 бит находится в состоянии ожидания при

импульсах _______ (d, f), и, следовательно, все выходы

находятся в ______ (Н-, L-)состоянии.

3.100. Оперативное запоминающее устройство на рис.

3.30 находится в состоянии _____ (записи, чтения) во

время импульсов а, b и с.

3.101. См. рис. 3.30. Оперативное запоминающее устройство находится в состоянии _____ (записи, чтения) во

время импульсов е, f, g и h.

3.102. См. рис. 3.30. Перечислить адреса и данные, помещенные в ОЗУ, при операции записи во время импульсов a, b и с.

См. рис. 3.30. Назвать адреса и данные на выходе ОЗУ при чтении во время импульсов е.

См. рис. 3.30. Назвать адреса и данные, выходящие из ОЗУ при чтении во время импульсов f, g и h.

Решения

3.63. Логических элементов. 3.64. См. рис.

3.31. 3.65. См. рис. 3.32. 3.66. Булевой. 3.67. Импульс

а —0; импульс b—1; импульс с—1; импульс

d — 0. 3.68. Импульс а—1; импульс b—1; импульс

с—1; импульс d — 0. 3.69. Импульс а —0;

импульс b—1; импульс с—1; импульс d —

0. 3.70. НЕ (инверсия или отрицание), И, ИЛИ,

ИЛИ ИСКЛЮЧАЮЩЕЕ. 3.71.![]() 3.72. См. рис. 3.33. 3.73. Q.

3.72. См. рис. 3.33. 3.73. Q.

3.74. Q. 3.75. Памяти. 3.76. Импульс а — сброс; импульс 6 — триггер; импульс с — триггер; импульс d — установка; импульс е — триггер; импульс f — ожидание. 3.77. Импульс а — 0; импульс b— 1; импульс с — 0; импульс d—1; импульс е — 0; импульс f — 0. 3.78. Шифраторами, дешифраторами. 3.79. Дешифратором двоично-десятичного кода. 3.80. L-состоянии. 3.81. Неактивна. 3.82. Импульс b—1; импульс с—1; импульс d—1; импульс е—1; импульс f—1; импульс g—1; импульс h— 1; импульс i — 0. 3.83. НЕ-И. 3.84. 1,7. 3.85. Транзисторно-транзисторная логика. 3.86. Трех состояниях. 3.87. Сопротивления. 3.88. ОЗУ, ПЗУ. 3.89. ППЗУ. 3.90. Записи. 3.91. Чтения. 3.92. ОЗУ. 3.93. Статические, динамические. 3.94. ППЗУ. 3.95. ОЗУ. 3.96. 4 бит. 3.97. 32. 3.98. 4096 бит. 3.99. d, Н-. 3.100. Записи. 3.101. Чтения. 3.102. Импульсы а — адрес

1111, данные 1100; импульсы b — адрес 1110, данные 1000; импульсы с — адрес 1101, данные 1011. 3.103. Адрес 0000, данные неизвестны (нет данных, записанных в этой ячейке памяти). 3.104. Импульсы f — адрес 1101, данные 1011, выходные данные (инверсные) 0100; импульсы g — адрес 1110, данные 1000, выходные данные (инверсные) 0111; импульсы h — адрес 1111, данные 1100, выходные данные (инверсные) 0011.